半导体功率器件的超结结构及其制作方法.pdf

子安****吖吖

亲,该文档总共18页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体功率器件的超结结构及其制作方法.pdf

一种半导体功率器件的超结结构包括N型衬底、形成于N型衬底上的N型外延、形成于N型外延表面的第一沟槽与第二沟槽、位于N型外延中的第一沟槽下方的第三沟槽、位于N型外延中的第四沟槽、位于第三沟槽与第四沟槽表面的P型掺杂区、位于第三、第四沟槽中且P型掺杂区表面及第一及第二沟槽侧壁的多晶硅、形成于N型外延上及第一及第二沟槽中的P型外延、形成于第一与第二沟槽之间的N型外延表面的N型外延层、形成于P型外延表面且邻近N型外延层两侧的第一、第二N型注入区、形成于N型外延层上的氧化硅与多晶硅层、形成于P型外延层、N型注入区与

一种超结功率器件及其制作方法.pdf

本发明公开了一种超结功率器件及其制作方法,其中制作方法包括:在衬底上形成外延层,并对所述外延层进行刻蚀形成沟槽;在所述外延层上方及所述沟槽内形成氧化层和多晶硅;在所述沟槽内填充介质材料形成介质层,去除所述外延层上方的氧化层、多晶硅以及沟槽内的介质层,保留所述沟槽内的氧化层、多晶硅和介质层,使得沟槽内保留的介质层与氧化层和多晶硅高度相同。采用对外延层进行刻蚀形成沟槽的方式,并在沟槽内形成氧化层和多晶硅,然后在沟槽中填充介质材料,形成P型区域,与现有制作方法相比,本发明不需要重复进行外延生长工艺来制作外延层,

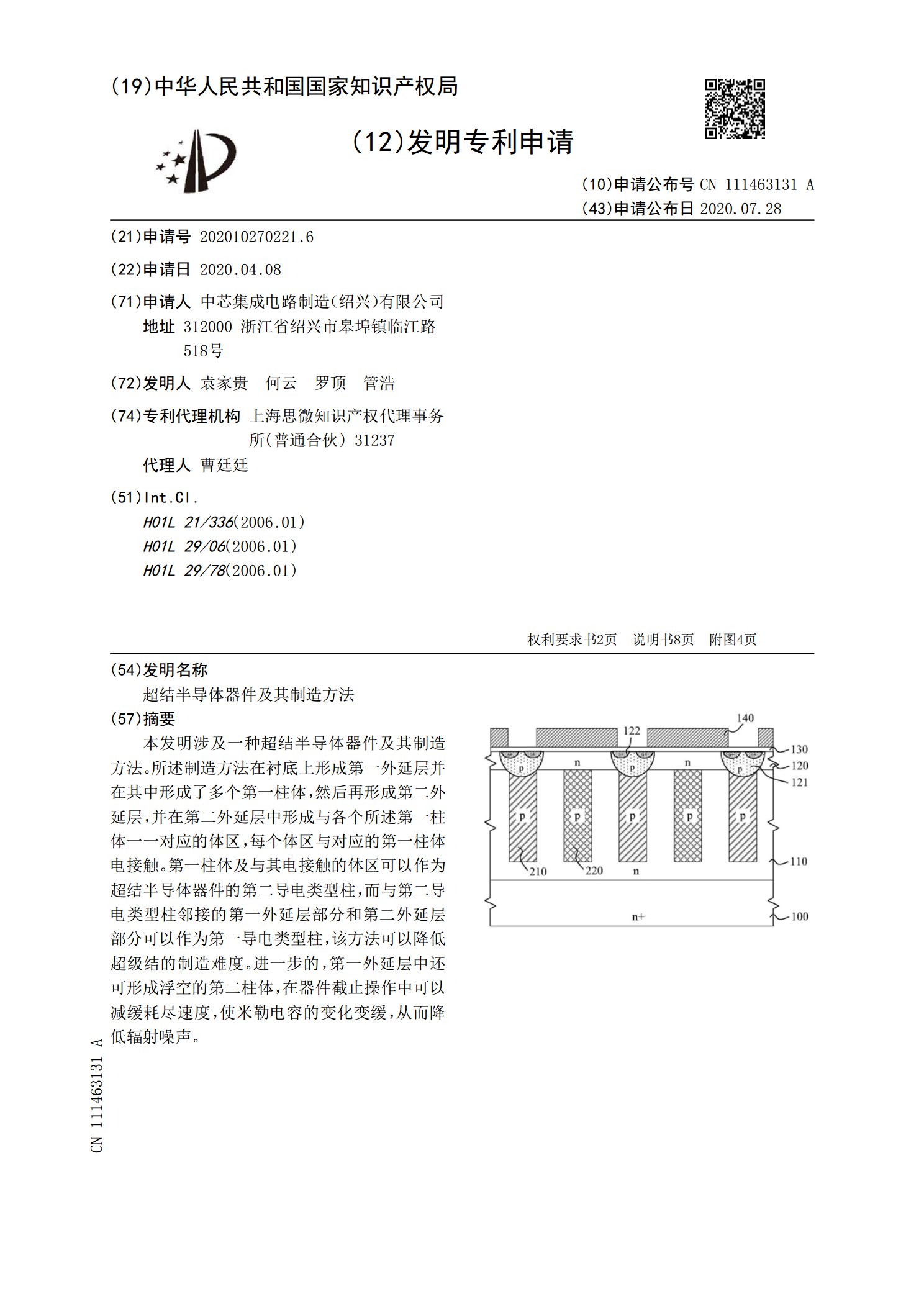

超结半导体器件及其制造方法.pdf

本发明涉及一种超结半导体器件及其制造方法。所述制造方法在衬底上形成第一外延层并在其中形成了多个第一柱体,然后再形成第二外延层,并在第二外延层中形成与各个所述第一柱体一一对应的体区,每个体区与对应的第一柱体电接触。第一柱体及与其电接触的体区可以作为超结半导体器件的第二导电类型柱,而与第二导电类型柱邻接的第一外延层部分和第二外延层部分可以作为第一导电类型柱,该方法可以降低超级结的制造难度。进一步的,第一外延层中还可形成浮空的第二柱体,在器件截止操作中可以减缓耗尽速度,使米勒电容的变化变缓,从而降低辐射噪声。

超结功率器件及其制备方法.pdf

本发明提供一种超结功率器件及其制备方法,在制备超结功率器件时,可在形成第一导电类型外延层之后通过添加超结掩膜版、在形成第二导电类型阱区之前或之后直接通过阱区掩膜版,以及在形成接触结构之前或之后直接通过接触掩膜版,即可在第一导电类型外延层内注入第二导电类型杂质,以依次形成第二导电类型浮岛及第二导电类型柱,该制备工艺无需进行多次外延工艺,且无需进行深沟道刻蚀,因此制备工艺简单、成本低,且成品率及可靠性较高。本发明的超结功率器件同时具有第二导电类型浮岛及第二导电类型柱,在断路状态,可提高功率器件的击穿电压,降低

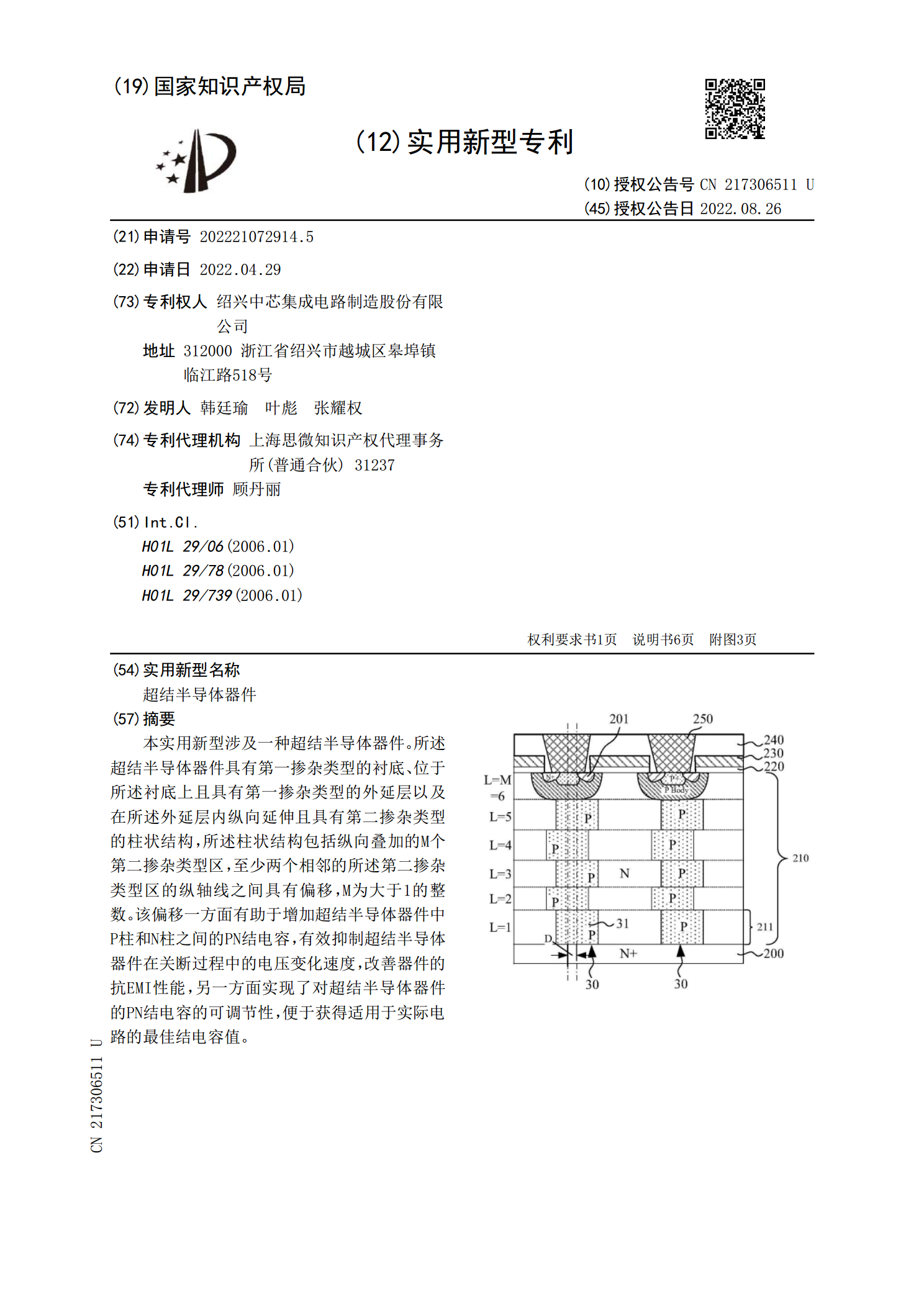

超结半导体器件.pdf

本实用新型涉及一种超结半导体器件。所述超结半导体器件具有第一掺杂类型的衬底、位于所述衬底上且具有第一掺杂类型的外延层以及在所述外延层内纵向延伸且具有第二掺杂类型的柱状结构,所述柱状结构包括纵向叠加的M个第二掺杂类型区,至少两个相邻的所述第二掺杂类型区的纵轴线之间具有偏移,M为大于1的整数。该偏移一方面有助于增加超结半导体器件中P柱和N柱之间的PN结电容,有效抑制超结半导体器件在关断过程中的电压变化速度,改善器件的抗EMI性能,另一方面实现了对超结半导体器件的PN结电容的可调节性,便于获得适用于实际电路的最