超结半导体器件.pdf

春景****23

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

超结半导体器件.pdf

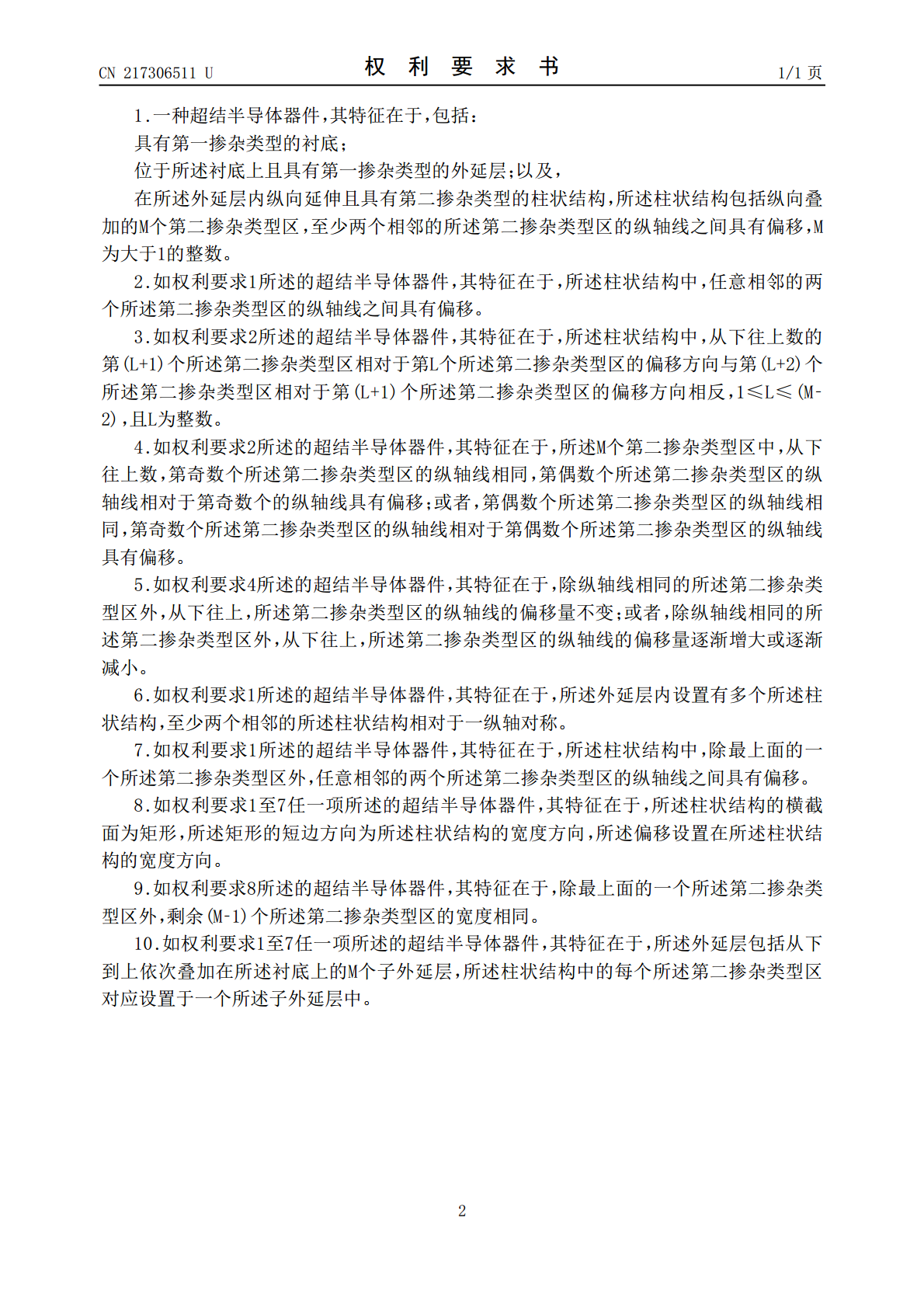

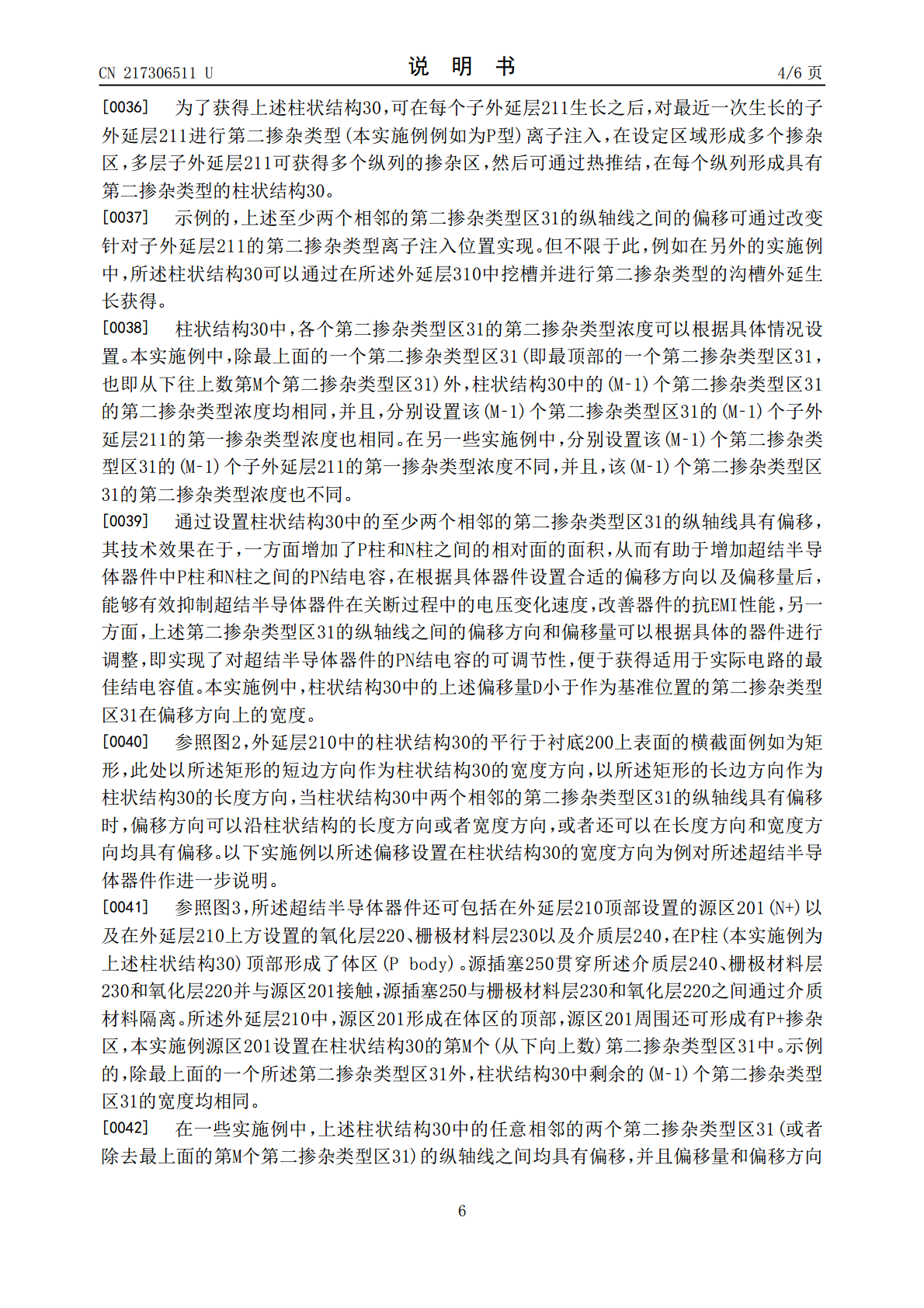

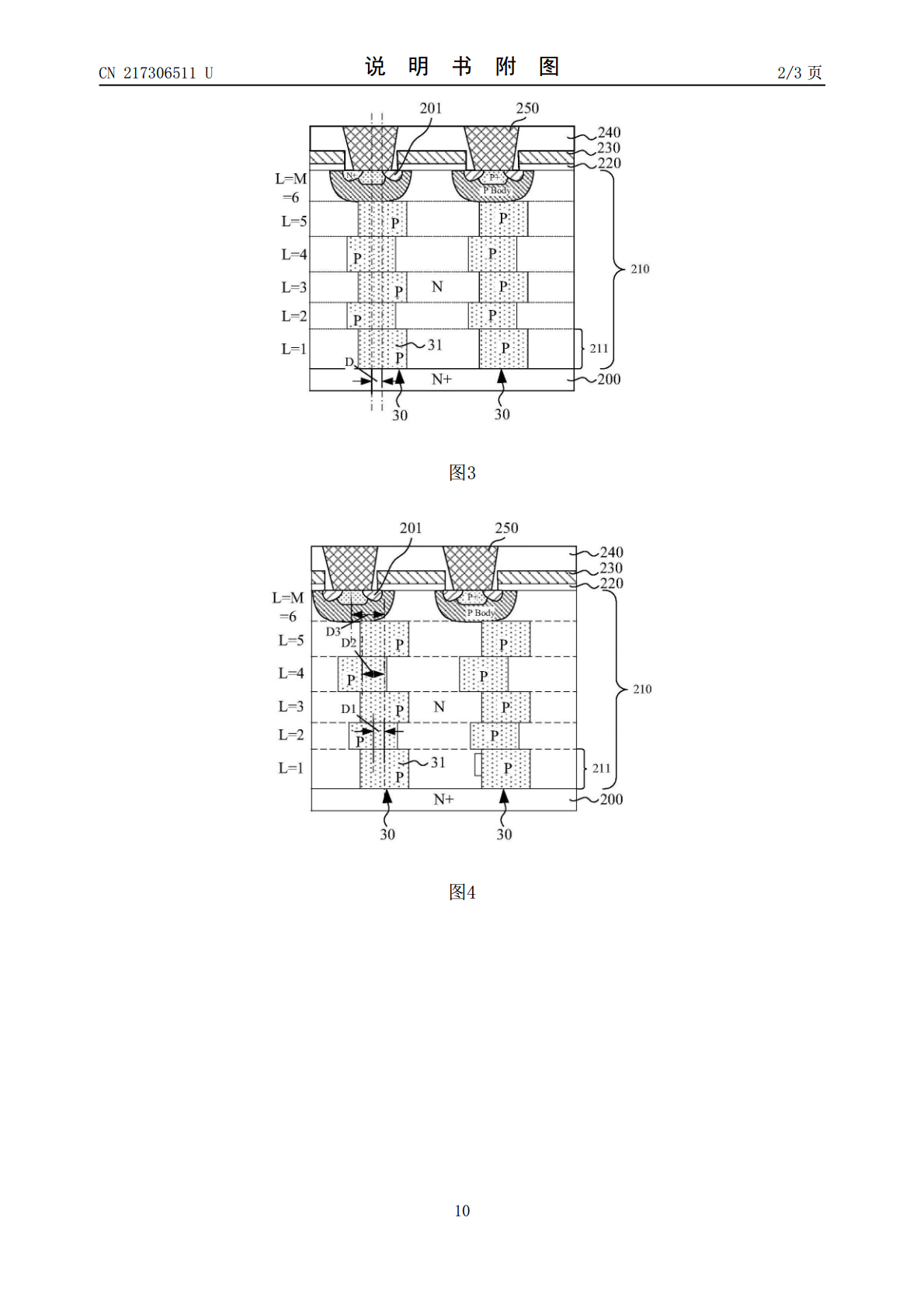

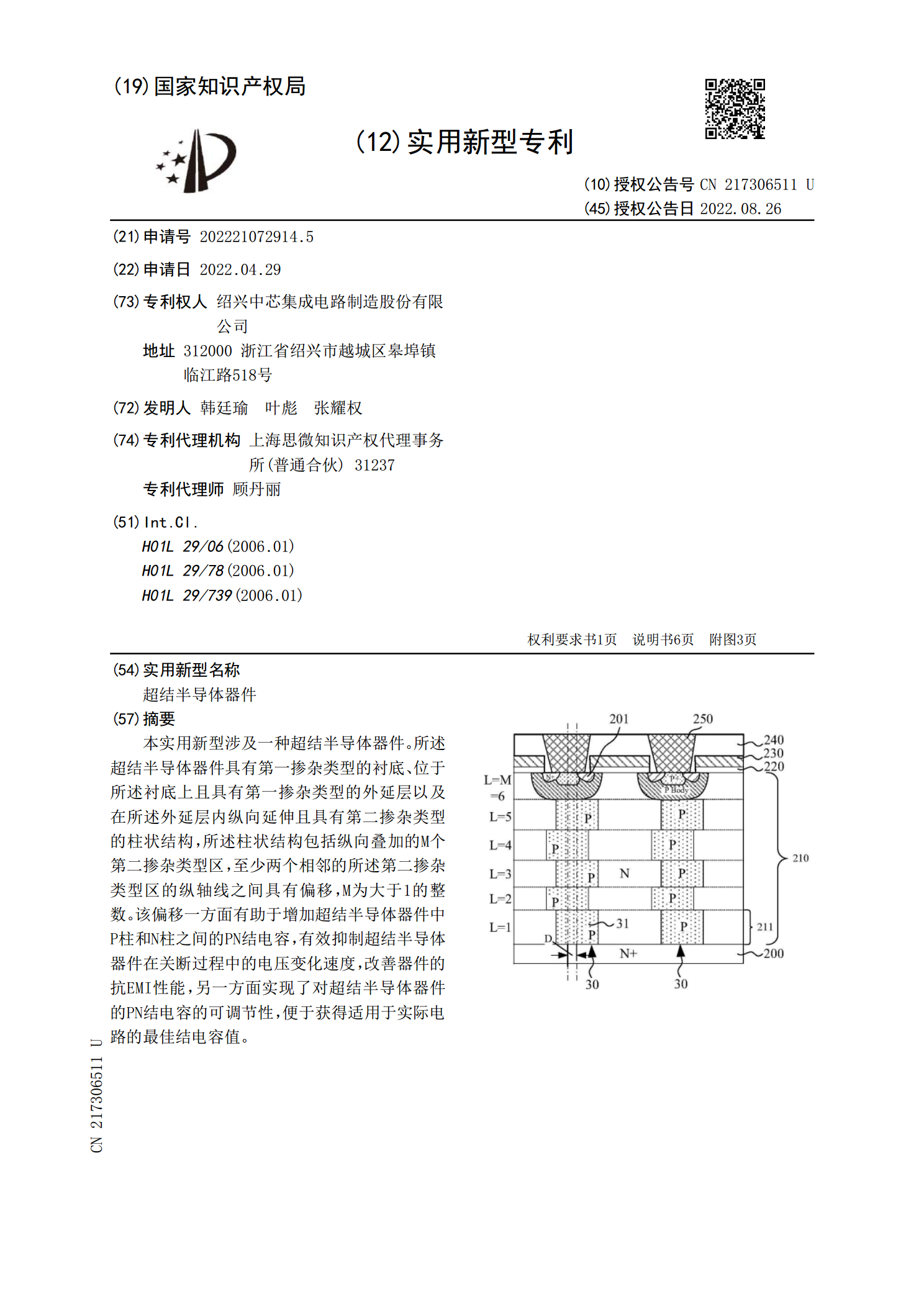

本实用新型涉及一种超结半导体器件。所述超结半导体器件具有第一掺杂类型的衬底、位于所述衬底上且具有第一掺杂类型的外延层以及在所述外延层内纵向延伸且具有第二掺杂类型的柱状结构,所述柱状结构包括纵向叠加的M个第二掺杂类型区,至少两个相邻的所述第二掺杂类型区的纵轴线之间具有偏移,M为大于1的整数。该偏移一方面有助于增加超结半导体器件中P柱和N柱之间的PN结电容,有效抑制超结半导体器件在关断过程中的电压变化速度,改善器件的抗EMI性能,另一方面实现了对超结半导体器件的PN结电容的可调节性,便于获得适用于实际电路的最

超结半导体器件及其制造方法.pdf

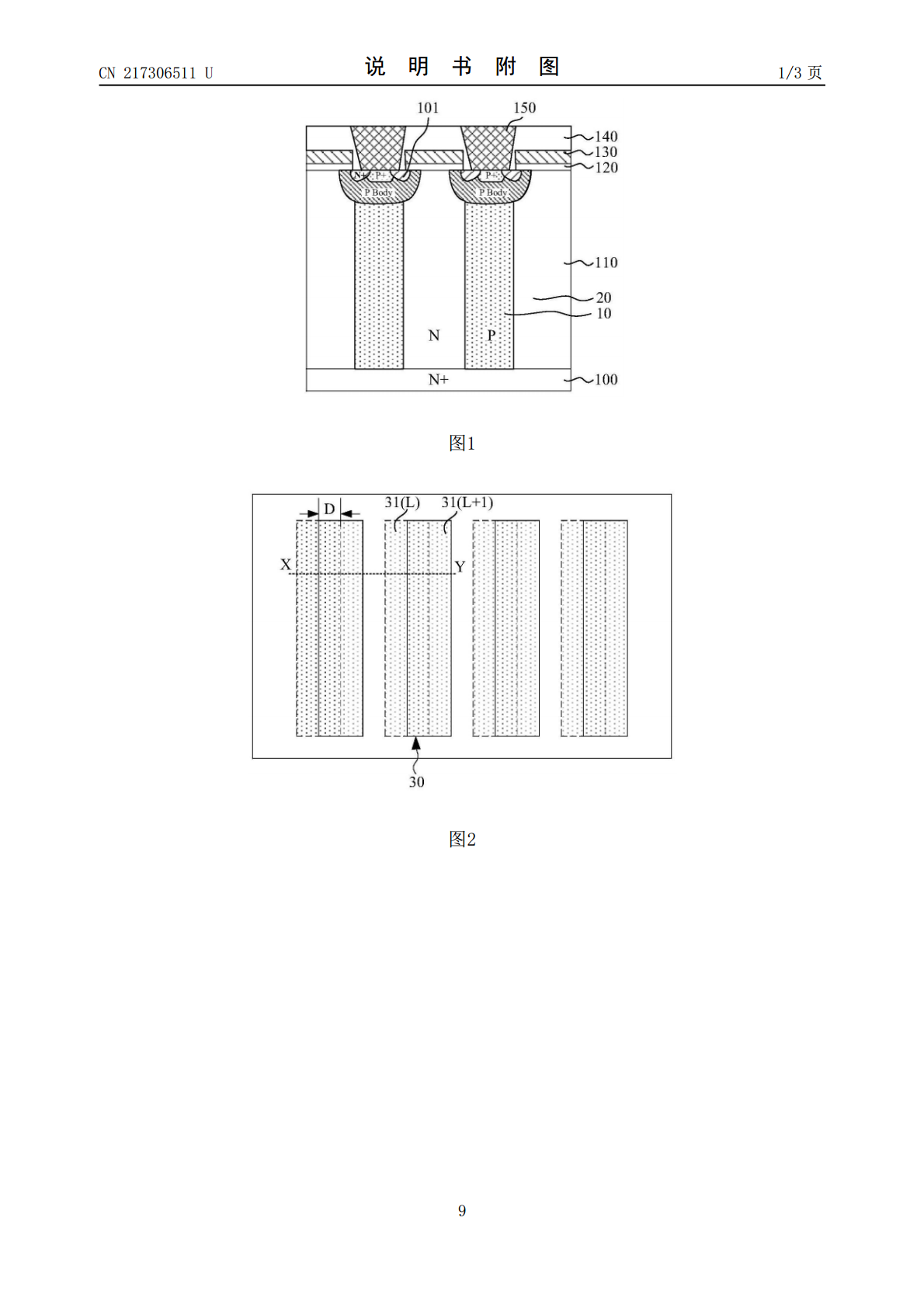

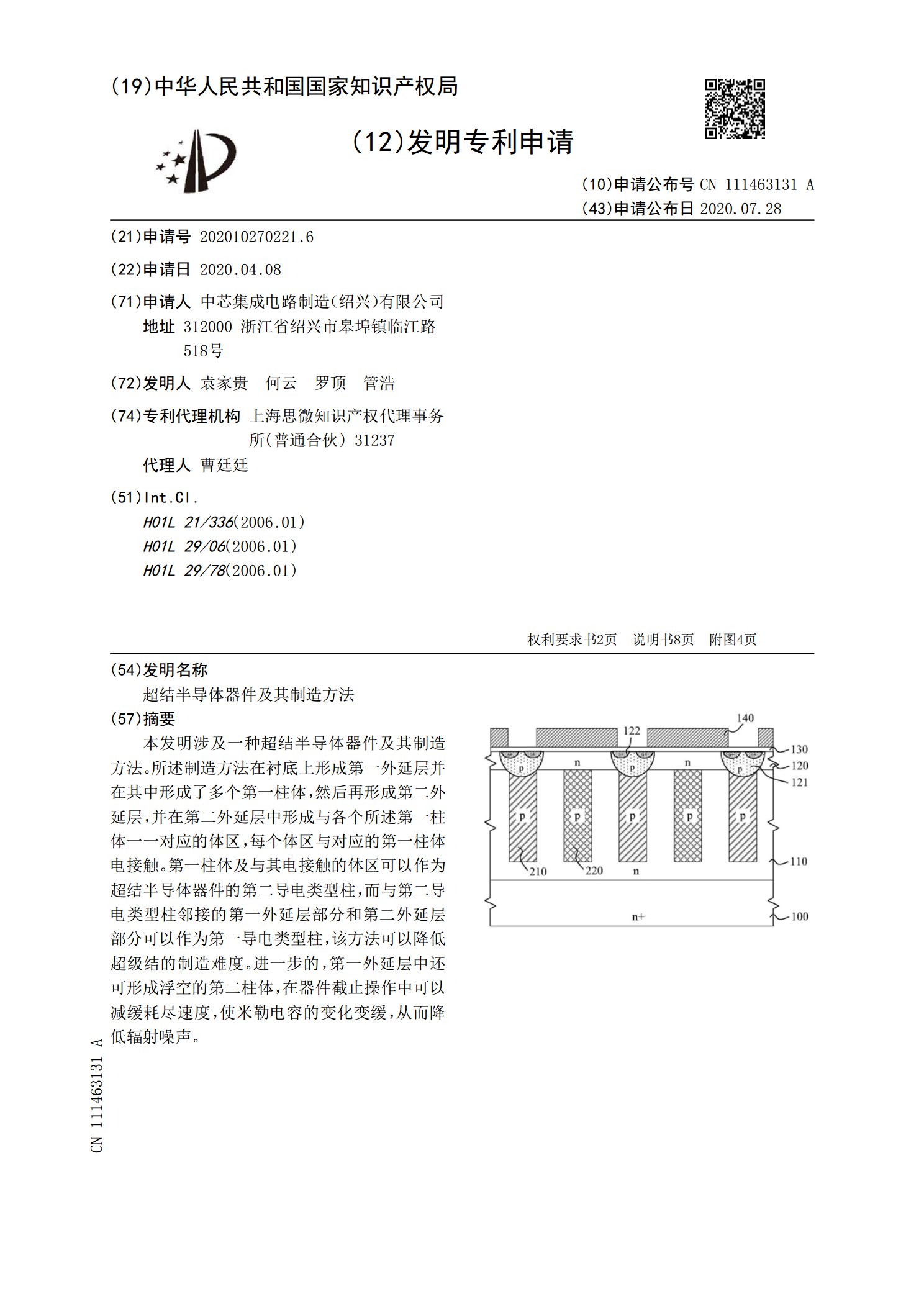

本发明涉及一种超结半导体器件及其制造方法。所述制造方法在衬底上形成第一外延层并在其中形成了多个第一柱体,然后再形成第二外延层,并在第二外延层中形成与各个所述第一柱体一一对应的体区,每个体区与对应的第一柱体电接触。第一柱体及与其电接触的体区可以作为超结半导体器件的第二导电类型柱,而与第二导电类型柱邻接的第一外延层部分和第二外延层部分可以作为第一导电类型柱,该方法可以降低超级结的制造难度。进一步的,第一外延层中还可形成浮空的第二柱体,在器件截止操作中可以减缓耗尽速度,使米勒电容的变化变缓,从而降低辐射噪声。

超结半导体器件及其形成方法.pdf

本发明涉及一种超结半导体器件及其形成方法。该形成方法包括在具有第一掺杂类型的衬底上多次执行外延生长工艺,形成叠加设置的多个子外延层,在一次外延生长工艺结束而下一次外延生长工艺开始前,执行第一掺杂类型离子注入在顶部子外延层中形成位于所述顶部子外延层上部的界面补偿区,所述界面补偿区与多个子外延层之间的界面较近,可以改善多个子外延层中层与层之间的阻抗高于目标值且稳定性差的问题,有助于N柱和P柱的电荷平衡,提升器件耐压性能和成品率。本发明提供的超结半导体器件采用上述形成方法形成,其中多个子外延层中层与层之间的阻抗

超结器件.pdf

本申请公开了一种超结器件。所述超结器件包括:半导体衬底;以及位于所述半导体衬底的第一表面上的超结结构,所述超结结构包括多个第一半导体柱和多个第二半导体柱,其中,所述超结器件包括元胞区和围绕所述元胞区的终端区,所述超结结构的一部分位于所述元胞区中,另一部分位于所述终端区中,所述超结器件还包括位于所述终端区中并且围绕所述元胞区的保护环,所述保护环包括分段延伸的多个掺杂区,以及将所述多个掺杂区连接成连续环的第一组半导体柱的顶端部分。该超结器件的保护环中的第一组半导体柱的顶端部分未掺杂,因此可以改善保护环的杂质分

半导体器件之pn结器件.pptx

pn结二极管pn结静态特性回顾理想pn结正偏电流-电压特性pn结的小信号模型空间电荷区中的产生与复合电流(非理想特性)pn结二极管的击穿特性pn结二极管的开关特性同质pn结性质回顾同一均匀半导体冶金结空间电荷区内建电场耗尽区零偏pn结pn结的零偏、反偏和正偏零偏状态下内建电势差形成的势垒维持着p区和n区内载流子的平衡内建电场造成的漂移电流和扩散电流相平衡pn结两端加正向偏压Va后,Va基本上全降落在耗尽区的势垒上;由于耗尽区中载流子浓度很小,与中性P区和N区的体电阻相比耗尽区电阻很大。势垒高度由平衡时的e