高导电低阻值的芯片封装结构及其制备方法.pdf

睿达****的的

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

高导电低阻值的芯片封装结构及其制备方法.pdf

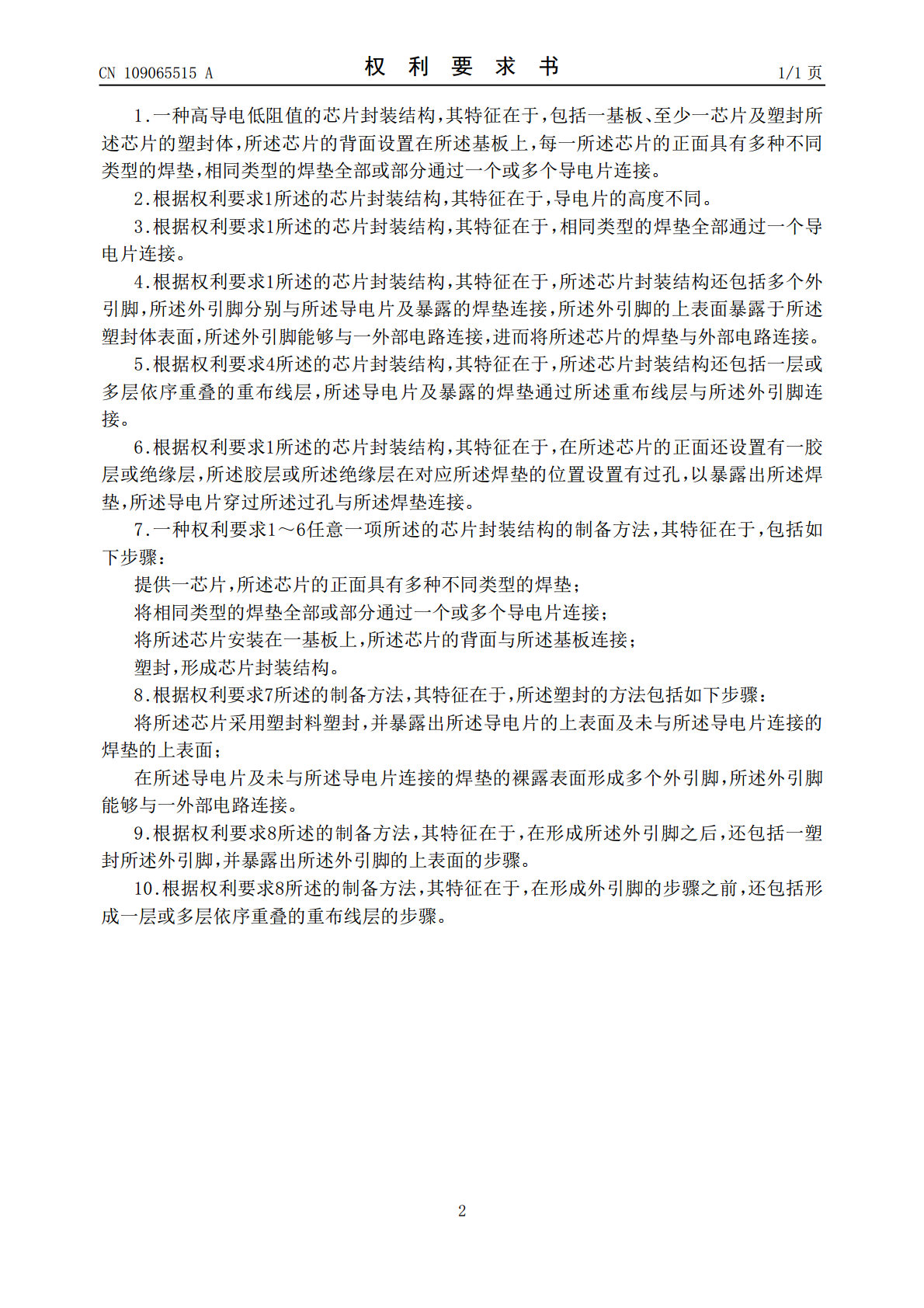

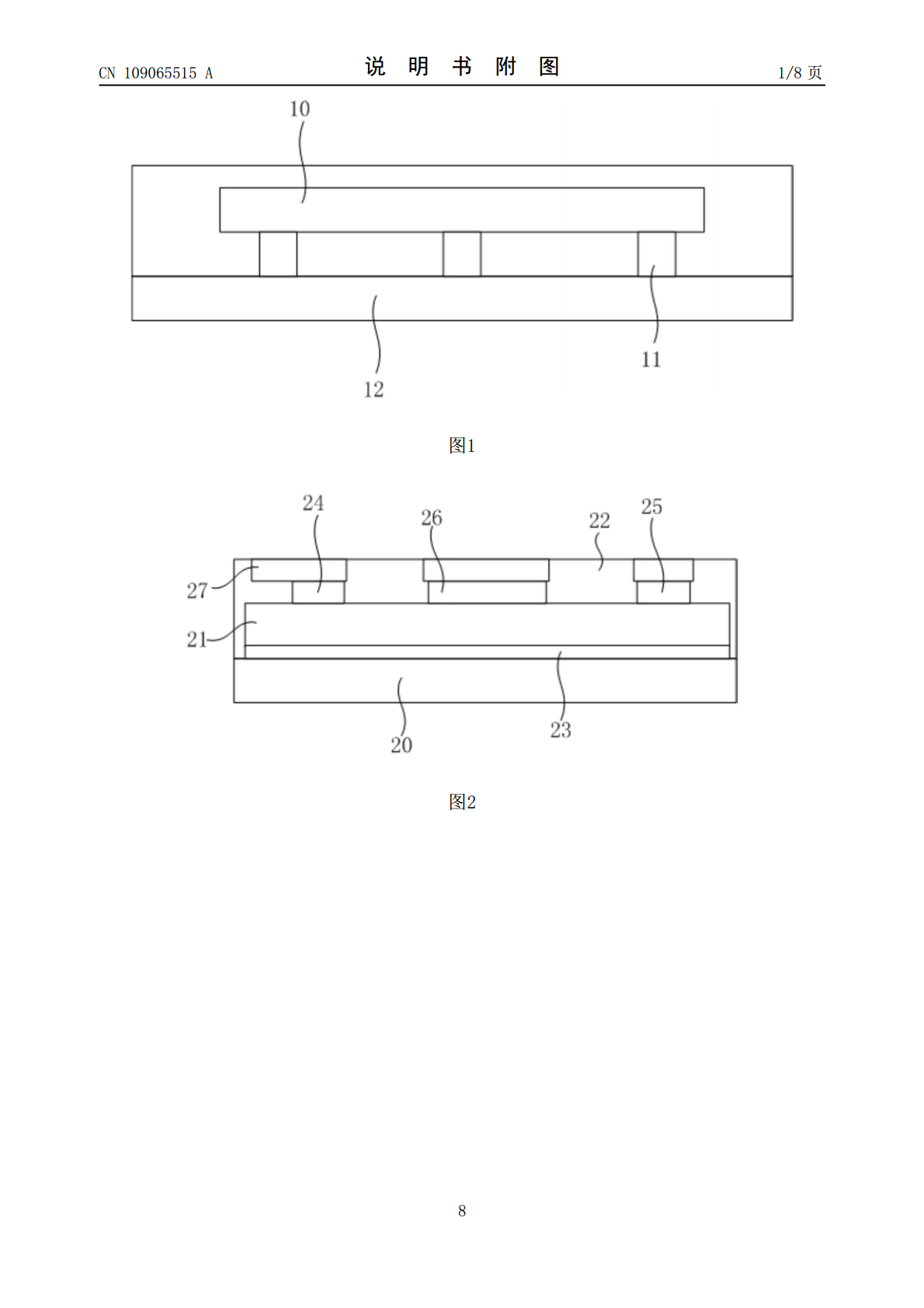

本发明提供一种高导电低阻值的芯片封装结构及其制备方法,所述芯片封装结构包括一基板、至少一芯片及塑封所述芯片的塑封体,所述芯片的背面设置在所述基板上,每一所述芯片的正面具有多种不同类型的焊垫,相同类型的焊垫全部或部分通过一个或多个导电片连接。本发明的优点在于,本发明芯片封装结构将芯片的相同类型的焊垫通过一导电片连接,形成大面积的导电层,导电性能好,比传统的晶圆级封装在高电流时的电阻值更低;且可以避免倒装工艺中电镀小的金属凸块时出现金属凸块的间距不足或者高度偏小的风险;对导电片的高度均一性无要求,只需满足最小

芯片封装结构及其制备方法.pdf

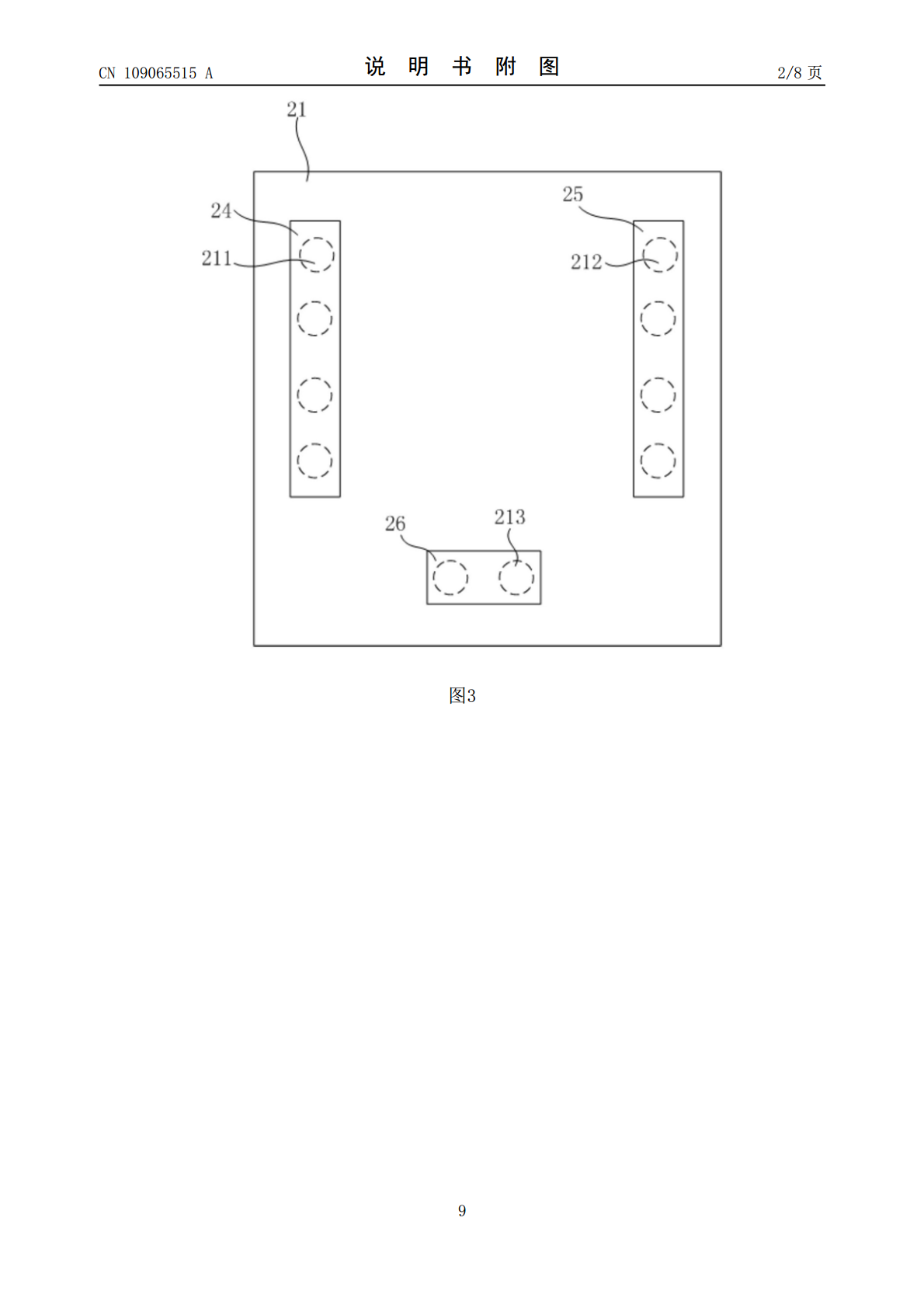

本发明提供一种芯片封装结构及其制备方法,芯片封装结构包括:一引线框架,所述引线框架具有至少一基岛及至少一引脚;至少一芯片,设置在所述基岛上,每一芯片的背面与所述基岛的承载面连接,每一芯片的有源面上设置有多个与芯片的焊垫连接的导电凸块;至少一导电柱,设置在所述引脚上表面;至少一重布线层,分别与所述导电凸块及所述导电柱连接,以将所述芯片的焊垫连接至所述引脚。本发明的优点在于,本发明芯片封装结构通过基岛散热,所述芯片通过导电凸块、重布线层及导电柱连接与引脚,具有高导热性能及良好的导电性能,适应大功率和高导热高导

芯片封装结构及其制备方法.pdf

本发明提供一种芯片封装结构及其制备方法,其中芯片封装结构包括:散热盖、加固片、芯片、辅助电子器件和基板;加固片、芯片和辅助电子器件固定设置于基板的同一表面上,散热盖位于加固片背离基板的一侧,散热盖与加固片固定连接,散热盖与芯片焊接,基板与加固片和散热盖合围成一安装腔,芯片位于安装腔内;加固片朝向基板的表面开设有容纳腔,辅助电子器件位于容纳腔内。本发明能够提高芯片封装的良率。

芯片封装结构及其制备方法.pdf

本发明涉及一种芯片封装结构及其制备方法。该芯片封装结构的制备方法,包括:提供基板;于基板表面形成网状排布的金属线路,各金属线路的端部形成有间隔排布的第一沟槽,第一沟槽的延伸方向与金属线路的延伸方向相同,且第一沟槽具有第一深度;键合芯片于金属线路的表面;形成封装层,覆盖芯片和金属线路,得到第一中间封装结构;对第一中间封装结构执行切割工艺,于金属线路的端部形成具有第二深度的第二沟槽,第二深度小于第一深度。上述芯片封装结构的制备方法,可以在执行切割工艺后,在芯片封装结构中的金属线路端部仍保留一定深度的沟槽,便于

芯片封装结构及其制备方法.pdf

本发明涉及芯片封装技术领域,具体公开了一种芯片封装结构及其制备方法。芯片封装结构包括:底板,底板上设置有接地端点;至少一个电子元件,电子元件设置于底板;塑封体,塑封体覆盖至少部分设置于电子元件上;屏蔽结构,屏蔽结构设置于塑封体的外围;以及接地金属线,接地金属线至少部分穿过所述塑封体并连接于接地端点与屏蔽结构之间。本发明中的芯片封装结构采用接地金属线来连接底板上的接地端点和屏蔽结构,在实际加工的过程中,无需采用高精密的镭射机台来进行镭射打孔,不存在盲孔打孔深度不好控制的问题,接地金属线可以采用键合机来制备形