液晶显示器的阵列基板及其制造方法.pdf

书生****22

亲,该文档总共38页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

液晶显示器的阵列基板及其制造方法.pdf

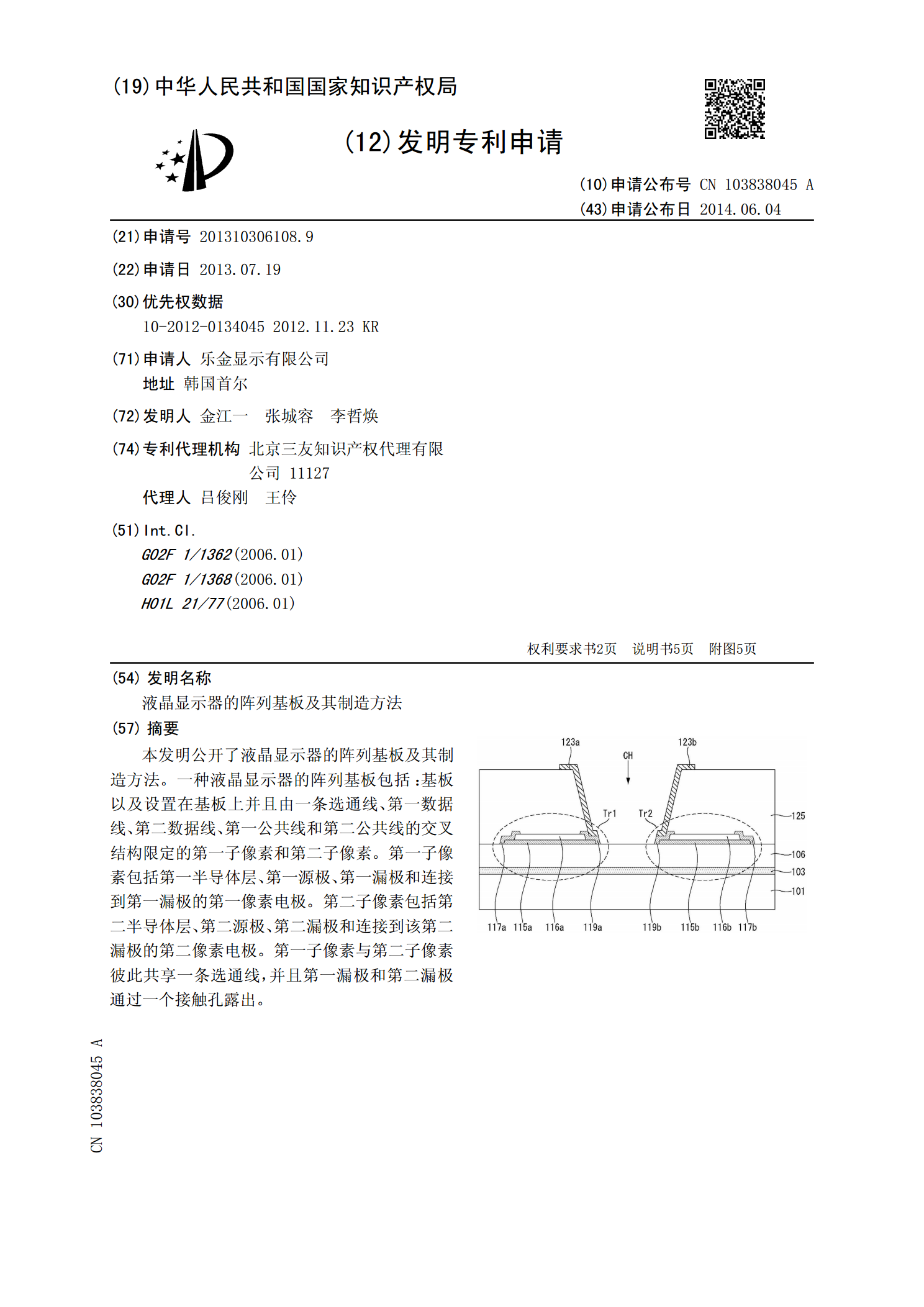

本发明公开了液晶显示器的阵列基板及其制造方法。一种液晶显示器的阵列基板包括:基板以及设置在基板上并且由一条选通线、第一数据线、第二数据线、第一公共线和第二公共线的交叉结构限定的第一子像素和第二子像素。第一子像素包括第一半导体层、第一源极、第一漏极和连接到第一漏极的第一像素电极。第二子像素包括第二半导体层、第二源极、第二漏极和连接到该第二漏极的第二像素电极。第一子像素与第二子像素彼此共享一条选通线,并且第一漏极和第二漏极通过一个接触孔露出。

液晶显示器的阵列基板及其制造方法.pdf

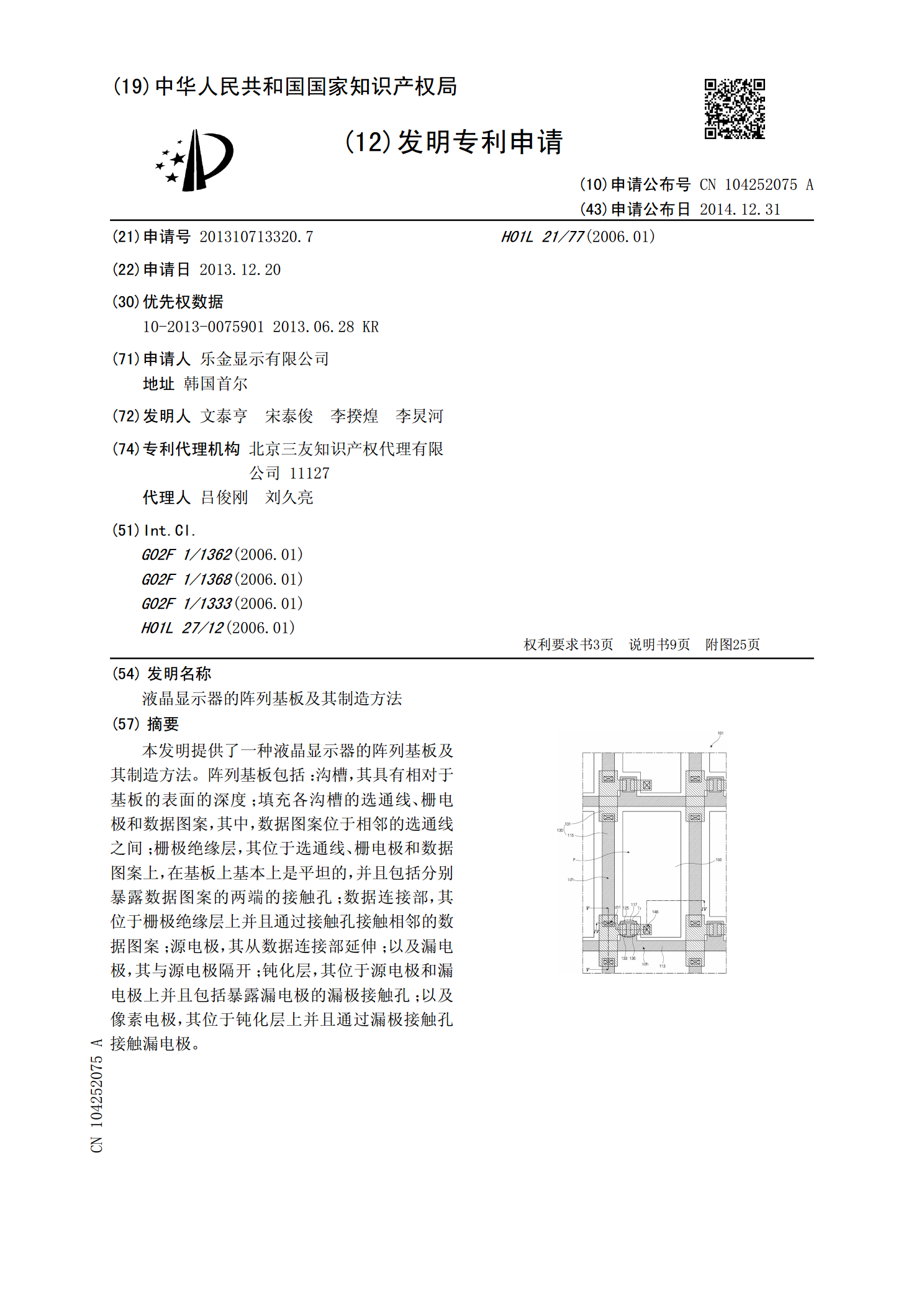

本发明提供了一种液晶显示器的阵列基板及其制造方法。阵列基板包括:沟槽,其具有相对于基板的表面的深度;填充各沟槽的选通线、栅电极和数据图案,其中,数据图案位于相邻的选通线之间;栅极绝缘层,其位于选通线、栅电极和数据图案上,在基板上基本上是平坦的,并且包括分别暴露数据图案的两端的接触孔;数据连接部,其位于栅极绝缘层上并且通过接触孔接触相邻的数据图案;源电极,其从数据连接部延伸;以及漏电极,其与源电极隔开;钝化层,其位于源电极和漏电极上并且包括暴露漏电极的漏极接触孔;以及像素电极,其位于钝化层上并且通过漏极接触

用于液晶显示器的阵列基板及其制造方法.pdf

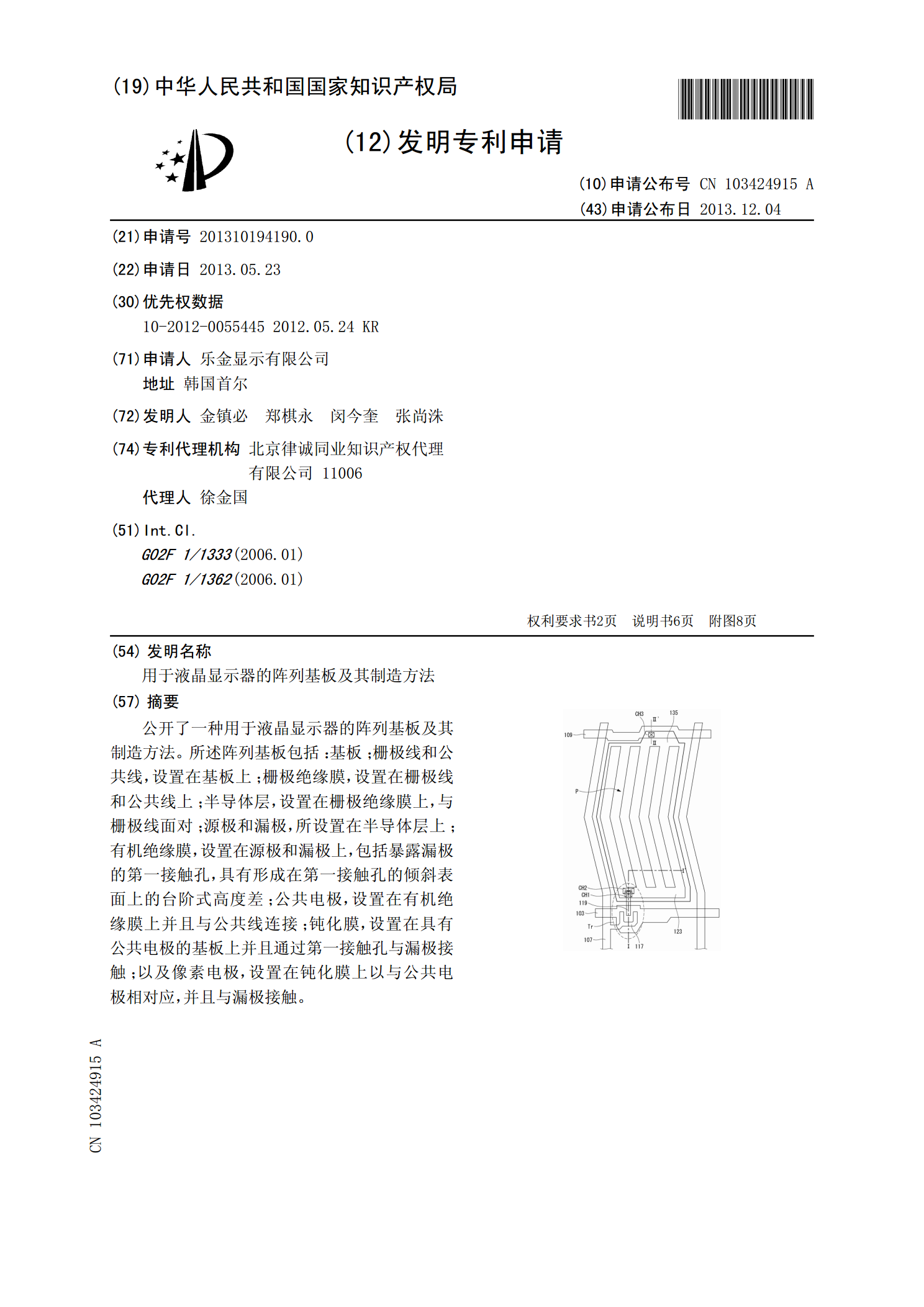

公开了一种用于液晶显示器的阵列基板及其制造方法。所述阵列基板包括:基板;栅极线和公共线,设置在基板上;栅极绝缘膜,设置在栅极线和公共线上;半导体层,设置在栅极绝缘膜上,与栅极线面对;源极和漏极,所设置在半导体层上;有机绝缘膜,设置在源极和漏极上,包括暴露漏极的第一接触孔,具有形成在第一接触孔的倾斜表面上的台阶式高度差;公共电极,设置在有机绝缘膜上并且与公共线连接;钝化膜,设置在具有公共电极的基板上并且通过第一接触孔与漏极接触;以及像素电极,设置在钝化膜上以与公共电极相对应,并且与漏极接触。

阵列基板及其制造方法和液晶显示器.pdf

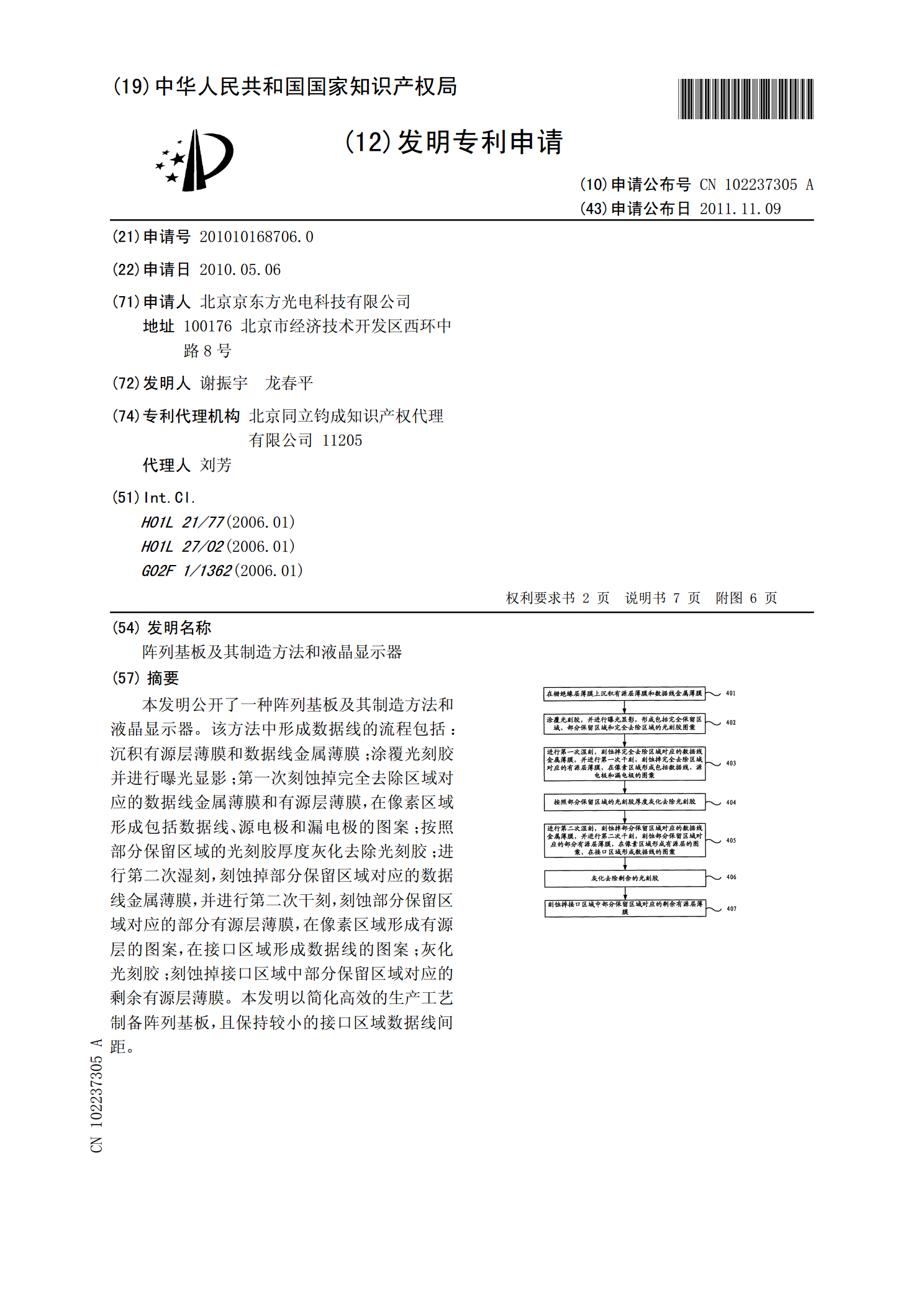

本发明公开了一种阵列基板及其制造方法和液晶显示器。该方法中形成数据线的流程包括:沉积有源层薄膜和数据线金属薄膜;涂覆光刻胶并进行曝光显影;第一次刻蚀掉完全去除区域对应的数据线金属薄膜和有源层薄膜,在像素区域形成包括数据线、源电极和漏电极的图案;按照部分保留区域的光刻胶厚度灰化去除光刻胶;进行第二次湿刻,刻蚀掉部分保留区域对应的数据线金属薄膜,并进行第二次干刻,刻蚀部分保留区域对应的部分有源层薄膜,在像素区域形成有源层的图案,在接口区域形成数据线的图案;灰化光刻胶;刻蚀掉接口区域中部分保留区域对应的剩余有源

阵列基板及其制造方法和液晶显示器.pdf

本发明公开了一种阵列基板及其制造方法和液晶显示器。该制造方法包括:形成有源层薄膜和数据线金属薄膜;涂覆光刻胶,采用多色调掩膜板进行曝光显影,形成三个厚度区域的光刻胶图案;刻蚀掉第三厚度区域对应的数据线金属薄膜和有源层薄膜;灰化去除部分厚度的光刻胶;在保留第一厚度区域光刻胶的衬底基板上形成透明导电薄膜;剥离剩余的光刻胶以及剩余光刻胶上的透明导电薄膜;对露出的数据线金属薄膜和部分有源层薄膜进行刻蚀;刻蚀掉除沟道上方之外的剩余有源层薄膜,形成包括数据线、源电极、漏电极、像素电极和带有沟道的有源层的图案。本发明可