薄膜晶体管阵列基板和包含其的数字X射线检测器.pdf

猫巷****觅蓉

亲,该文档总共34页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

薄膜晶体管阵列基板和包含其的数字X射线检测器.pdf

本申请涉及薄膜晶体管阵列基板和包含其的数字X射线检测器,其中公开了一种用于高分辨率数字X射线检测器的薄膜晶体管阵列基板和包含该薄膜晶体管阵列基板的高分辨率数字X射线检测器,其中通过增加填充因数来改善光敏性,使PIN二极管之间的干扰最小化,并且改善PIN二极管的阶梯覆盖以提高PIN二极管的稳定性。出于这些目的,使PIN二极管的面积最大化,并且在PIN层内设置PIN二极管的像素电极。此外,由无机材料制成的包覆层形成在像素电极的边缘区域和/或接触孔区域中。因此,可以最小化由于在弯曲区域上集中电场而导致的漏电流。

薄膜晶体管阵列基板和包括其的数字X射线检测器.pdf

薄膜晶体管阵列基板和包括其的数字X射线检测器。公开了通过增大填充因子来改进感光性,PIN二极管的稳定性提高并且使寄生电容的产生减少或最小化的用于高分辨率数字X射线检测器的薄膜晶体管阵列基板和包括该薄膜晶体管阵列基板的高分辨率数字X射线检测器。在一个实施方式中,PIN二极管最大程度地延伸,使得薄膜晶体管的电极和接触孔设置在PIN二极管内部。在电极或布线之间存在有机材料的平整层。另外,通过将偏置线设置成与数据线或选通线交叠而不与PIN二极管交叠来使PIN二极管的光接收区域增大或最大化。

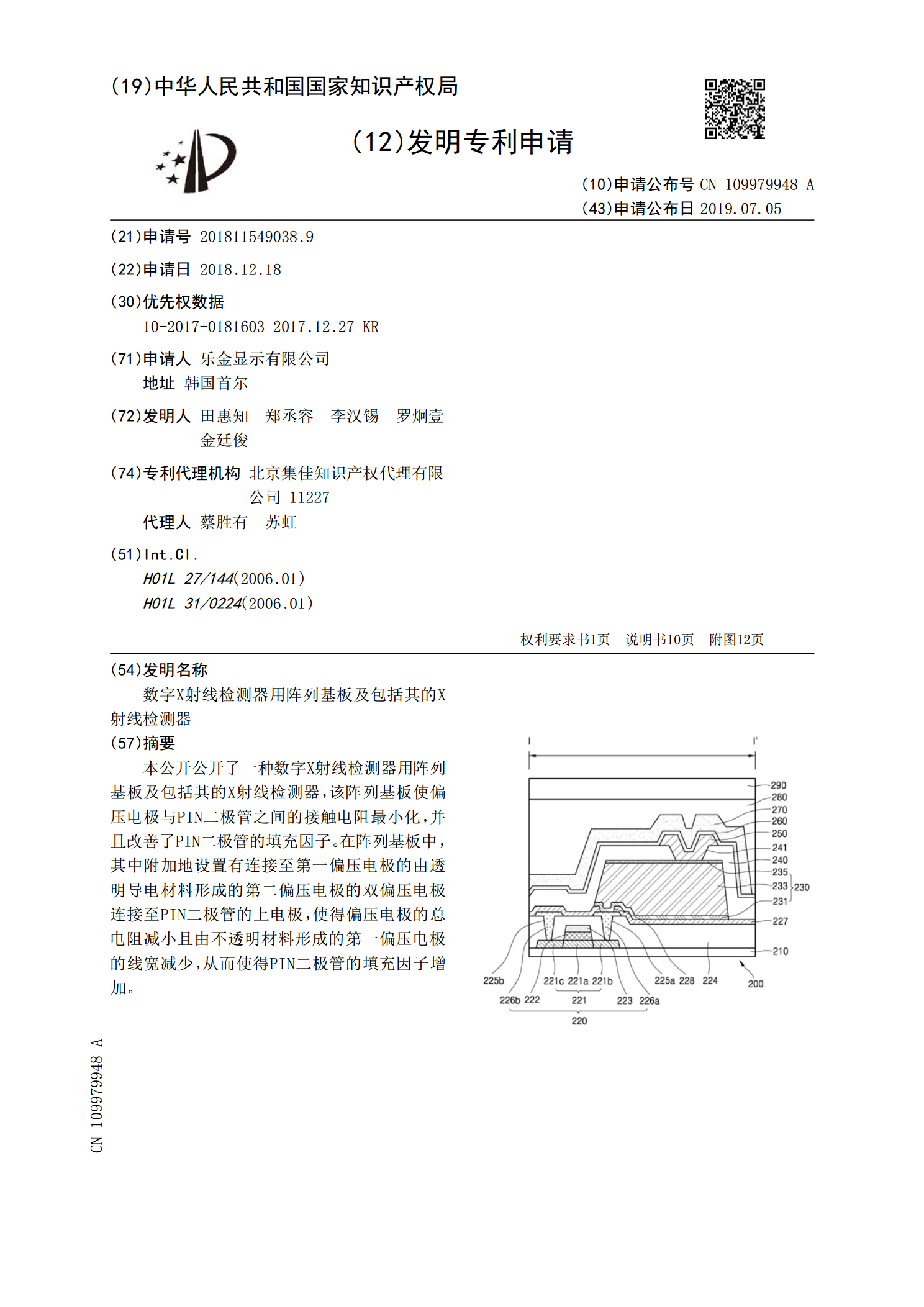

数字X射线检测器用阵列基板及包括其的X射线检测器.pdf

本公开公开了一种数字X射线检测器用阵列基板及包括其的X射线检测器,该阵列基板使偏压电极与PIN二极管之间的接触电阻最小化,并且改善了PIN二极管的填充因子。在阵列基板中,其中附加地设置有连接至第一偏压电极的由透明导电材料形成的第二偏压电极的双偏压电极连接至PIN二极管的上电极,使得偏压电极的总电阻减小且由不透明材料形成的第一偏压电极的线宽减少,从而使得PIN二极管的填充因子增加。

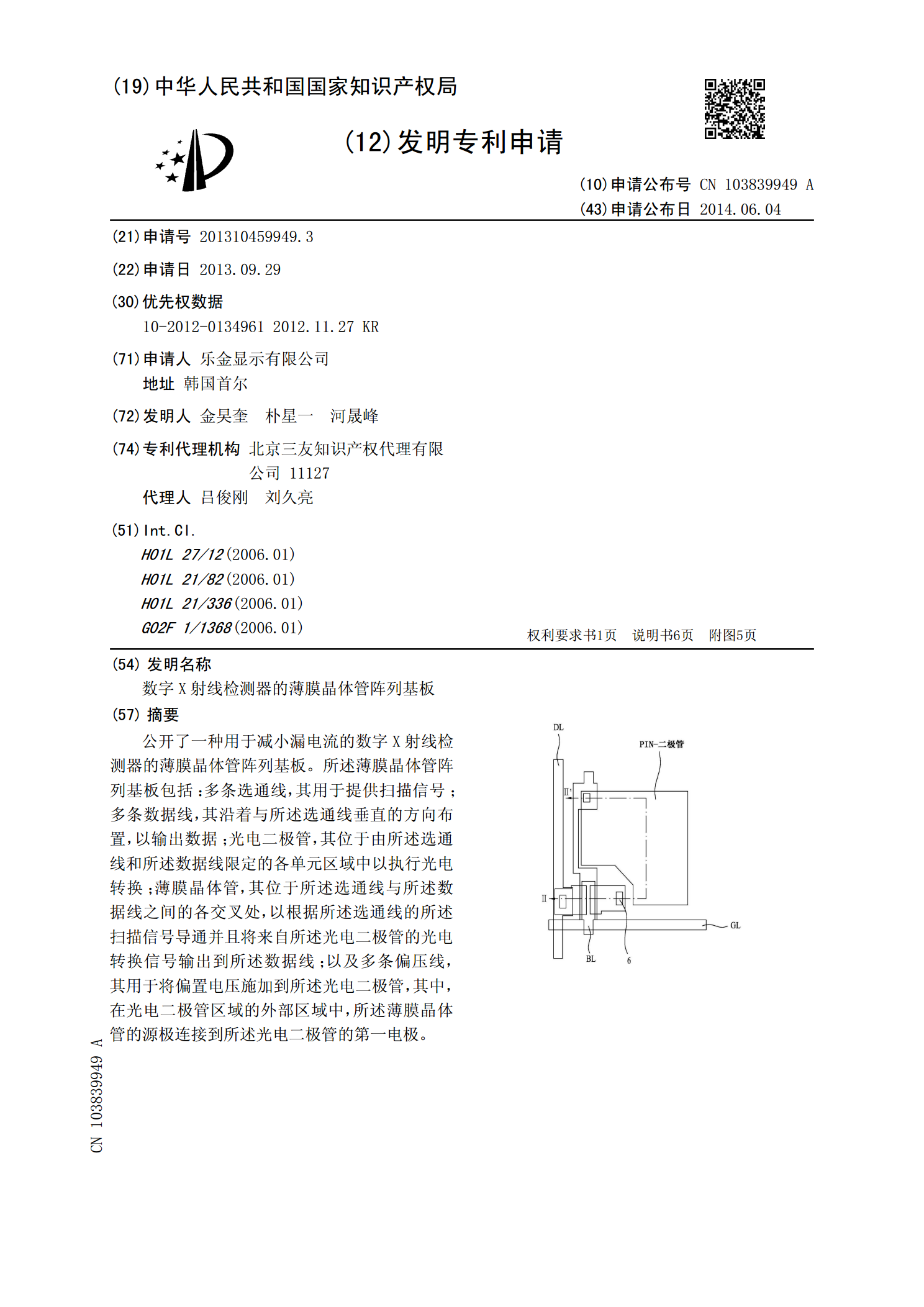

数字X射线检测器的薄膜晶体管阵列基板.pdf

公开了一种用于减小漏电流的数字X射线检测器的薄膜晶体管阵列基板。所述薄膜晶体管阵列基板包括:多条选通线,其用于提供扫描信号;多条数据线,其沿着与所述选通线垂直的方向布置,以输出数据;光电二极管,其位于由所述选通线和所述数据线限定的各单元区域中以执行光电转换;薄膜晶体管,其位于所述选通线与所述数据线之间的各交叉处,以根据所述选通线的所述扫描信号导通并且将来自所述光电二极管的光电转换信号输出到所述数据线;以及多条偏压线,其用于将偏置电压施加到所述光电二极管,其中,在光电二极管区域的外部区域中,所述薄膜晶体管的

用于数字X射线检测器的薄膜晶体管阵列基板.pdf

公开了一种用于数字X射线检测器的薄膜晶体管阵列基板,能够通过向遮光层施加选通电压而非偏置电压以遮蔽薄膜晶体管的沟道区来减少薄膜晶体管漏电流和输出信号噪声。薄膜晶体管阵列基板包括:多条选通线,提供扫描信号;多条数据线,设置在与选通线垂直的方向上,输出数据;光电二极管,形成在由选通线和数据线限定的多个单元区的每一个中,执行光电转换,光电二极管包括按次序层压的第一电极、半导体层、第二电极;薄膜晶体管,形成在选通线与数据线之间的多个交叉点的每一个处,响应于选通线的扫描信号向数据线输出来自光电二极管的光电转换信号;