半导体元件的制备方法.pdf

Ja****44

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

半导体元件的制备方法.pdf

本公开提供一种半导体元件的制备方法。该半导体元件的制备方法包括提供一目标层;形成一第一硬遮罩层在该目标层上;形成多个第二硬遮罩层在该第一硬遮罩层上;执行一第一倾斜蚀刻制程在该第一硬遮罩层上,以形成多个第一开口在沿着该第一硬遮罩并邻近所述第二硬遮罩层的各第一侧处;以及执行一第二倾斜蚀刻制程在该第一硬遮罩层上,以形成多个第二开口在沿着该第一硬遮罩层并邻近所述第二硬遮罩层的各第二侧处。该第一倾斜蚀刻制程与该第二倾斜蚀刻制程使用所述第二硬遮罩层当作图案引导件,且该第一硬遮罩层通过所述第一开口与所述第二开口而转变成

半导体元件的制备方法.pdf

本发明关于一种半导体元件的制备方法,其包括步骤:步骤一:应用传统的工艺流程制备多晶硅栅极并沉积适当厚度的层间介质层(ILD,Interlayer?Dielectric);该多晶硅栅极具有位于下层的浮栅(FG,Floating?Gate)、中间层的氧化物-氮化物-氧化物(ONO)及位于上层的控制栅(CG,Control?Gate);步骤二:利用化学机械抛光将层间介质层ILD磨平并停止在CG多晶硅表面;步骤三:使用对OXIDE选择比很高的湿法刻蚀方法将CG多晶硅完全去除;步骤四:在除去了CG多晶硅的晶圆上沉积

半导体元件及其制备方法.pdf

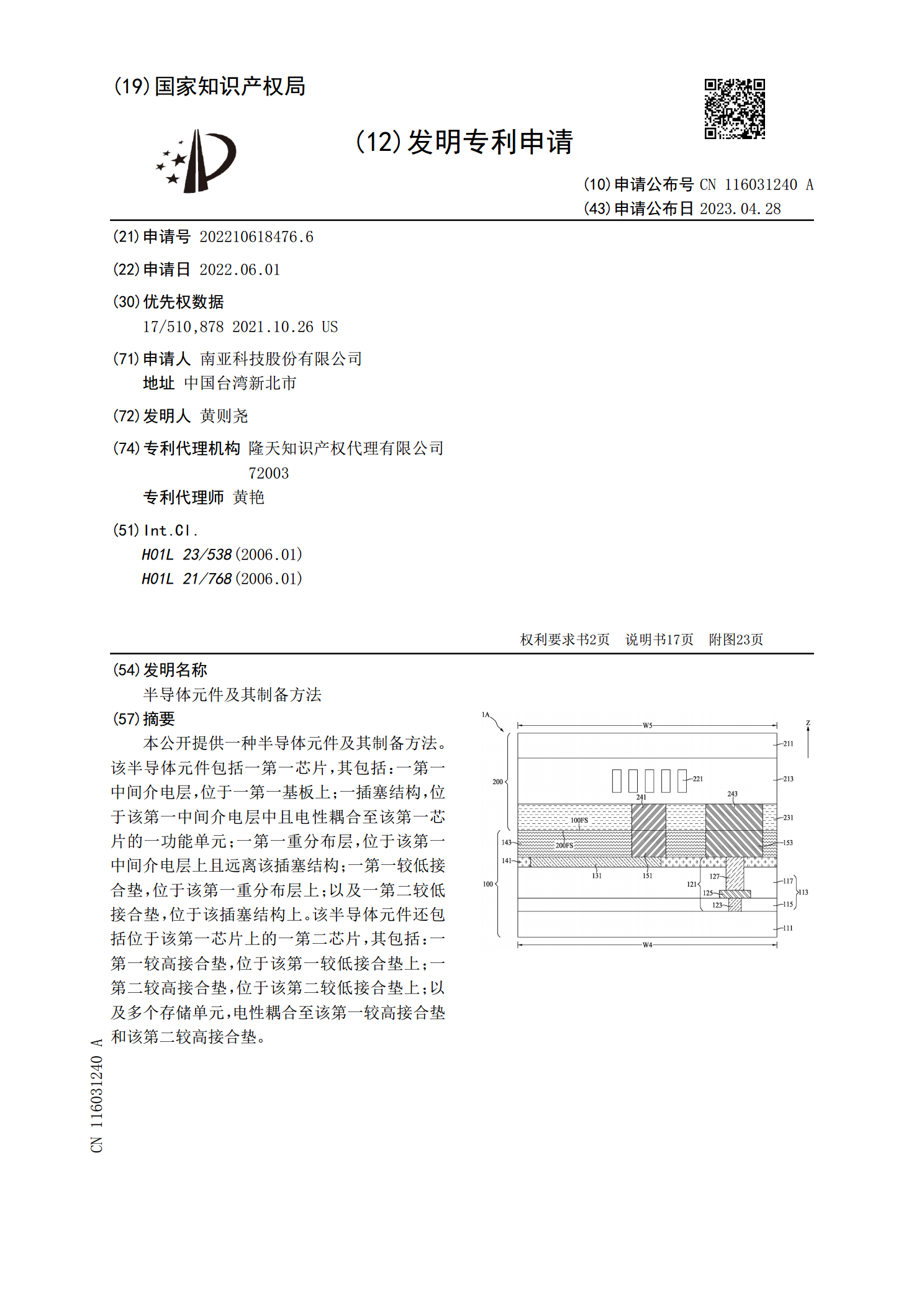

本公开提供一种半导体元件及其制备方法。该半导体元件包括一第一芯片,其包括:一第一中间介电层,位于一第一基板上;一插塞结构,位于该第一中间介电层中且电性耦合至该第一芯片的一功能单元;一第一重分布层,位于该第一中间介电层上且远离该插塞结构;一第一较低接合垫,位于该第一重分布层上;以及一第二较低接合垫,位于该插塞结构上。该半导体元件还包括位于该第一芯片上的一第二芯片,其包括:一第一较高接合垫,位于该第一较低接合垫上;一第二较高接合垫,位于该第二较低接合垫上;以及多个存储单元,电性耦合至该第一较高接合垫和该第二较

半导体元件及其制备方法.pdf

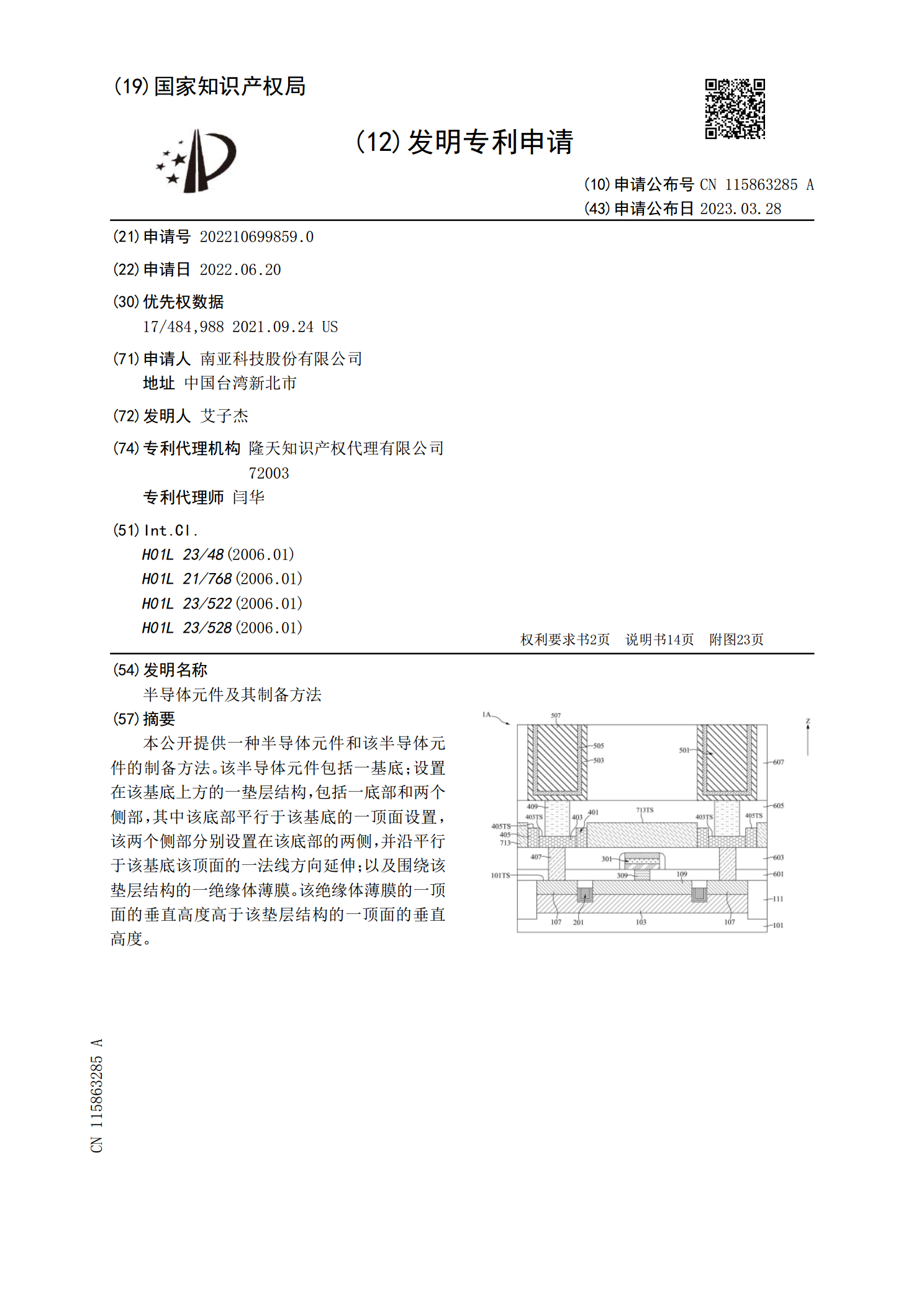

本公开提供一种半导体元件和该半导体元件的制备方法。该半导体元件包括一基底;设置在该基底上方的一垫层结构,包括一底部和两个侧部,其中该底部平行于该基底的一顶面设置,该两个侧部分别设置在该底部的两侧,并沿平行于该基底该顶面的一法线方向延伸;以及围绕该垫层结构的一绝缘体薄膜。该绝缘体薄膜的一顶面的垂直高度高于该垫层结构的一顶面的垂直高度。

半导体元件及其制备方法.pdf

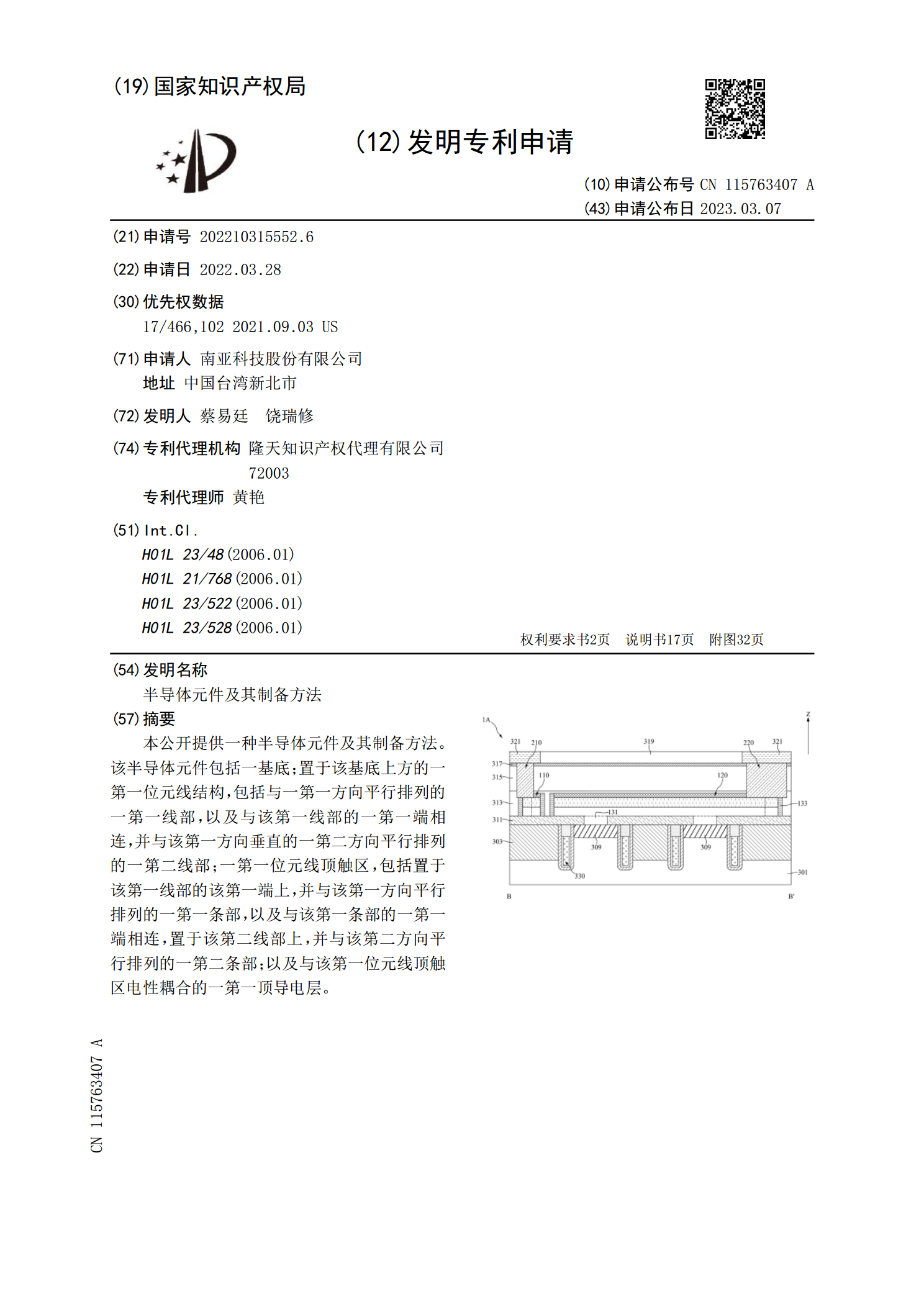

本公开提供一种半导体元件及其制备方法。该半导体元件包括一基底;置于该基底上方的一第一位元线结构,包括与一第一方向平行排列的一第一线部,以及与该第一线部的一第一端相连,并与该第一方向垂直的一第二方向平行排列的一第二线部;一第一位元线顶触区,包括置于该第一线部的该第一端上,并与该第一方向平行排列的一第一条部,以及与该第一条部的一第一端相连,置于该第二线部上,并与该第二方向平行排列的一第二条部;以及与该第一位元线顶触区电性耦合的一第一顶导电层。