半导体器件的制造方法和半导体器件.pdf

玉环****找我

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

半导体器件的制造方法和半导体器件.pdf

本发明提供了一种半导体器件的制造方法和一种半导体器件,其中,所述制造方法包括:对N型外延层进行刻蚀,以形成第一沟槽;在第一沟槽的衬底表面生长第一氧化层并进行回刻处理,仅保留第一沟槽的侧壁上的第一氧化层;对第一沟槽进行填充处理,形成P型填充区域;对P型填充区域进行刻蚀形成多个第二沟槽;在多个第二沟槽的衬底表面生长第二氧化层并进行回刻处理,仅保留多个第二沟槽的侧壁上的第二氧化层;对多个第二沟槽进行填充处理,形成多个N型填充区域,以形成目标衬底结构,并在目标衬底结构的基础上完成半导体器件的制造。通过本发明的技术

制造半导体器件的方法和半导体器件.pdf

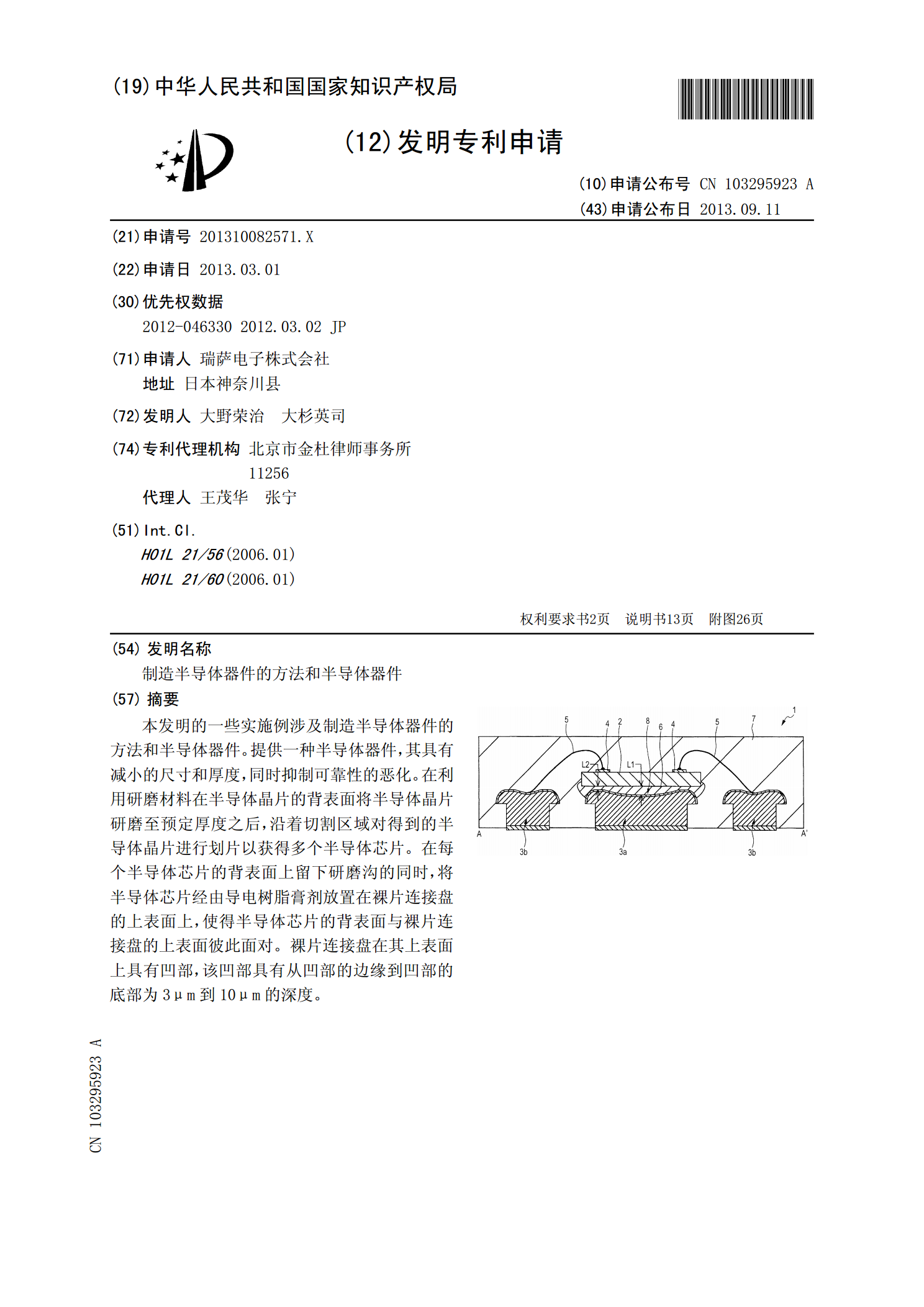

本发明的一些实施例涉及制造半导体器件的方法和半导体器件。提供一种半导体器件,其具有减小的尺寸和厚度,同时抑制可靠性的恶化。在利用研磨材料在半导体晶片的背表面将半导体晶片研磨至预定厚度之后,沿着切割区域对得到的半导体晶片进行划片以获得多个半导体芯片。在每个半导体芯片的背表面上留下研磨沟的同时,将半导体芯片经由导电树脂膏剂放置在裸片连接盘的上表面上,使得半导体芯片的背表面与裸片连接盘的上表面彼此面对。裸片连接盘在其上表面上具有凹部,该凹部具有从凹部的边缘到凹部的底部为3μm到10μm的深度。

制造半导体器件的方法和半导体器件.pdf

本申请的实施例提供了一种半导体器件及其制造方法。在制造半导体器件的方法中,在衬底上方形成栅极介电层;在栅极介电层上方形成牺牲层;图案化牺牲层以形成牺牲栅电极;通过部分地蚀刻牺牲栅电极在牺牲栅电极中形成多个开口;利用与牺牲栅电极的材料不同的填充材料填充多个开口;去除牺牲栅电极以形成栅极空间,从而在栅极空间中留下多个柱或壁;以及利用一种或多种导电材料填充栅极空间,从而形成金属栅电极。

用于制造半导体器件的方法和半导体器件.pdf

本发明涉及用于制造半导体器件的方法和半导体器件。一种制造半导体器件的方法包括:提供具有主表面(101)的半导体基底(199)和在相邻半导体台面(191、192)之间的沟槽(190)内的栅电极(150)。栅电极(150)通过各自的电介质层与相邻半导体台面(191、192)绝缘。在相邻半导体台面(191、192)中的每个上形成各自的立柱(201、202),从而在沟槽(190)之上在立柱(201、202)之间留下开口(400)。沿各自的立柱侧壁在开口(400)中形成电介质接触间隔物(211、212)以收窄栅电极

用于制造半导体器件的方法和半导体器件.pdf

提出一种用于制造多个半导体器件(1)的方法,所述方法具有如下步骤:a)提供半导体层序列(2),所述半导体层序列具有第一半导体层(21)、第二半导体层(22)和设置在第一半导体层和第二半导体层之间的有源区域(25),所述有源区域设置用于产生和/或接收辐射;b)在第二半导体层的背离第一半导体层的一侧上构成第一连接层(31);c)构成多个穿过半导体层序列的留空部(29);d)在留空部中构成传导层(4)用于在第一半导体层和第一连接层之间建立导电连接;和e)分割成多个半导体器件,其中从半导体层序列中为每个半导体器件