一种实现低抖动的时钟产生电路.pdf

文光****iu

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种实现低抖动的时钟产生电路.pdf

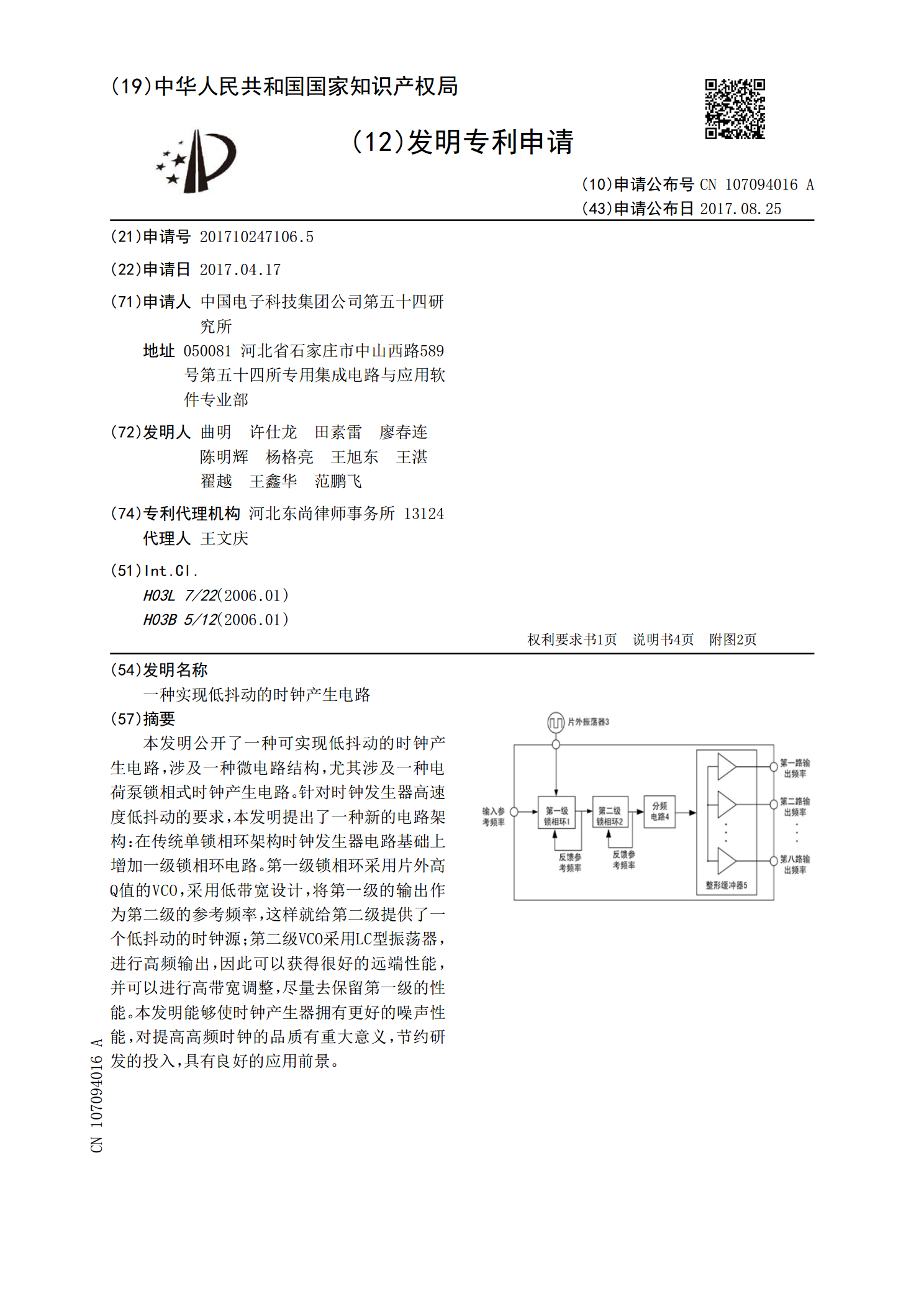

本发明公开了一种可实现低抖动的时钟产生电路,涉及一种微电路结构,尤其涉及一种电荷泵锁相式时钟产生电路。针对时钟发生器高速度低抖动的要求,本发明提出了一种新的电路架构:在传统单锁相环架构时钟发生器电路基础上增加一级锁相环电路。第一级锁相环采用片外高Q值的VCO,采用低带宽设计,将第一级的输出作为第二级的参考频率,这样就给第二级提供了一个低抖动的时钟源;第二级VCO采用LC型振荡器,进行高频输出,因此可以获得很好的远端性能,并可以进行高带宽调整,尽量去保留第一级的性能。本发明能够使时钟产生器拥有更好的噪声性能

一种应用于TDC的低抖动多相高频时钟产生电路设计的开题报告.docx

一种应用于TDC的低抖动多相高频时钟产生电路设计的开题报告开题报告:一种应用于TDC的低抖动多相高频时钟产生电路设计一、研究背景TDC(Time-to-DigitalConverter)作为时钟测量的一种重要技术手段,被广泛应用于高性能计算、粒子探测器、飞行器导航、医学成像等领域。为了实现高精度的时间测量,TDC需要用到高精度、高稳定性、低抖动的时钟信号。因此,设计一种低抖动多相高频时钟产生电路,对TDC和其它精密测量系统具有重要的意义。二、研究目的本文旨在设计一种低抖动多相高频时钟产生电路,具有以下目的

一种时钟产生电路以及时钟校准方法.pdf

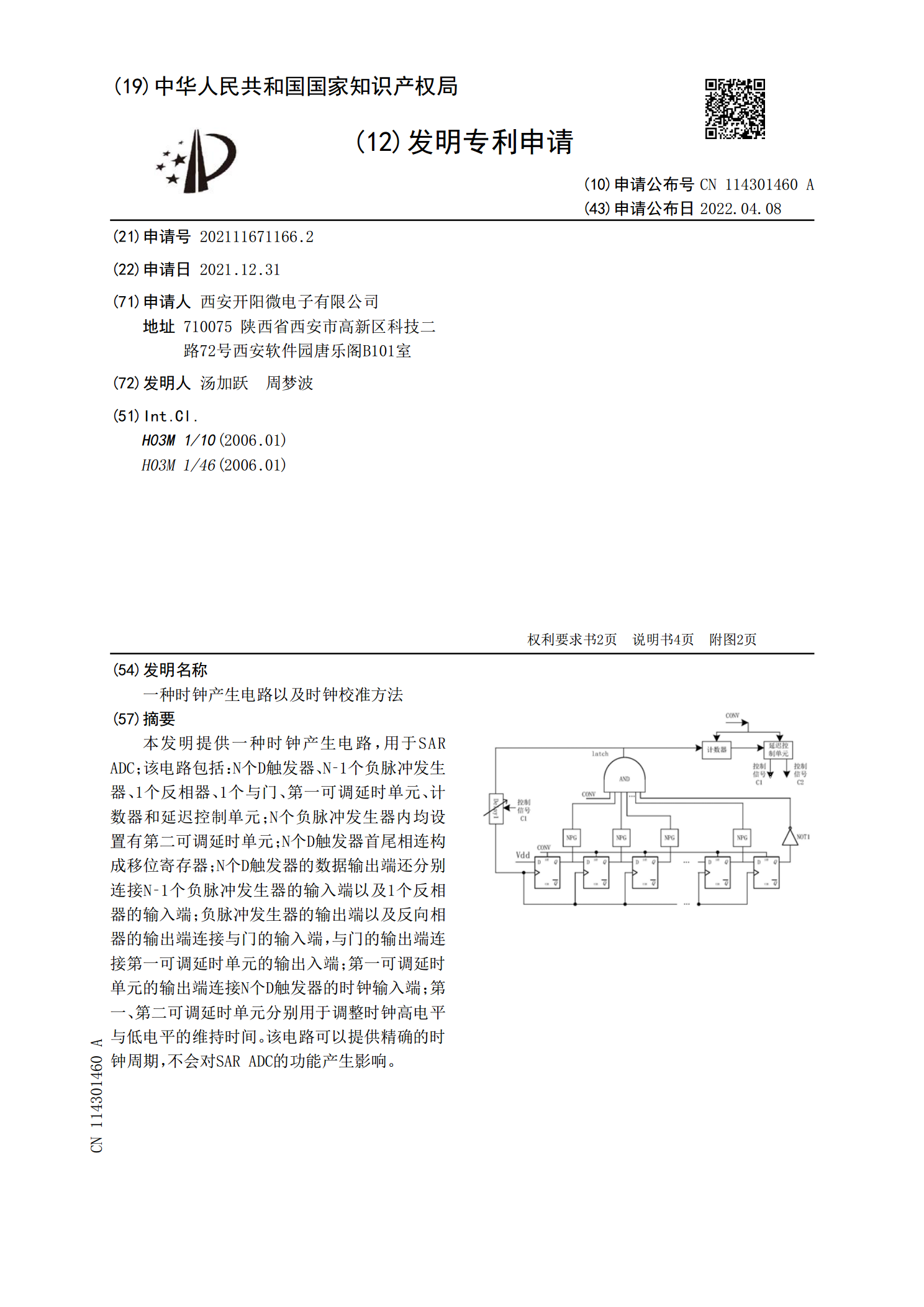

本发明提供一种时钟产生电路,用于SARADC;该电路包括:N个D触发器、N?1个负脉冲发生器、1个反相器、1个与门、第一可调延时单元、计数器和延迟控制单元;N个负脉冲发生器内均设置有第二可调延时单元;N个D触发器首尾相连构成移位寄存器;N个D触发器的数据输出端还分别连接N?1个负脉冲发生器的输入端以及1个反相器的输入端;负脉冲发生器的输出端以及反向相器的输出端连接与门的输入端,与门的输出端连接第一可调延时单元的输出入端;第一可调延时单元的输出端连接N个D触发器的时钟输入端;第一、第二可调延时单元分别用于调

一种稳定的片内时钟产生电路.pdf

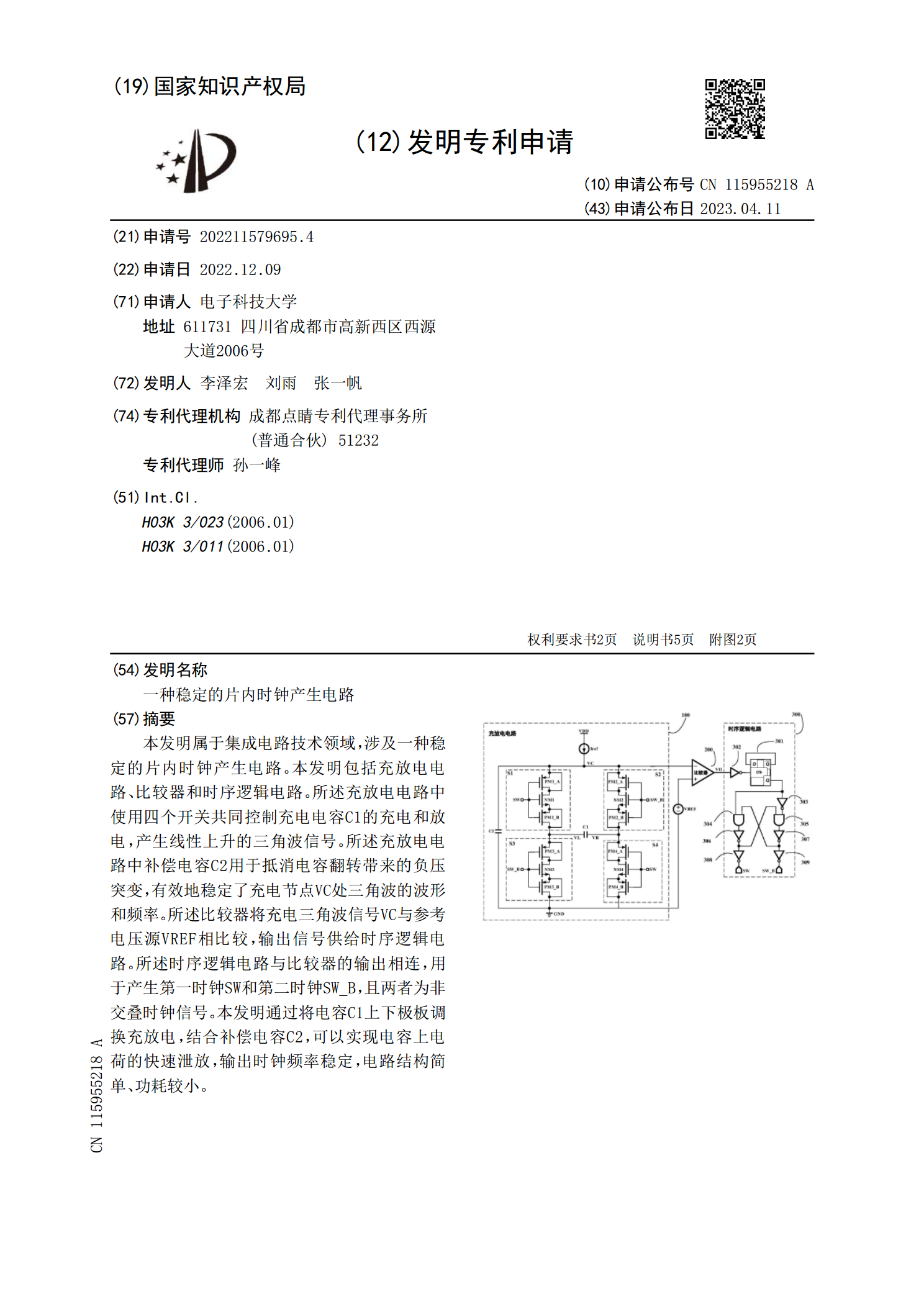

本发明属于集成电路技术领域,涉及一种稳定的片内时钟产生电路。本发明包括充放电电路、比较器和时序逻辑电路。所述充放电电路中使用四个开关共同控制充电电容C1的充电和放电,产生线性上升的三角波信号。所述充放电电路中补偿电容C2用于抵消电容翻转带来的负压突变,有效地稳定了充电节点VC处三角波的波形和频率。所述比较器将充电三角波信号VC与参考电压源VREF相比较,输出信号供给时序逻辑电路。所述时序逻辑电路与比较器的输出相连,用于产生第一时钟SW和第二时钟SW_B,且两者为非交叠时钟信号。本发明通过将电容C1上下极板

时钟信号产生电路、时钟信号产生方法及电子设备.pdf

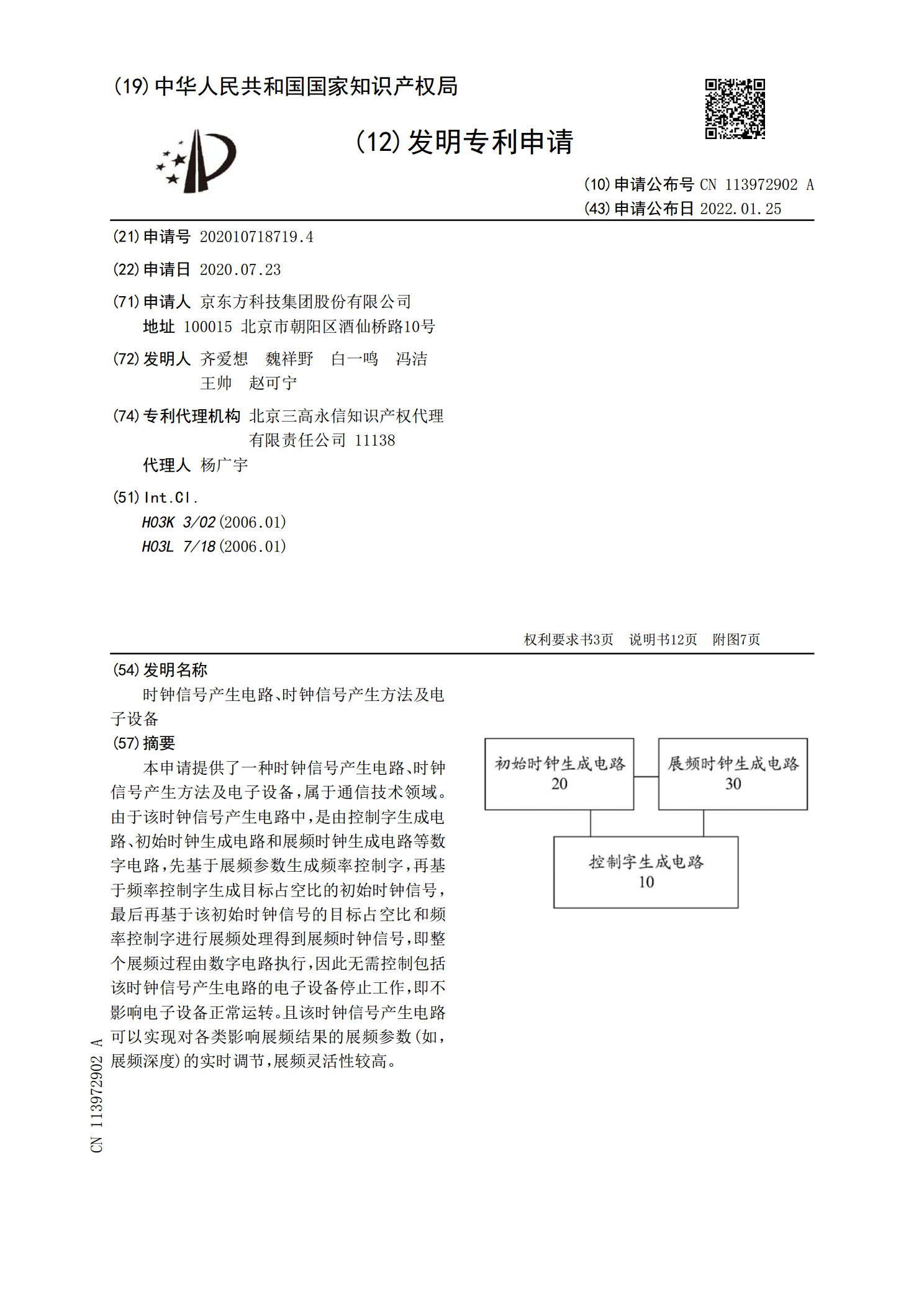

本申请提供了一种时钟信号产生电路、时钟信号产生方法及电子设备,属于通信技术领域。由于该时钟信号产生电路中,是由控制字生成电路、初始时钟生成电路和展频时钟生成电路等数字电路,先基于展频参数生成频率控制字,再基于频率控制字生成目标占空比的初始时钟信号,最后再基于该初始时钟信号的目标占空比和频率控制字进行展频处理得到展频时钟信号,即整个展频过程由数字电路执行,因此无需控制包括该时钟信号产生电路的电子设备停止工作,即不影响电子设备正常运转。且该时钟信号产生电路可以实现对各类影响展频结果的展频参数(如,展频深度)的