一种应用于TDC的低抖动多相高频时钟产生电路设计的开题报告.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种应用于TDC的低抖动多相高频时钟产生电路设计的开题报告.docx

一种应用于TDC的低抖动多相高频时钟产生电路设计的开题报告开题报告:一种应用于TDC的低抖动多相高频时钟产生电路设计一、研究背景TDC(Time-to-DigitalConverter)作为时钟测量的一种重要技术手段,被广泛应用于高性能计算、粒子探测器、飞行器导航、医学成像等领域。为了实现高精度的时间测量,TDC需要用到高精度、高稳定性、低抖动的时钟信号。因此,设计一种低抖动多相高频时钟产生电路,对TDC和其它精密测量系统具有重要的意义。二、研究目的本文旨在设计一种低抖动多相高频时钟产生电路,具有以下目的

一种实现低抖动的时钟产生电路.pdf

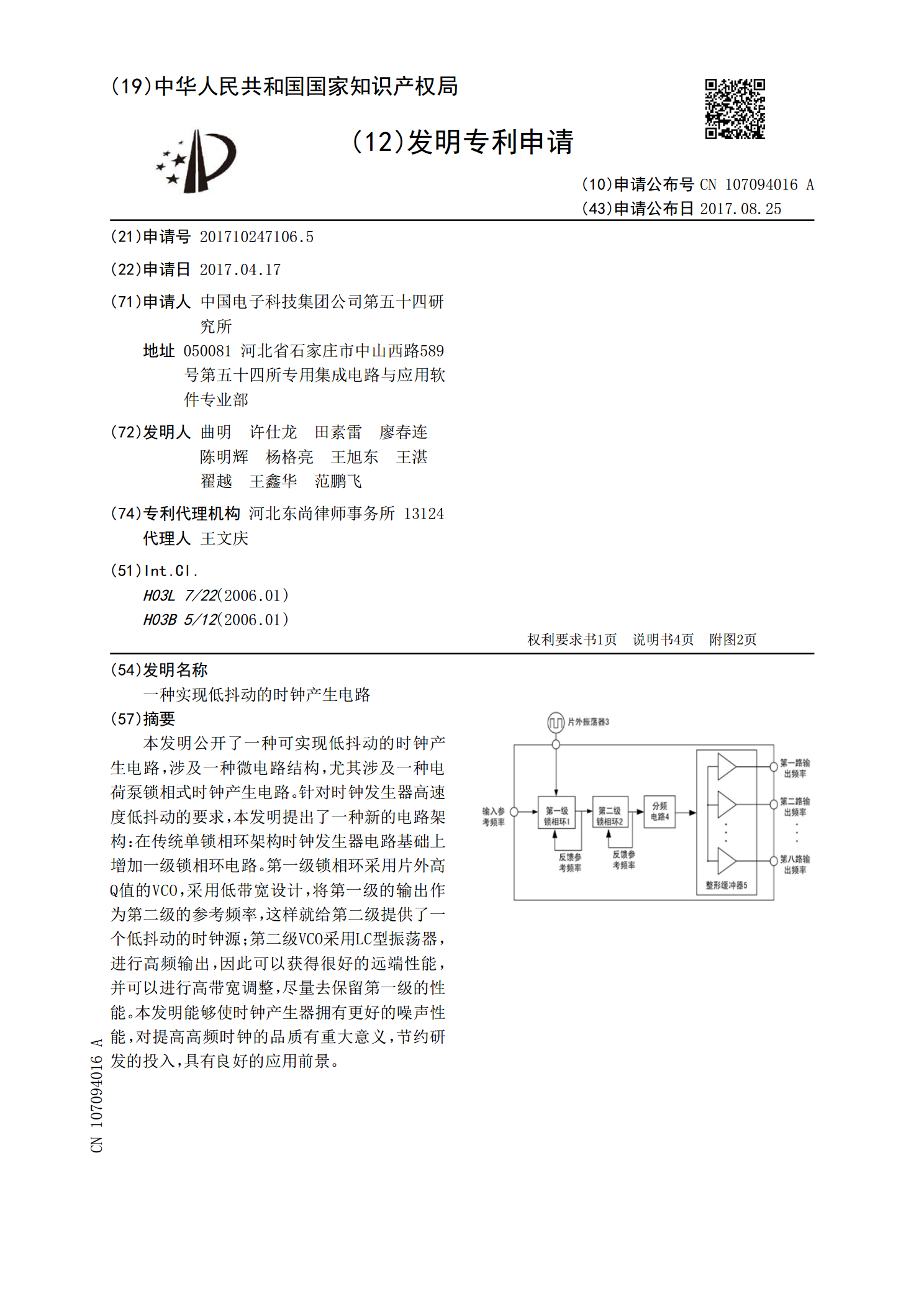

本发明公开了一种可实现低抖动的时钟产生电路,涉及一种微电路结构,尤其涉及一种电荷泵锁相式时钟产生电路。针对时钟发生器高速度低抖动的要求,本发明提出了一种新的电路架构:在传统单锁相环架构时钟发生器电路基础上增加一级锁相环电路。第一级锁相环采用片外高Q值的VCO,采用低带宽设计,将第一级的输出作为第二级的参考频率,这样就给第二级提供了一个低抖动的时钟源;第二级VCO采用LC型振荡器,进行高频输出,因此可以获得很好的远端性能,并可以进行高带宽调整,尽量去保留第一级的性能。本发明能够使时钟产生器拥有更好的噪声性能

基于温度的DRAM刷新时钟产生电路设计的开题报告.docx

基于温度的DRAM刷新时钟产生电路设计的开题报告一、课题背景和意义DRAM(DynamicRandomAccessMemory)是计算机主存储器中最重要的一种,其存储单元通过电容存储电荷来表示二进制数字,因此需要定期进行刷新操作以避免数据丢失。目前常见的DRAM刷新方法是周期性刷新,即定期向所有存储单元写入数据以刷新电容电荷状态。然而,随着DRAM尺寸的不断扩大和操作速度的不断提高,周期性刷新频率的增加会带来更大的功耗和性能损失,因此研究更加高效的刷新方法具有重要的意义。目前已有研究表明,在一定范围内,D

一种新颖的高精度多相时钟发生电路设计.pdf

万方数据一种新颖的高精度多相时钟发生电路设计2磊孑1而i×109=2·08ps,误差为±‘r赢簧南西)%=l·64%,在本文设计的五相时钟过采样作用下,高速通信李浩亮,张防震引言系统总体架构PLL电路MHz时钟信号“B”,信号“B”进入DLL0多相时钟发生器的设计可归结为两大类方法【l'2J:第一种基于负反馈技术,可分为两小类.一是采用“PLL(锁相环:PhaseLoop)+插入器(Interpolator)”构架Hj,二是采用DLL(DigitalLoop)构架M1;第二种方法采用无反馈(NF:No—F

基于DLL技术的多相时钟设计的开题报告.docx

基于DLL技术的多相时钟设计的开题报告一、选题背景随着计算机技术的发展,计算机系统中时钟的重要性也越来越受到人们的关注。时钟作为计算机系统中的核心组件,不仅需要提供稳定、准确的时序信号,还需要支持多种不同频率、不同相位的时钟信号。在时钟信号设计中,多相时钟是一种较为普遍的时钟架构,其特点是可以支持多个不同的相位时钟,并且可以在一个时钟周期内对不同的组件提供不同的时钟信号。因此,在高速计算机系统中,多相时钟应用得越来越广泛。为了实现多相时钟的设计,基于DLL(Delay-LockedLoop)技术的PLL(