存储结构及其制作方法.pdf

书生****写意

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

存储结构及其制作方法.pdf

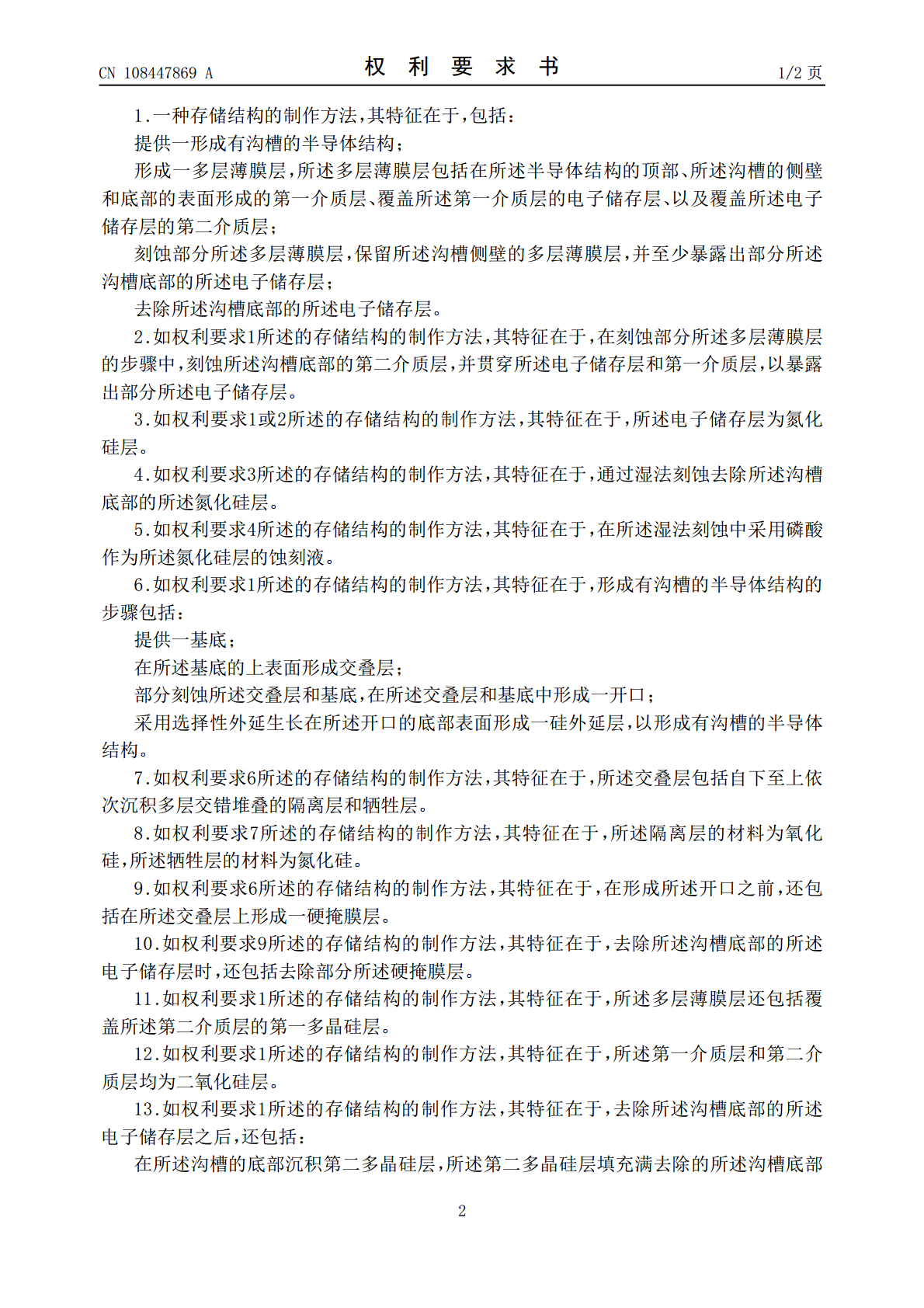

本发明公开了一种存储结构及其制作方法,所述制作方法包括:提供一形成有沟槽的半导体结构;形成一多层薄膜层,所述多层薄膜层包括在所述半导体结构的顶部、所述沟槽的侧壁和底部的表面形成的第一介质层、覆盖所述第一介质层的电子储存层、以及覆盖所述电子储存层的第二介质层;刻蚀部分所述多层薄膜层,保留所述沟槽侧壁的多层薄膜层,并至少暴露出部分所述沟槽底部的所述电子储存层;去除所述沟槽底部的所述电子储存层。本发明通过去除所述沟槽底部的所述电子储存层,可以防止在所述沟槽底部的所述电子储存层中出现电子储存的现象,提高存储结构的

半导体结构及其制作方法、存储器.pdf

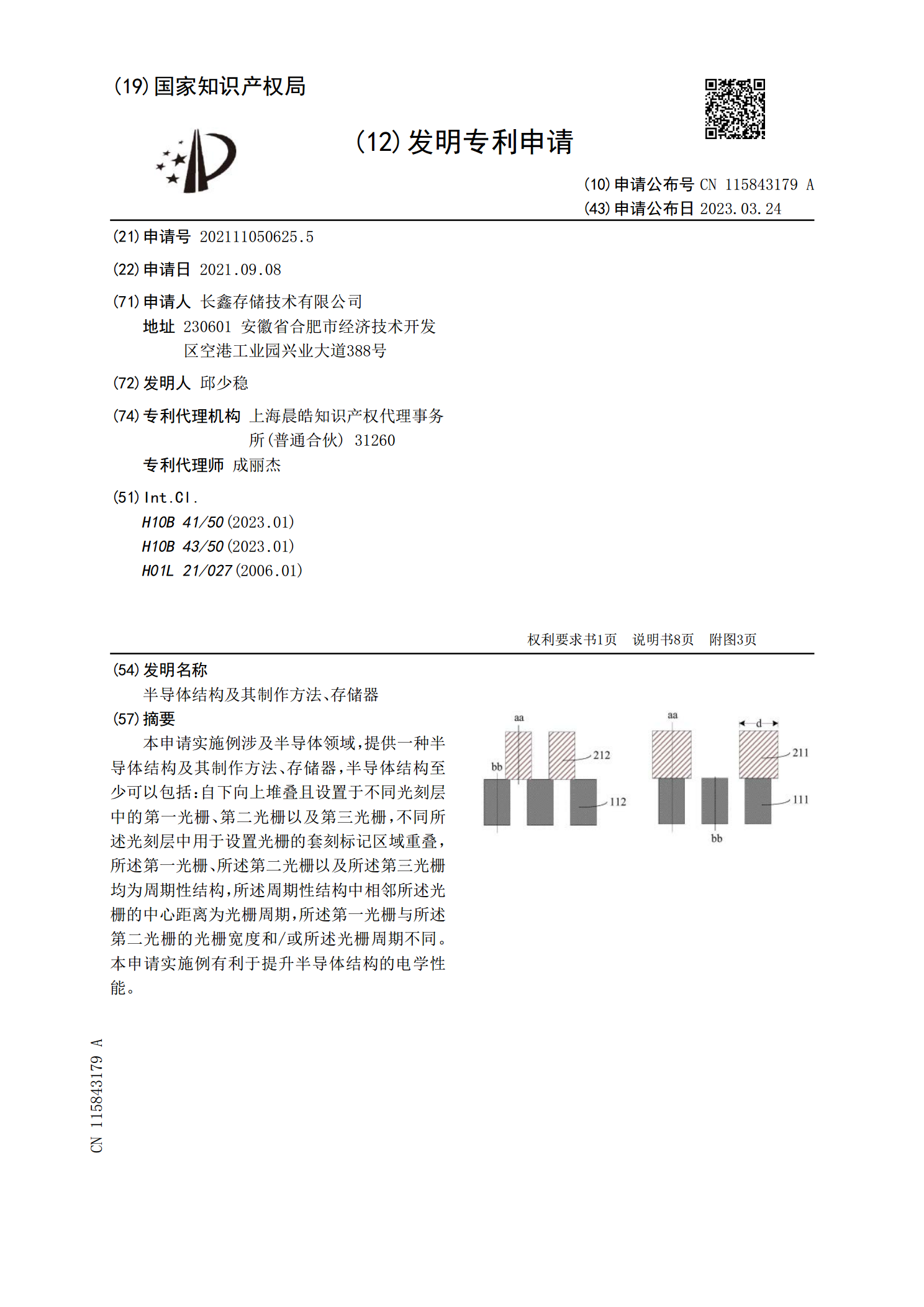

本申请实施例涉及半导体领域,提供一种半导体结构及其制作方法、存储器,半导体结构至少可以包括:自下向上堆叠且设置于不同光刻层中的第一光栅、第二光栅以及第三光栅,不同所述光刻层中用于设置光栅的套刻标记区域重叠,所述第一光栅、所述第二光栅以及所述第三光栅均为周期性结构,所述周期性结构中相邻所述光栅的中心距离为光栅周期,所述第一光栅与所述第二光栅的光栅宽度和/或所述光栅周期不同。本申请实施例有利于提升半导体结构的电学性能。

半导体结构及其制作方法、存储器.pdf

本公开实施例提出了一种半导体结构及其制作方法、存储器,其中,半导体结构包括:多个有源区,沿相交的第一方向和第二方向呈阵列排布且被隔离结构间隔开;位线选择结构,包括位于相互相邻的四个有源区上的第一栅极、第二栅极、第三栅极和第四栅极,以及位于隔离结构上的至少一条连接线;第一栅极的一个端部与第二栅极的一个端部连接,第三栅极的一个端部与第四栅极的一个端部连接,连接线连接第一栅极和第三栅极对应的两个端部和/或所述第二栅极和第四栅极对应的两个端部;多个接触结构;每一接触结构位于一栅极的两侧中靠近连接线的一侧且与一有源

半导体结构及其制作方法、存储器.pdf

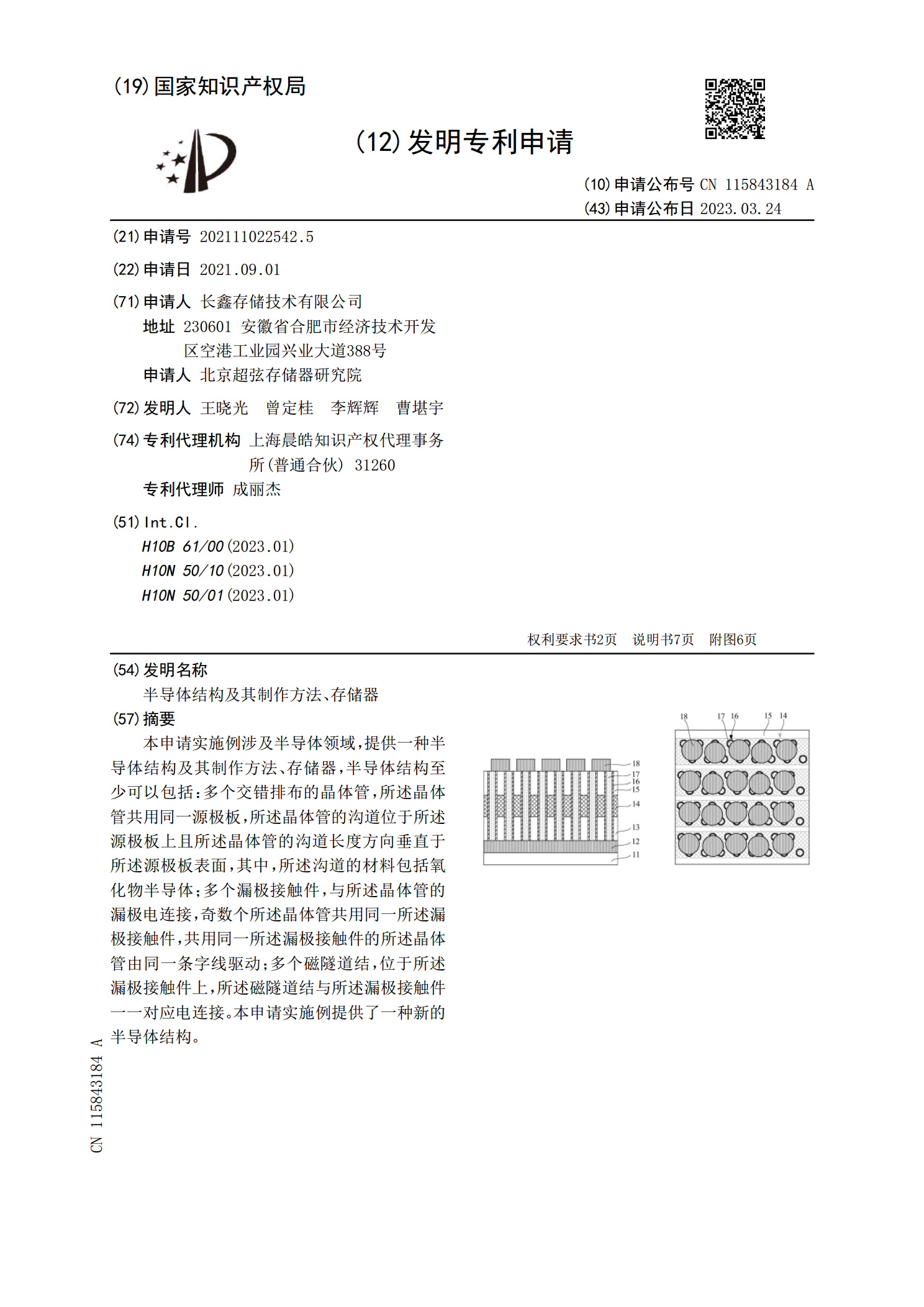

本申请实施例涉及半导体领域,提供一种半导体结构及其制作方法、存储器,半导体结构至少可以包括:多个交错排布的晶体管,所述晶体管共用同一源极板,所述晶体管的沟道位于所述源极板上且所述晶体管的沟道长度方向垂直于所述源极板表面,其中,所述沟道的材料包括氧化物半导体;多个漏极接触件,与所述晶体管的漏极电连接,奇数个所述晶体管共用同一所述漏极接触件,共用同一所述漏极接触件的所述晶体管由同一条字线驱动;多个磁隧道结,位于所述漏极接触件上,所述磁隧道结与所述漏极接触件一一对应电连接。本申请实施例提供了一种新的半导体结构。

半导体结构及其制作方法、存储器.pdf

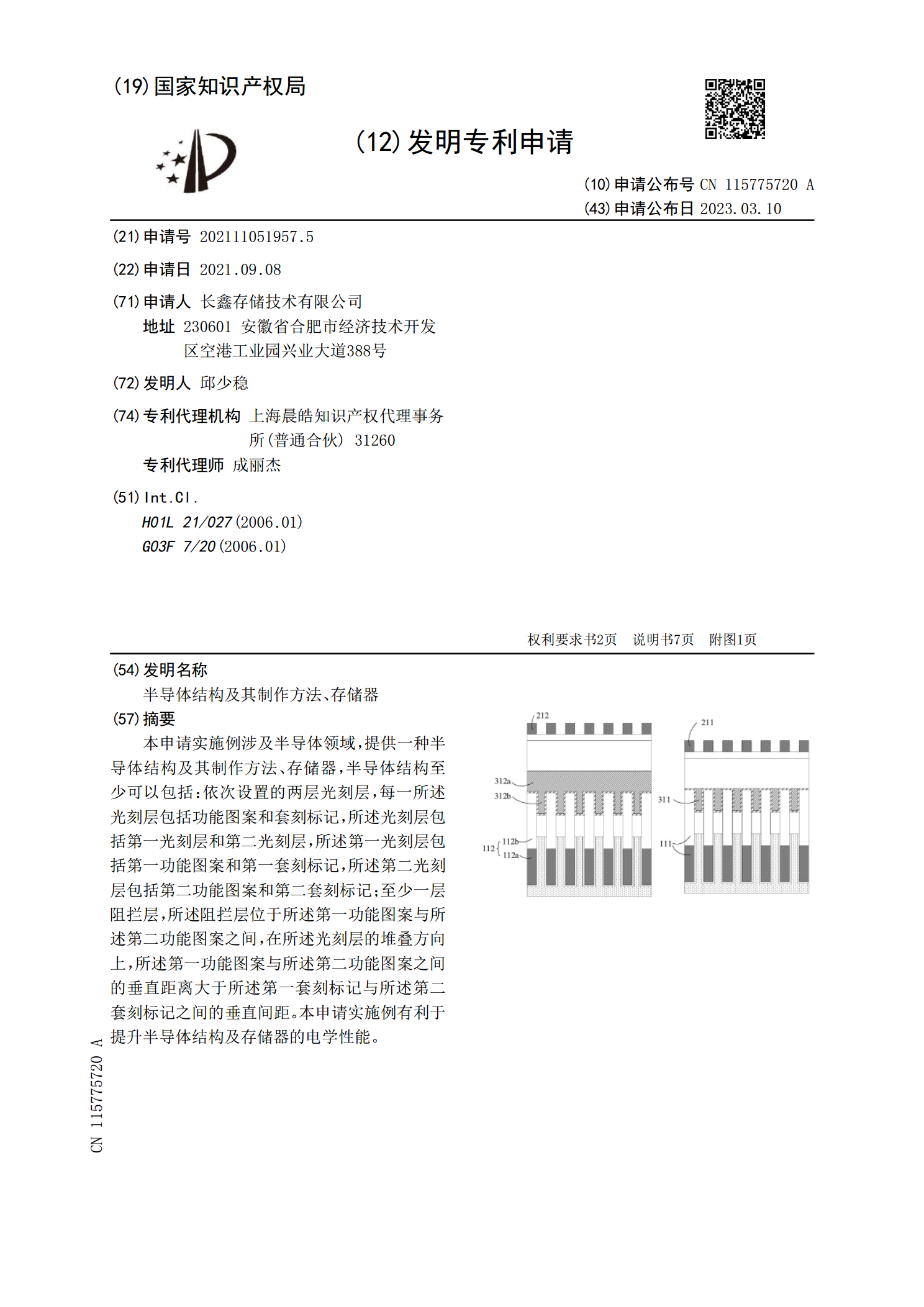

本申请实施例涉及半导体领域,提供一种半导体结构及其制作方法、存储器,半导体结构至少可以包括:依次设置的两层光刻层,每一所述光刻层包括功能图案和套刻标记,所述光刻层包括第一光刻层和第二光刻层,所述第一光刻层包括第一功能图案和第一套刻标记,所述第二光刻层包括第二功能图案和第二套刻标记;至少一层阻拦层,所述阻拦层位于所述第一功能图案与所述第二功能图案之间,在所述光刻层的堆叠方向上,所述第一功能图案与所述第二功能图案之间的垂直距离大于所述第一套刻标记与所述第二套刻标记之间的垂直间距。本申请实施例有利于提升半导体结