半导体元件的精细岛状图案形成方法.pdf

猫巷****忠娟

亲,该文档总共16页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体元件的精细岛状图案形成方法.pdf

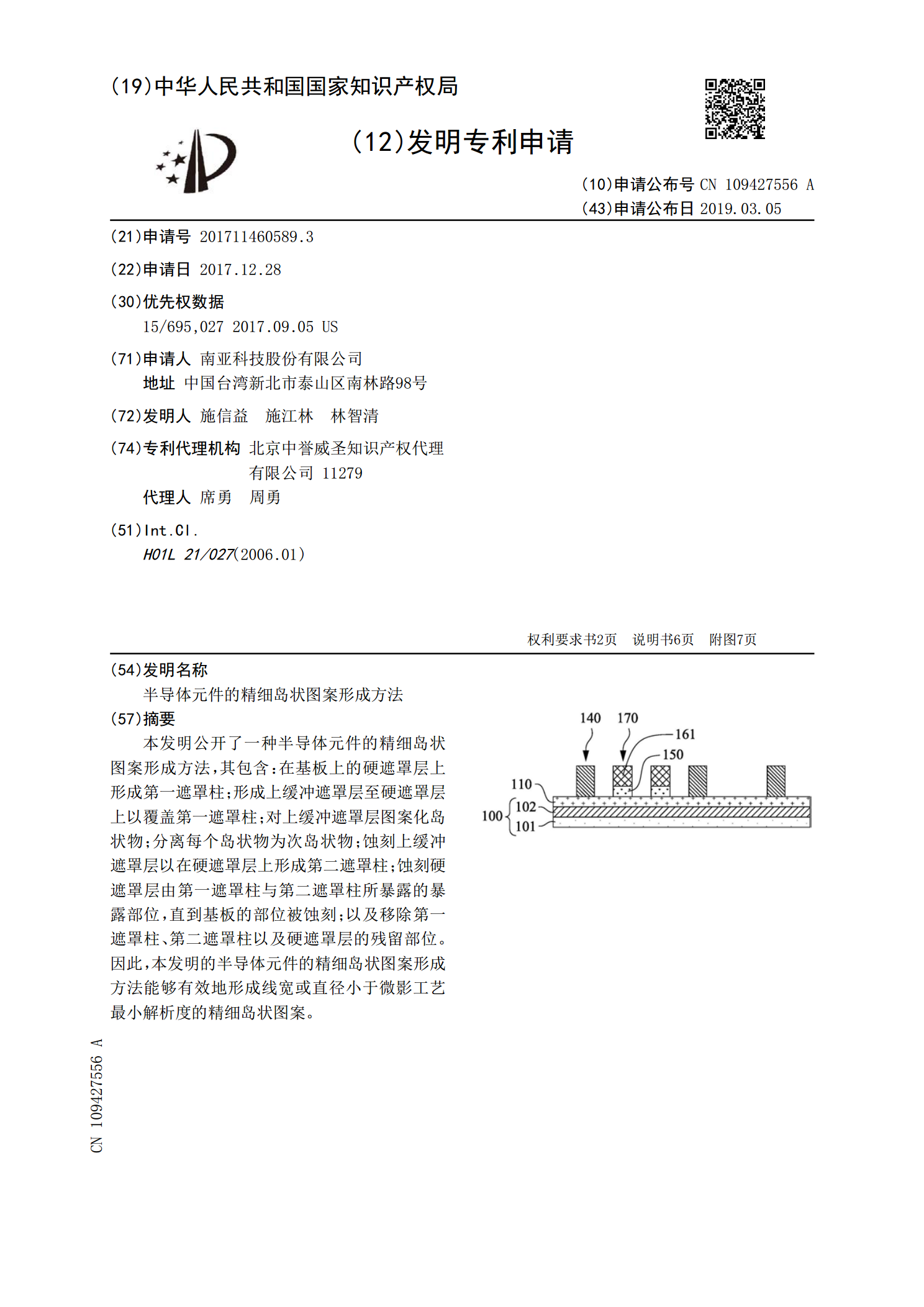

本发明公开了一种半导体元件的精细岛状图案形成方法,其包含:在基板上的硬遮罩层上形成第一遮罩柱;形成上缓冲遮罩层至硬遮罩层上以覆盖第一遮罩柱;对上缓冲遮罩层图案化岛状物;分离每个岛状物为次岛状物;蚀刻上缓冲遮罩层以在硬遮罩层上形成第二遮罩柱;蚀刻硬遮罩层由第一遮罩柱与第二遮罩柱所暴露的暴露部位,直到基板的部位被蚀刻;以及移除第一遮罩柱、第二遮罩柱以及硬遮罩层的残留部位。因此,本发明的半导体元件的精细岛状图案形成方法能够有效地形成线宽或直径小于微影工艺最小解析度的精细岛状图案。

形成图案的方法、精细图案层以及半导体装置.pdf

一种形成图案的方法、精细图案层以及半导体装置。形成图案的方法包括:在衬底上形成蚀刻对象层,在蚀刻对象层上形成具有凸图案的第一层,形成完全覆盖第一层的凸图案的第二层,部分地移除第二层以暴露出凸图案的顶部、同时留下设置于凸图案的侧处的第二层,移除第一层以暴露出蚀刻对象层的顶部,以及使用设置于被移除的第一层的凸部的侧面处的第二层作为蚀刻掩模对蚀刻对象层进行蚀刻,其中第一层及第二层中的一者为含碳的层且另一者为含硅的层,含硅的层是通过对含硅的组合物进行涂布并对硅的组合物进行热处理来形成。本发明可实现精细的图案并同时

使用半双向图案化和岛形成半导体器件的方法.pdf

本发明涉及一种使用半双向图案化和岛形成半导体器件的方法。提供了使用半双向图案化制造集成电路器件的器件和方法。一种方法例如包括:获得具有电介质层、第一硬掩模层、第二硬掩模层、第三硬掩模层和光刻叠层的中间半导体器件;图案化第一组线;在第一组线之间图案化第二组线;蚀刻以限定第一和第二组线的组合;沉积第二光刻叠层;图案化岛的组;蚀刻以限定该组的岛,留下OPL;在OPL上沉积间隔物;蚀刻间隔物,留下垂直间隔物的组;以及使用第三硬掩模层和该组的垂直间隔物作为掩模蚀刻第二硬掩模层。

形成半导体器件的图案的方法.pdf

本发明公开一种形成半导体器件的图案的方法,具体地公开了使用间隔物图案化工序形成半导体器件的图案的方法,该方法包括:在包括间隔物图案的基板上涂覆可显影的抗反射膜;在抗反射膜上涂覆光阻膜;以及利用曝光和显影工序将抗反射膜和光阻膜图案化以形成蚀刻掩模图案。蚀刻掩模图案具有良好的轮廓。当使用蚀刻掩模图案蚀刻下面的基层时,可以保证足够的蚀刻裕量,从而获得可靠的半导体器件。

半导体结构及形成元件的方法.pdf

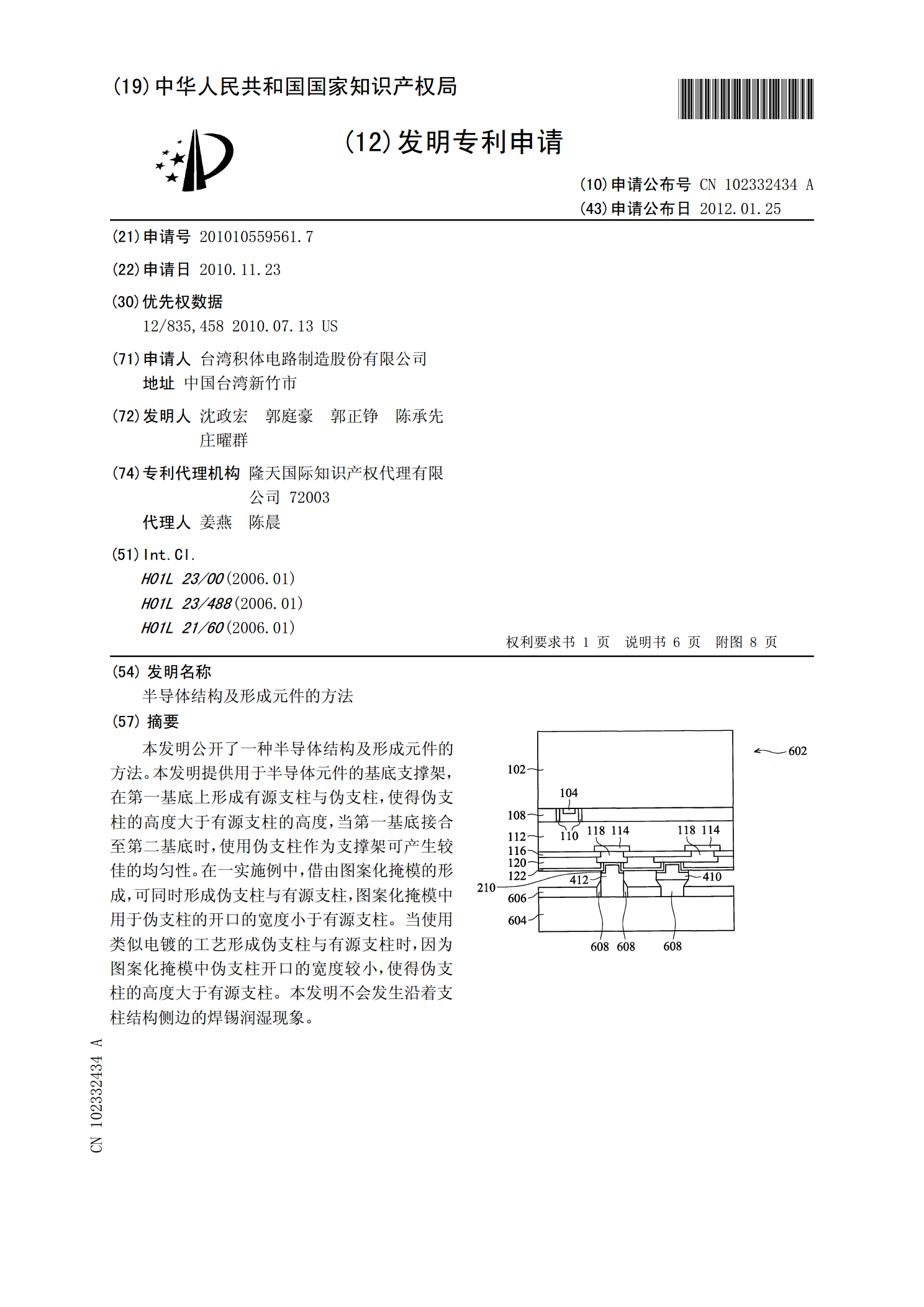

本发明公开了一种半导体结构及形成元件的方法。本发明提供用于半导体元件的基底支撑架,在第一基底上形成有源支柱与伪支柱,使得伪支柱的高度大于有源支柱的高度,当第一基底接合至第二基底时,使用伪支柱作为支撑架可产生较佳的均匀性。在一实施例中,借由图案化掩模的形成,可同时形成伪支柱与有源支柱,图案化掩模中用于伪支柱的开口的宽度小于有源支柱。当使用类似电镀的工艺形成伪支柱与有源支柱时,因为图案化掩模中伪支柱开口的宽度较小,使得伪支柱的高度大于有源支柱。本发明不会发生沿着支柱结构侧边的焊锡润湿现象。