使用半双向图案化和岛形成半导体器件的方法.pdf

邻家****曼玉

亲,该文档总共25页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

使用半双向图案化和岛形成半导体器件的方法.pdf

本发明涉及一种使用半双向图案化和岛形成半导体器件的方法。提供了使用半双向图案化制造集成电路器件的器件和方法。一种方法例如包括:获得具有电介质层、第一硬掩模层、第二硬掩模层、第三硬掩模层和光刻叠层的中间半导体器件;图案化第一组线;在第一组线之间图案化第二组线;蚀刻以限定第一和第二组线的组合;沉积第二光刻叠层;图案化岛的组;蚀刻以限定该组的岛,留下OPL;在OPL上沉积间隔物;蚀刻间隔物,留下垂直间隔物的组;以及使用第三硬掩模层和该组的垂直间隔物作为掩模蚀刻第二硬掩模层。

形成半导体器件的图案的方法.pdf

本发明公开一种形成半导体器件的图案的方法,具体地公开了使用间隔物图案化工序形成半导体器件的图案的方法,该方法包括:在包括间隔物图案的基板上涂覆可显影的抗反射膜;在抗反射膜上涂覆光阻膜;以及利用曝光和显影工序将抗反射膜和光阻膜图案化以形成蚀刻掩模图案。蚀刻掩模图案具有良好的轮廓。当使用蚀刻掩模图案蚀刻下面的基层时,可以保证足够的蚀刻裕量,从而获得可靠的半导体器件。

掩模版和使用该掩模版形成半导体器件中的图案的方法.pdf

提供了掩模版和使用该掩模版形成半导体器件中的图案的方法。所述掩模版包括:掩模基板;反射层,所述反射层位于所述掩模基板上;以及掩模图案,所述掩模图案位于所述反射层上,并且具有用于吸收光的图像图案和位于所述图像图案之间的第一图案,所述第一图案是开口,并且在俯视图中具有蜂窝状排列,使得七个所述第一图案布置在第一正六边形的相应的顶点和中心处,并且每个所述第一图案具有相对于所述第一正六边形旋转90度的第二正六边形的形状。

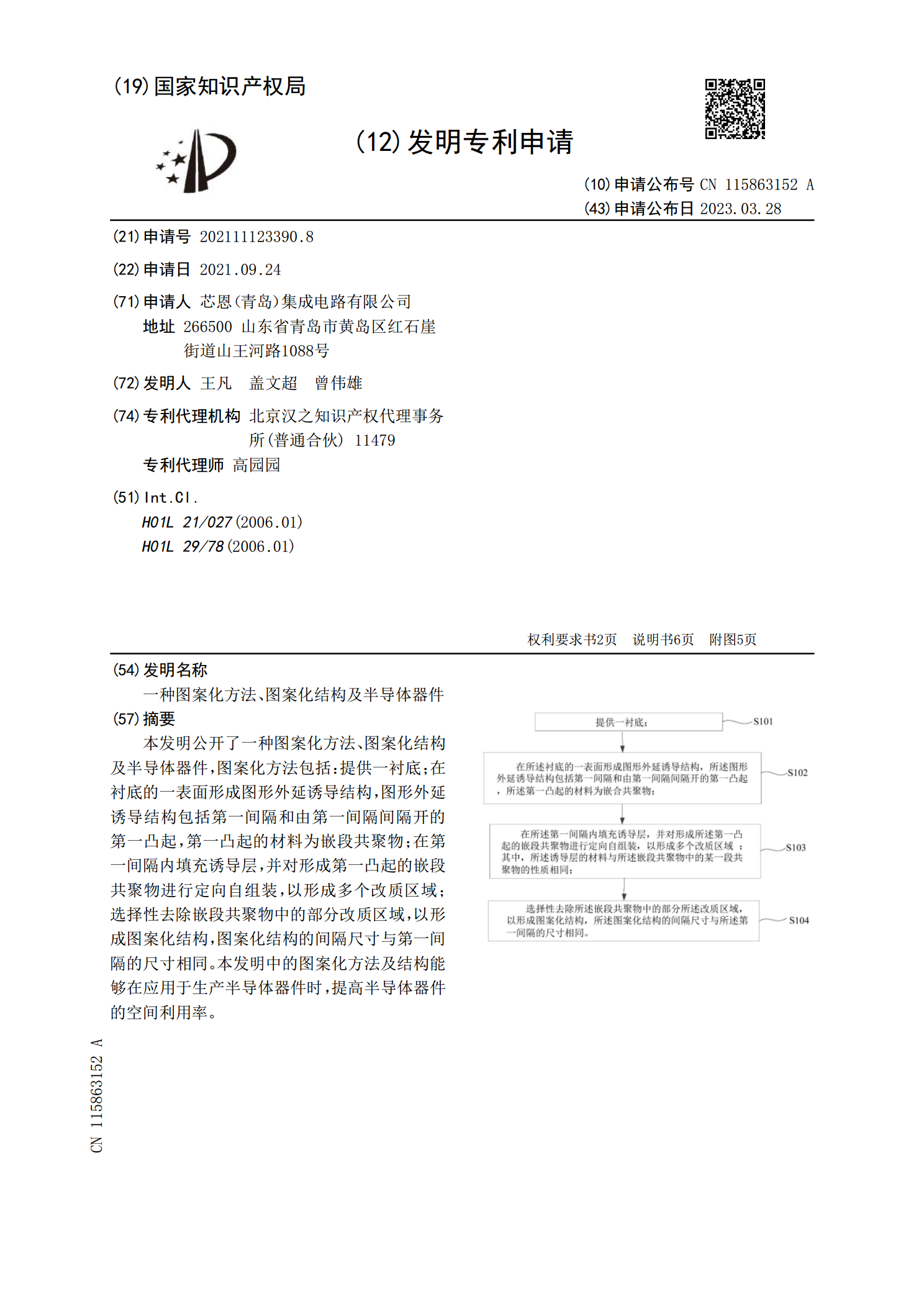

一种图案化方法、图案化结构及半导体器件.pdf

本发明公开了一种图案化方法、图案化结构及半导体器件,图案化方法包括:提供一衬底;在衬底的一表面形成图形外延诱导结构,图形外延诱导结构包括第一间隔和由第一间隔间隔开的第一凸起,第一凸起的材料为嵌段共聚物;在第一间隔内填充诱导层,并对形成第一凸起的嵌段共聚物进行定向自组装,以形成多个改质区域;选择性去除嵌段共聚物中的部分改质区域,以形成图案化结构,图案化结构的间隔尺寸与第一间隔的尺寸相同。本发明中的图案化方法及结构能够在应用于生产半导体器件时,提高半导体器件的空间利用率。

半导体器件和用于形成半导体器件的方法.pdf

本发明涉及半导体器件和用于形成半导体器件的方法。该方法包括:在半导体衬底中形成场效应晶体管结构的源极区域。该方法还包括:形成氧化物层。该方法还包括:在形成氧化物层之后,将原子类型群组中至少一种原子类型的原子并入到场效应晶体管结构的源极区域的至少一部分中。该原子类型群组包括硫族元素原子、硅原子和氩原子。