半导体结构及形成元件的方法.pdf

是飞****文章

亲,该文档总共16页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体结构及形成元件的方法.pdf

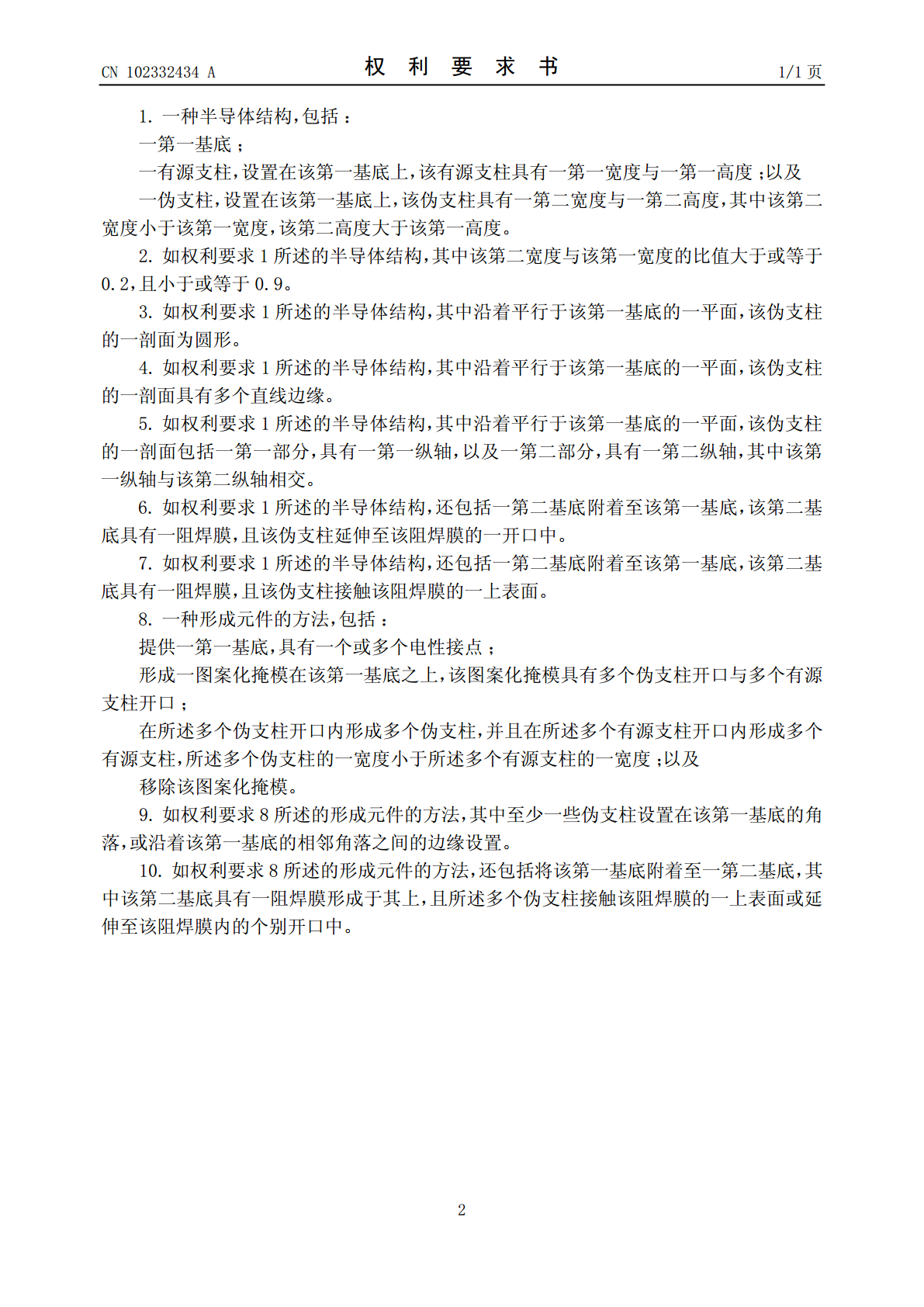

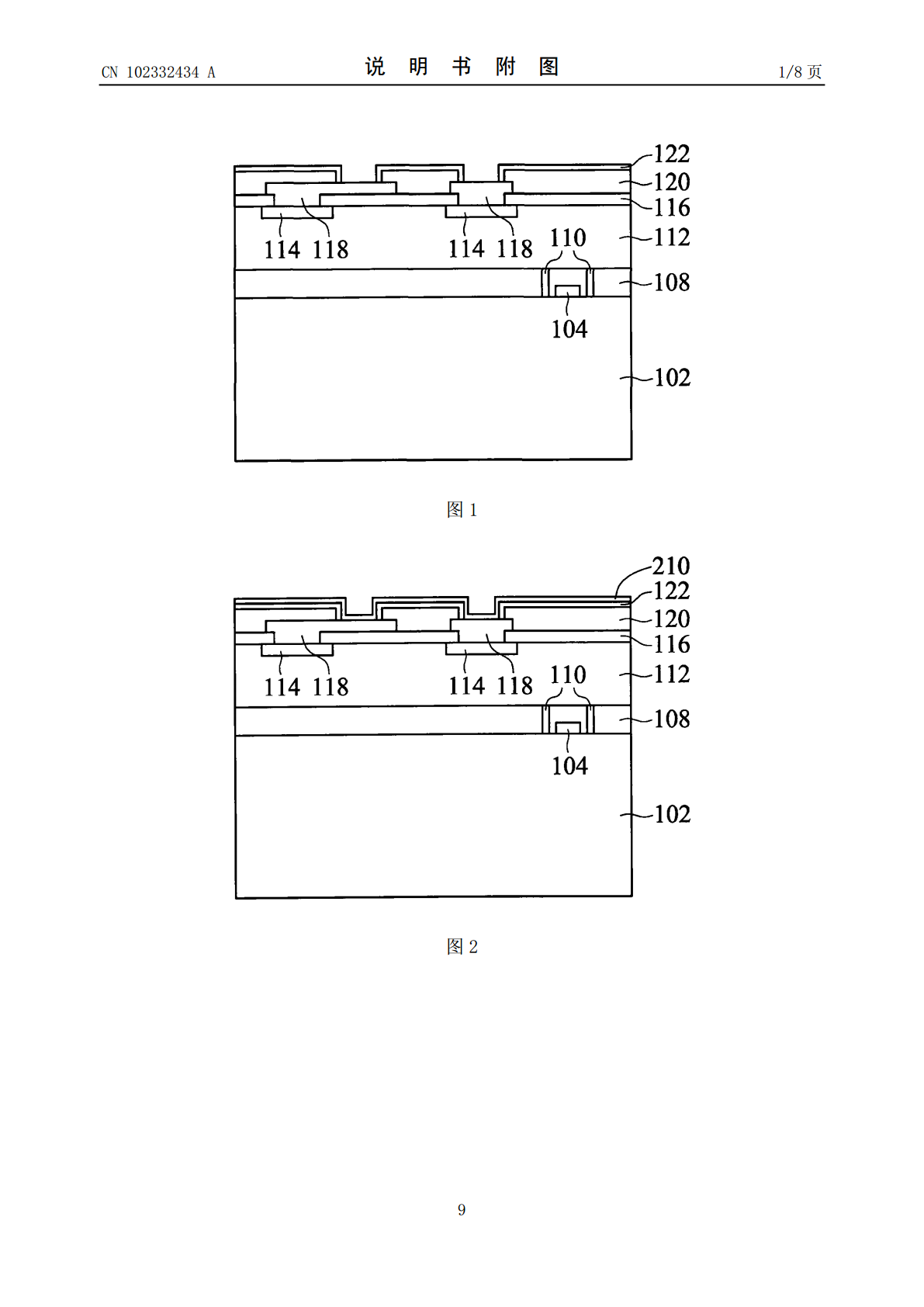

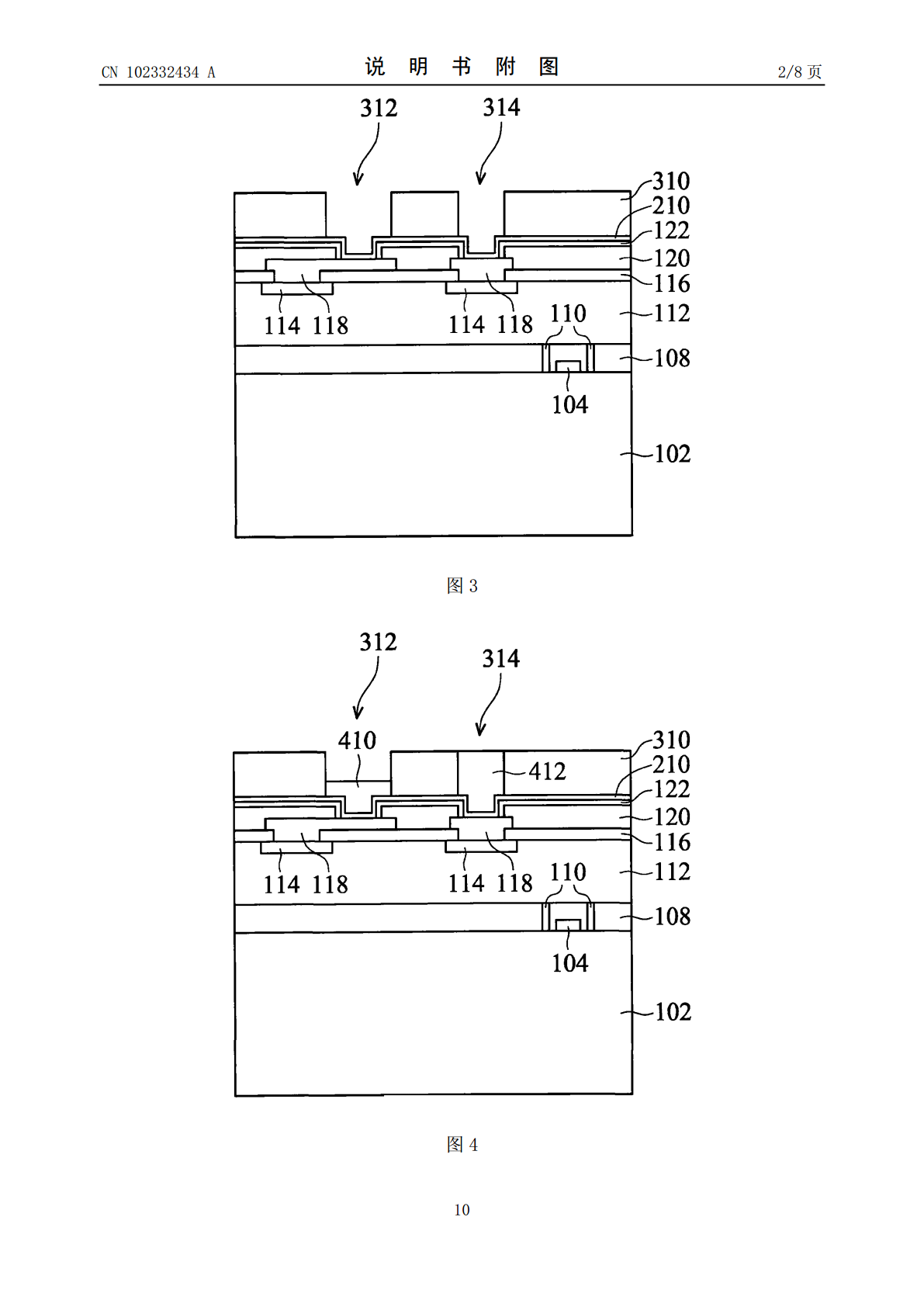

本发明公开了一种半导体结构及形成元件的方法。本发明提供用于半导体元件的基底支撑架,在第一基底上形成有源支柱与伪支柱,使得伪支柱的高度大于有源支柱的高度,当第一基底接合至第二基底时,使用伪支柱作为支撑架可产生较佳的均匀性。在一实施例中,借由图案化掩模的形成,可同时形成伪支柱与有源支柱,图案化掩模中用于伪支柱的开口的宽度小于有源支柱。当使用类似电镀的工艺形成伪支柱与有源支柱时,因为图案化掩模中伪支柱开口的宽度较小,使得伪支柱的高度大于有源支柱。本发明不会发生沿着支柱结构侧边的焊锡润湿现象。

半导体结构、半导体元件及其形成方法.pdf

本发明公开了一种半导体结构、半导体元件及其形成方法。半导体元件包含两个彼此横向连接的半导体结构,且各半导体结构包含半导体基板以及第一导电凸块。半导体基板具有集成电路以及互连金属层,其中斜角表面形成在半导体基板的边缘上。第一导电凸块经由互连金属层电性连接至集成电路,并位于斜角表面上,其中第一导电凸块的轮廓延伸超出半导体基板的边缘的侧表面。此两个半导体结构通过其相接合的第一导电凸块横向连接。本发明的半导体元件,能够建立与导电凸块的横向连接,以节省成本。

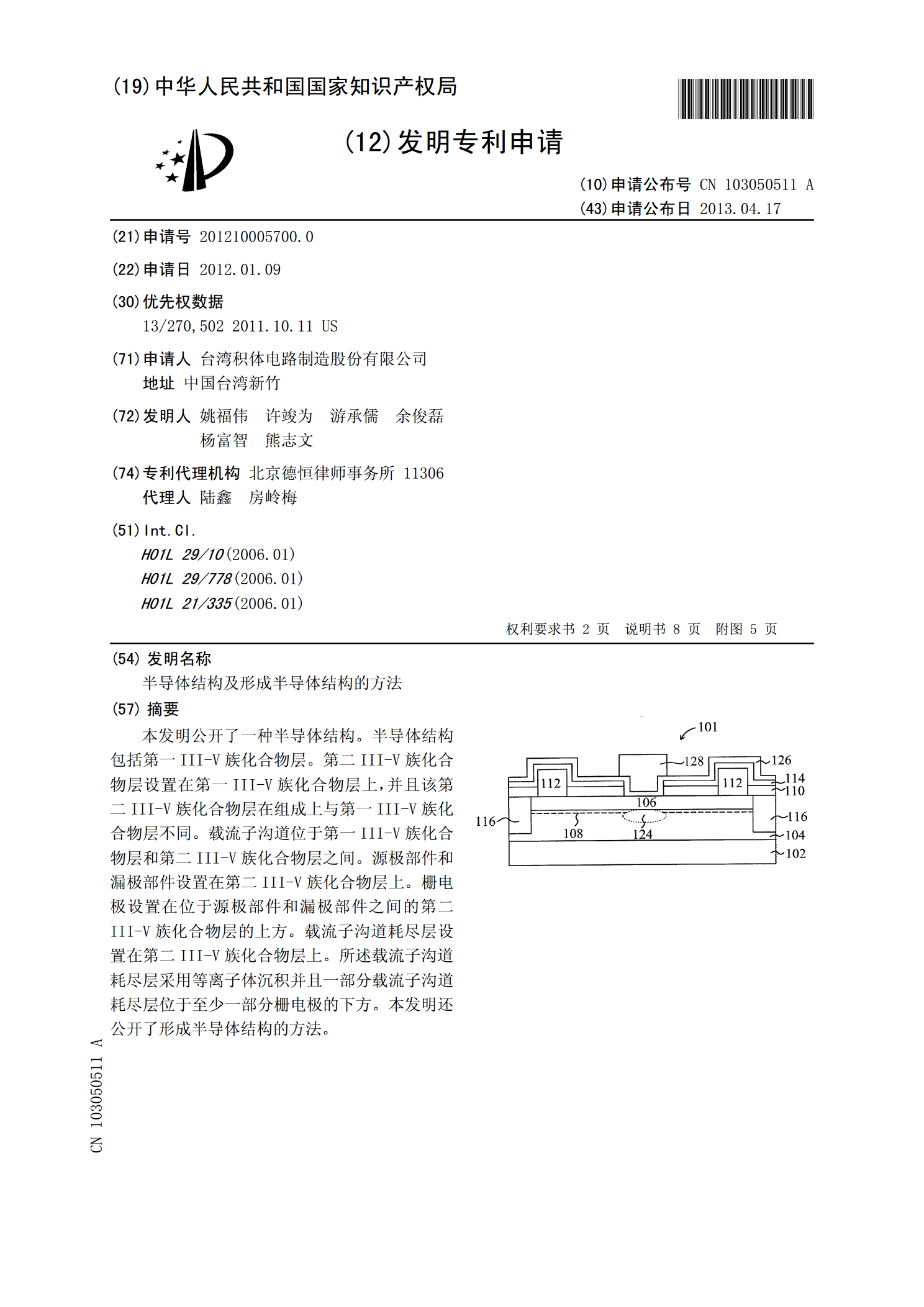

半导体结构及形成半导体结构的方法.pdf

本发明公开了一种半导体结构。半导体结构包括第一III-V族化合物层。第二III-V族化合物层设置在第一III-V族化合物层上,并且该第二III-V族化合物层在组成上与第一III-V族化合物层不同。载流子沟道位于第一III-V族化合物层和第二III-V族化合物层之间。源极部件和漏极部件设置在第二III-V族化合物层上。栅电极设置在位于源极部件和漏极部件之间的第二III-V族化合物层的上方。载流子沟道耗尽层设置在第二III-V族化合物层上。所述载流子沟道耗尽层采用等离子体沉积并且一部分载流子沟道耗尽层位于至少

半导体元件的形成方法.pdf

一种半导体元件的形成方法,包含在穿过介电质层的开口的底面上形成第一导电特征。形成第一导电特征留下晶种在开口的侧壁上。对晶种执行处理制程以形成经处理晶种。经处理晶种通过清洁制程去除。清洁制程可以包含用去离子水冲洗。形成第二导电特征以填充开口。

半导体元件的形成方法.pdf

本发明提供在半导体元件的制造过程中移除硬掩模的方法,该方法包括如下步骤:于基底上的结构之上形成保护层,例如为底部抗反射涂层或其他介电层,并沿着结构的侧边形成间隙壁。在一实施例中,这些结构为栅极电极,具有硬掩模形成于其上,以及间隙壁沿着栅极电极的侧边形成。在保护层之上形成光致抗蚀剂层,且光致抗蚀剂层可以被图案化,以移除在部分保护层上的光致抗蚀剂层的一部分,之后进行回蚀工艺,使得邻接间隙壁的保护层残留以保护间隙壁,然后当保护层保护间隙壁时移除硬掩模。本发明有利于形成的元件的操作。