一种LED芯片及其制备方法.pdf

景山****魔王

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种LED芯片及其制备方法.pdf

本发明公开了一种LED芯片及其制备方法,在N型半导体层远离衬底的一面沉积绝缘层,且绝缘层围绕量子阱层、P型半导体层以及N电极设置,因此在PN分界处优先覆盖绝缘材料,能够在Mesa刻蚀之后ITO层溅射之前生成绝缘层,减少PN分界处因ITO导电物质产生的微漏电;并且通过设置绝缘层,相较于现有技术能够提高ITO层的面积,增加发光效率并提高芯片亮度,同时在应用端也能充分避免PN分界处的其他导电杂质驻留。

一种LED芯片及其制备方法.pdf

本发明公开了一种LED芯片及其制备方法,所述LED芯片包括N电极,所述N电极包括相互连接的N电极主体部分和N电极延伸部分,且在所述N电极延伸部分对应区域的LED外延结构中至少设置有两个开口,所述开口依次贯穿所述P型外延层和量子阱层,直至暴露出N型外延层,所述N电极延伸部分覆盖暴露的N型外延层以及覆盖形成于所述开口的侧壁和保留的P型外延层的表面的绝缘层。则本发明的所述N电极延伸部分的下方保留了区域性的外延层,相当于增大了LED芯片的发光面积,从而能够增加LED芯片的发光亮度。

一种LED芯片及其制备方法.pdf

本发明提供了一种LED芯片及其制备方法,该LED芯片包括依次层叠的衬底和外延层,所述LED芯片还包括设于所述外延层上的电流阻挡层和第一电极,所述电流阻挡层为环状结构,且所述电流阻挡层的内环呈水波纹状设置,所述第一电极的一端插入所述电流阻挡层的中心部位,以使所述第一电极的侧壁与所述电流阻挡层的内环接触,所述第一电极的底部与所述外延层接触。通过本申请,不仅提升第一电极外围的承压能力,提升了推力值,有效改善了第一电极在焊线受压时会破裂、撕金的问题,还能提升LED芯片的成品率。

LED芯片及其制备方法.pdf

本发明涉及一种LED芯片及其制备方法。LED芯片设置有将芯片主体至少部分包覆的阻挡层,以及将阻挡层包覆的第一钝化层,阻挡层可阻挡第一钝化层中氯离子进入芯片主体,且保留在第一钝化层中的氯离子可与外部进入的金属离子结合,避免金属离子从LED芯片外界透过钝化层到达芯片主体,从而对芯片主体进行有效的保护。因此上述LED芯片的第一钝化层抗金属离子污染的能力得到明显提升,同时LED芯片的可靠性、质量以及良品率也都能得到明显的提升。

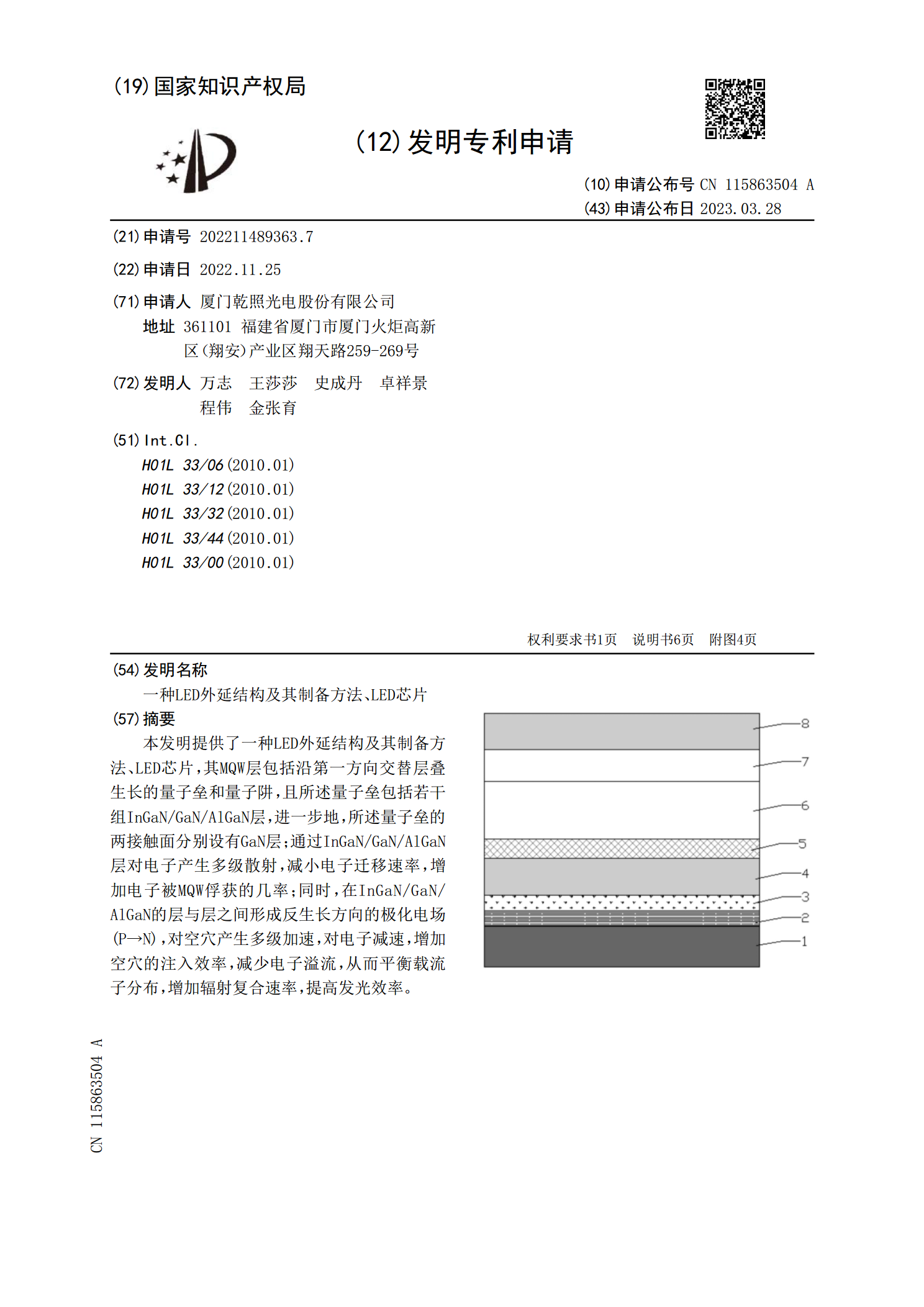

一种LED外延结构及其制备方法、LED芯片.pdf

本发明提供了一种LED外延结构及其制备方法、LED芯片,其MQW层包括沿第一方向交替层叠生长的量子垒和量子阱,且所述量子垒包括若干组InGaN/GaN/AlGaN层,进一步地,所述量子垒的两接触面分别设有GaN层;通过InGaN/GaN/AlGaN层对电子产生多级散射,减小电子迁移速率,增加电子被MQW俘获的几率;同时,在InGaN/GaN/AlGaN的层与层之间形成反生长方向的极化电场(P→N),对空穴产生多级加速,对电子减速,增加空穴的注入效率,减少电子溢流,从而平衡载流子分布,增加辐射复合速率,提高