半导体结构的互连方法与半导体互连结构.pdf

含秀****66

亲,该文档总共20页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体结构的互连方法与半导体互连结构.pdf

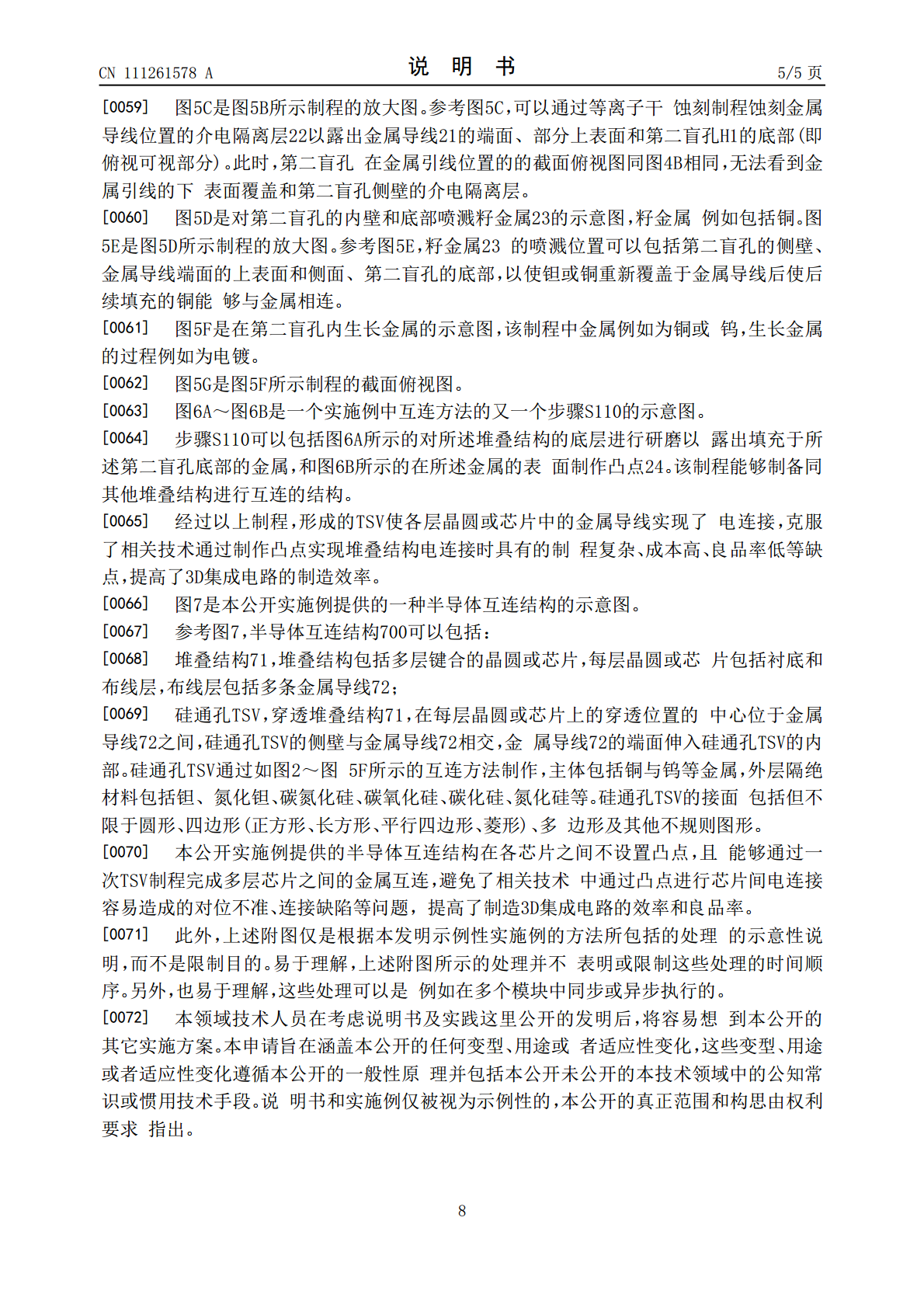

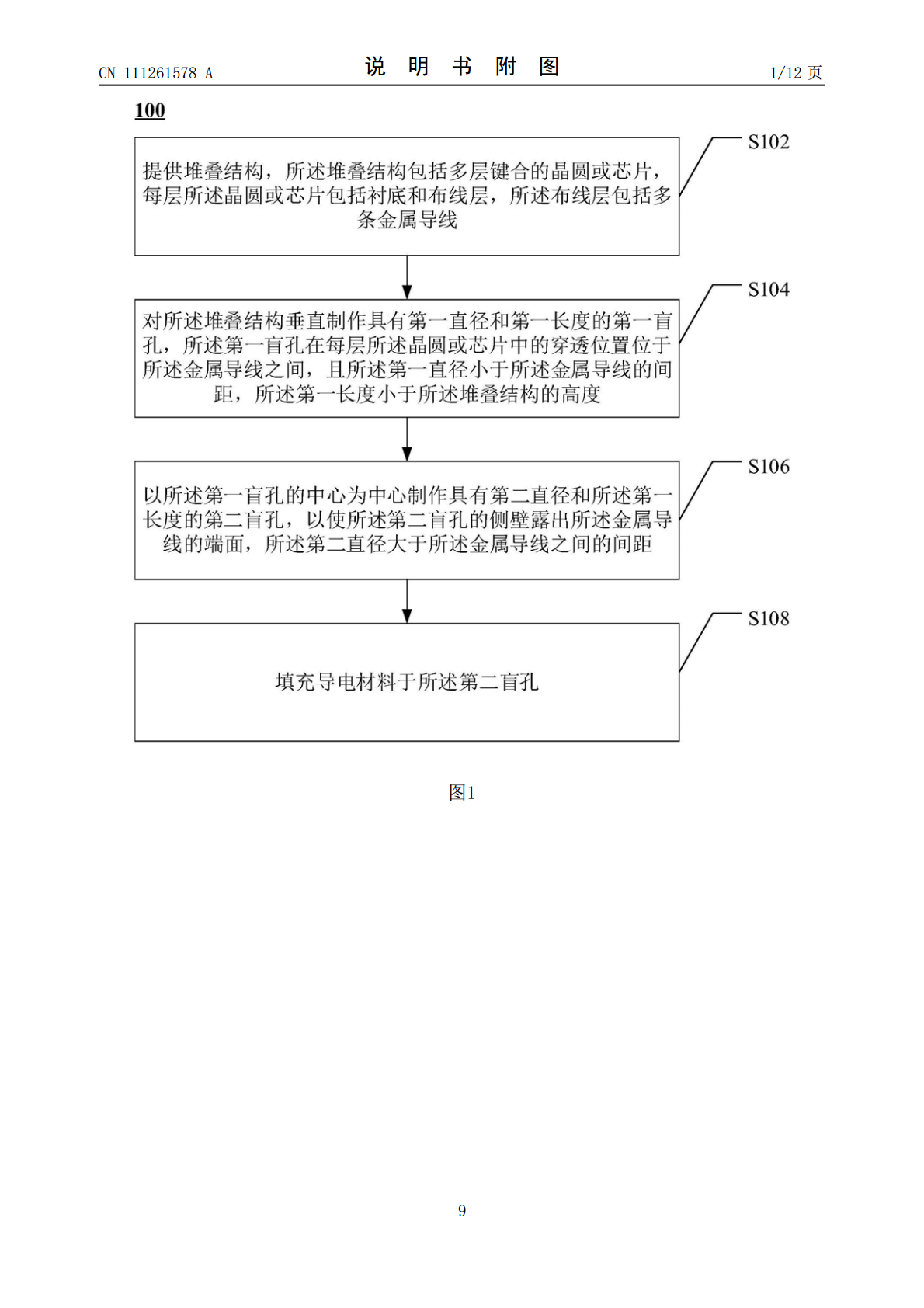

本公开提供一种用于半导体互连结构的互连方法与半导体互连结构。互连方法包括:提供堆叠结构,堆叠结构包括多层键合的晶圆,每层晶圆的上表面设置有重布线层,重布线层包括多条金属导线;对堆叠结构垂直制作具有第一直径和第一长度的第一盲孔,第一盲孔在每层晶圆中的穿透位置位于金属导线之间,且第一直径小于金属导线的间距;以第一盲孔的中心为圆心制作具有第二直径和第一长度的第二盲孔,以使第二盲孔的侧壁露出金属导线,第二直径大于金属导线之间的间距;填充导电材料于第二盲孔。本公开的互连方法可以通过一次掩模刻蚀制程制作使堆叠结构中各

互连结构、具有互连结构的半导体器件及其制造方法.pdf

本公开涉及一种互连结构、具有互连结构的半导体器件及其制造方法。本公开的各个实施例通过经由单个间隙填充处理同时形成延各个方向延伸的互连件来提高半导体器件的集成度。本发明的实施例提供了一种能够简化半导体处理的互连结构、包括该互连结构的半导体器件以及用于制造该半导体器件的方法。根据本公开的一个实施例,一种互连结构包括:多个互连件的堆叠,其中,多个互连件中的至少两层沿不同方向延伸,并且至少两层的下部互连件的上表面的一部分与至少两层的上部互连件的下表面的一部分直接接触。

互连结构及其制造方法以及使用互连结构的半导体器件.pdf

一种半导体器件包括半导体衬底、存在于半导体衬底中的接触区和位于接触区的纹理化的表面上的硅化物。多个溅射残留物存在于硅化物和接触区之间。由于接触区的表面被纹理化,因此由硅化物提供的接触面积相应的增加,从而降低了半导体器件中的互连结构的电阻。本发明实施例涉及互连结构及其制造方法以及使用互连结构的半导体器件。

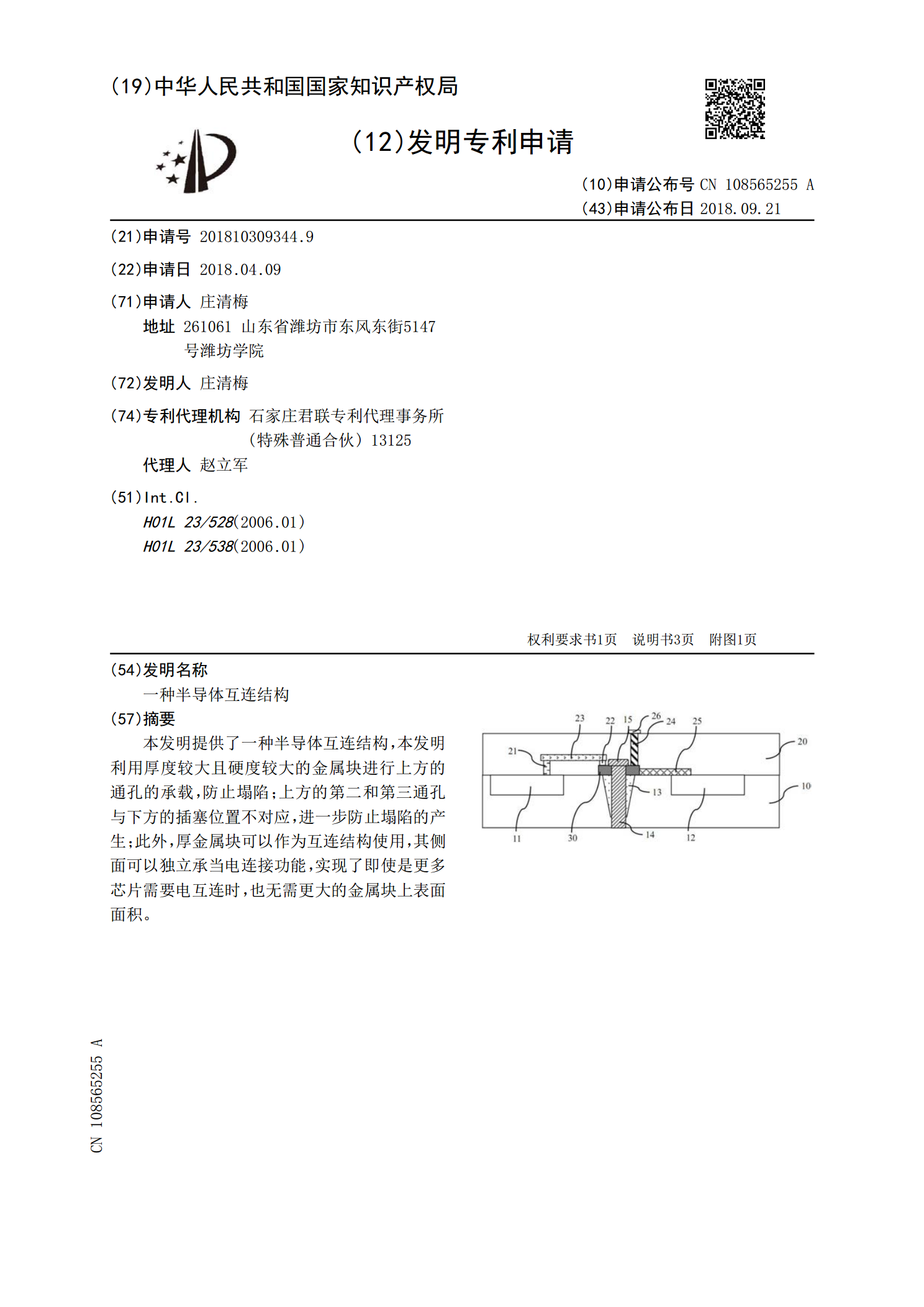

一种半导体互连结构.pdf

本发明提供了一种半导体互连结构,本发明利用厚度较大且硬度较大的金属块进行上方的通孔的承载,防止塌陷;上方的第二和第三通孔与下方的插塞位置不对应,进一步防止塌陷的产生;此外,厚金属块可以作为互连结构使用,其侧面可以独立承当电连接功能,实现了即使是更多芯片需要电互连时,也无需更大的金属块上表面面积。

具有光学互连结构的半导体封装.pdf

具有光学互连结构的半导体封装。一种半导体封装包括设置在基板的顶表面上的第一收发器;以及设置在所述基板的底表面上的第二收发器。所述第一和第二收发器通过穿透基板的光信号彼此光学通信。