高密度互连印刷电路板的制造顺序及高密度互连印刷电路板.pdf

一吃****春艳

亲,该文档总共31页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

高密度互连印刷电路板的制造顺序及高密度互连印刷电路板.pdf

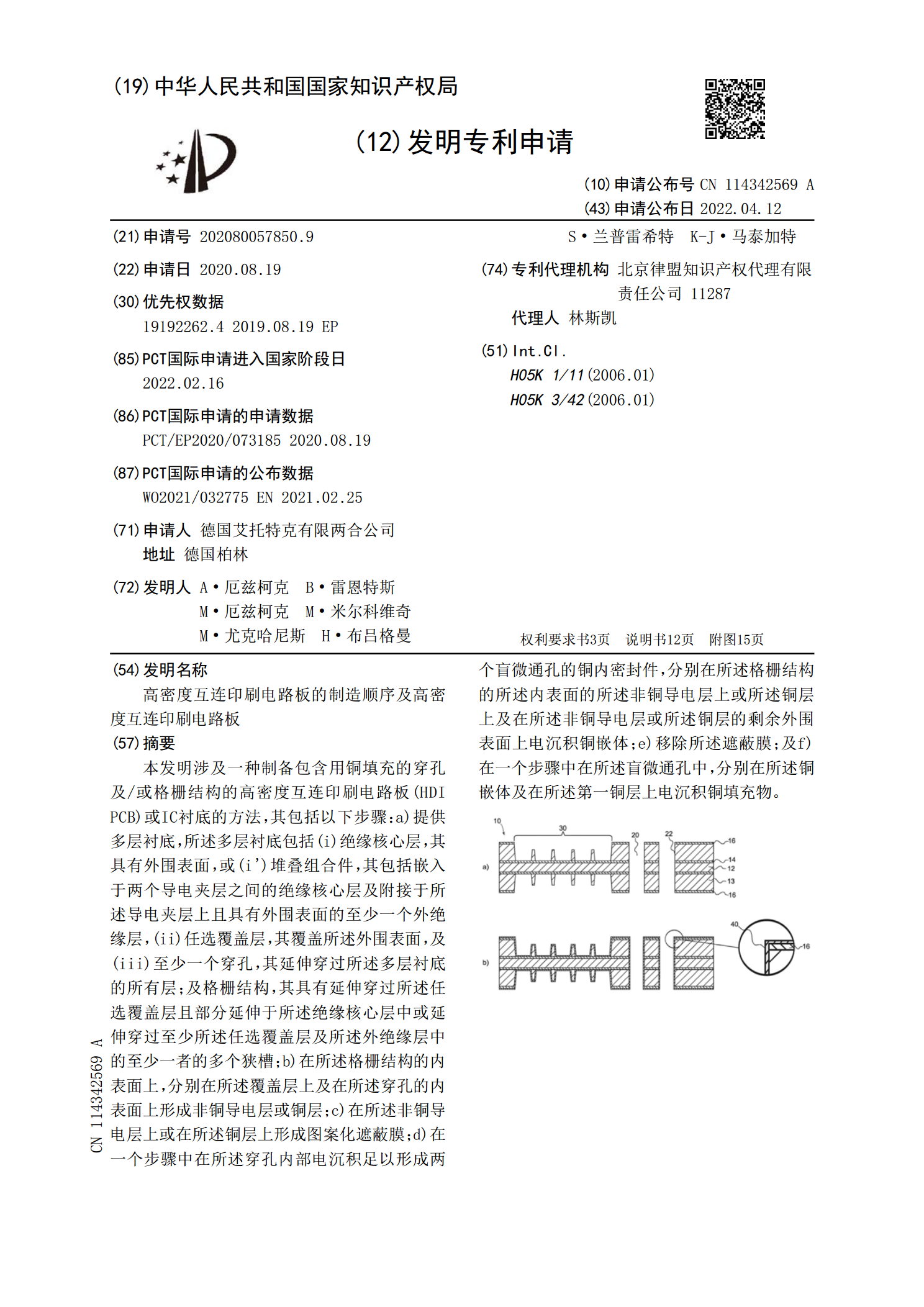

本发明涉及一种制备包含用铜填充的穿孔及/或格栅结构的高密度互连印刷电路板(HDIPCB)或IC衬底的方法,其包括以下步骤:a)提供多层衬底,所述多层衬底包括(i)绝缘核心层,其具有外围表面,或(i')堆叠组合件,其包括嵌入于两个导电夹层之间的绝缘核心层及附接于所述导电夹层上且具有外围表面的至少一个外绝缘层,(ii)任选覆盖层,其覆盖所述外围表面,及(iii)至少一个穿孔,其延伸穿过所述多层衬底的所有层;及格栅结构,其具有延伸穿过所述任选覆盖层且部分延伸于所述绝缘核心层中或延伸穿过至少所述任选覆盖层及所述

高密度互连电路板.pdf

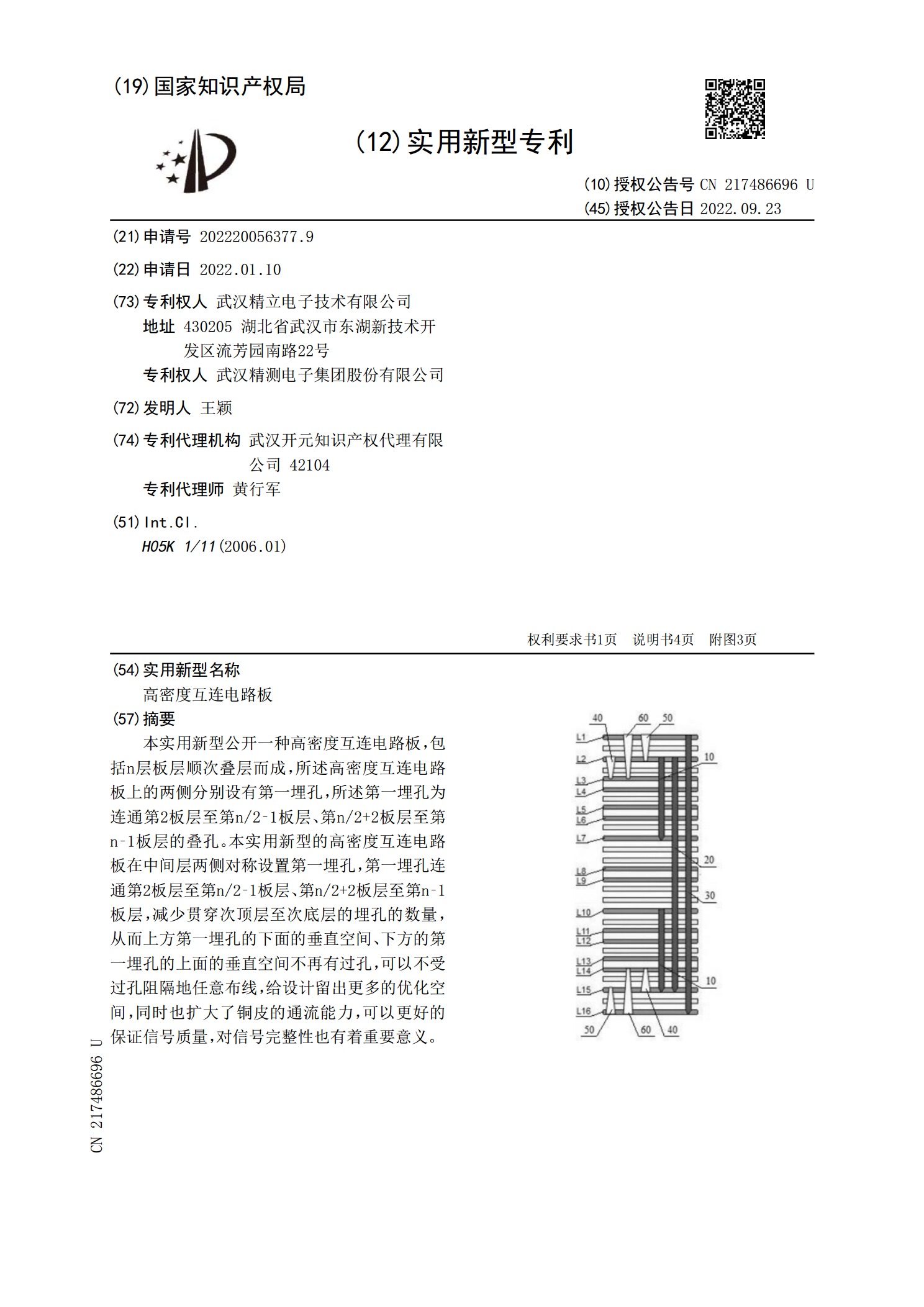

本实用新型公开一种高密度互连电路板,包括n层板层顺次叠层而成,所述高密度互连电路板上的两侧分别设有第一埋孔,所述第一埋孔为连通第2板层至第n/2?1板层、第n/2+2板层至第n?1板层的叠孔。本实用新型的高密度互连电路板在中间层两侧对称设置第一埋孔,第一埋孔连通第2板层至第n/2?1板层、第n/2+2板层至第n?1板层,减少贯穿次顶层至次底层的埋孔的数量,从而上方第一埋孔的下面的垂直空间、下方的第一埋孔的上面的垂直空间不再有过孔,可以不受过孔阻隔地任意布线,给设计留出更多的优化空间,同时也扩大了铜皮的通流

高密度互连印刷线路板制造方法.pdf

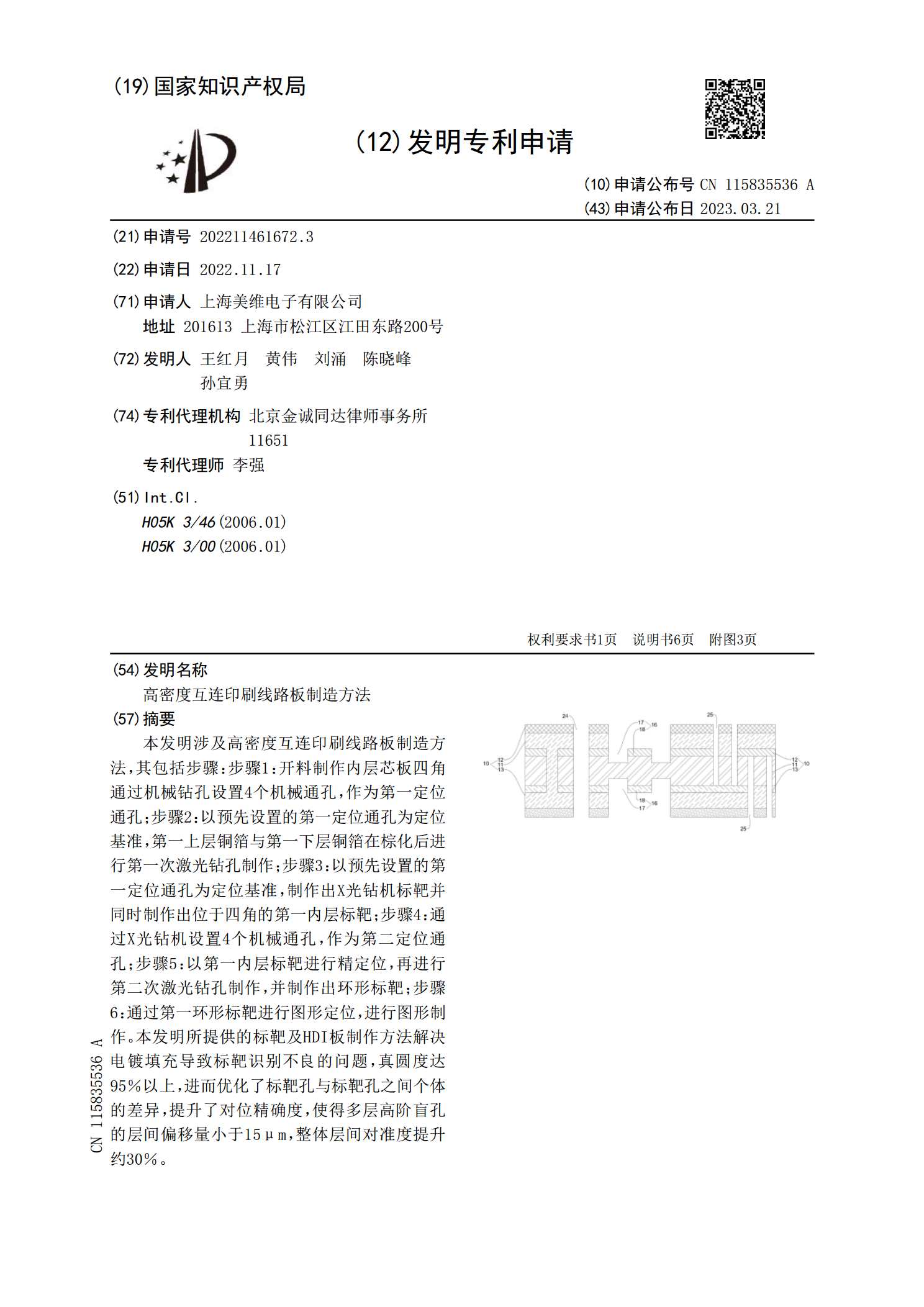

本发明涉及高密度互连印刷线路板制造方法,其包括步骤:步骤1:开料制作内层芯板四角通过机械钻孔设置4个机械通孔,作为第一定位通孔;步骤2:以预先设置的第一定位通孔为定位基准,第一上层铜箔与第一下层铜箔在棕化后进行第一次激光钻孔制作;步骤3:以预先设置的第一定位通孔为定位基准,制作出X光钻机标靶并同时制作出位于四角的第一内层标靶;步骤4:通过X光钻机设置4个机械通孔,作为第二定位通孔;步骤5:以第一内层标靶进行精定位,再进行第二次激光钻孔制作,并制作出环形标靶;步骤6:通过第一环形标靶进行图形定位,进行图形制

高密度互连印刷电路板上盲钻沉孔的加工工艺.pdf

本发明涉及一种高密度互连印刷电路板上盲钻沉孔的加工工艺,特征在于,包括以下工艺步骤:(1)使用上销钉机对待加工的印刷电路板进行上定位销钉;(2)使用自动贴胶机将与印刷电路板尺寸相同的铝片与印刷电路板固定在一起;(3)将步骤(2)得到的印刷电路板放在钻孔机台的夹销钉槽里,使印刷电路板固定在钻孔机台面上;(4)将盲钻钻孔机压力脚上的轴承更换成塑胶轴承;(5)启动盲钻钻孔机,对印刷电路板进行盲钻加工。本发明的实施可保证了印刷电路板上盲钻沉孔的精度品质的要求,也减少了不良品的发生,并且可有效的保护钻孔机的工作台面

高密度互连印刷电路板上盲捞沉孔的加工工艺.pdf

本发明涉及一种高密度互连印刷电路板上盲捞沉孔的加工工艺,特征在于,包括以下工艺步骤:(1)盲捞沉孔面积小于50×50mm,使用美工刀片将电木板上钻出销钉孔的火山口刮平;盲捞沉孔面积大于50×50mm,采用铣刀对整个电木板平面铣平;(2)把盲捞成型机上的压力脚毛刷更换成铁氟龙材质的毛刷;(3)把用于钻销钉孔的钻头插在刀座上,启动盲捞成型机,在成型机工作台面的电木板上钻出销钉孔;(4)选取4颗销钉插在电木板上的4颗销钉孔内,套上一片印刷电路板进行敲销钉;(5)将印刷电路板的四边固定;(6)调试盲捞深度,进行盲