一种集成肖特基二极管的屏蔽栅沟槽MOSFET的制作方法.pdf

Jo****63

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种集成肖特基二极管的屏蔽栅沟槽MOSFET的制作方法.pdf

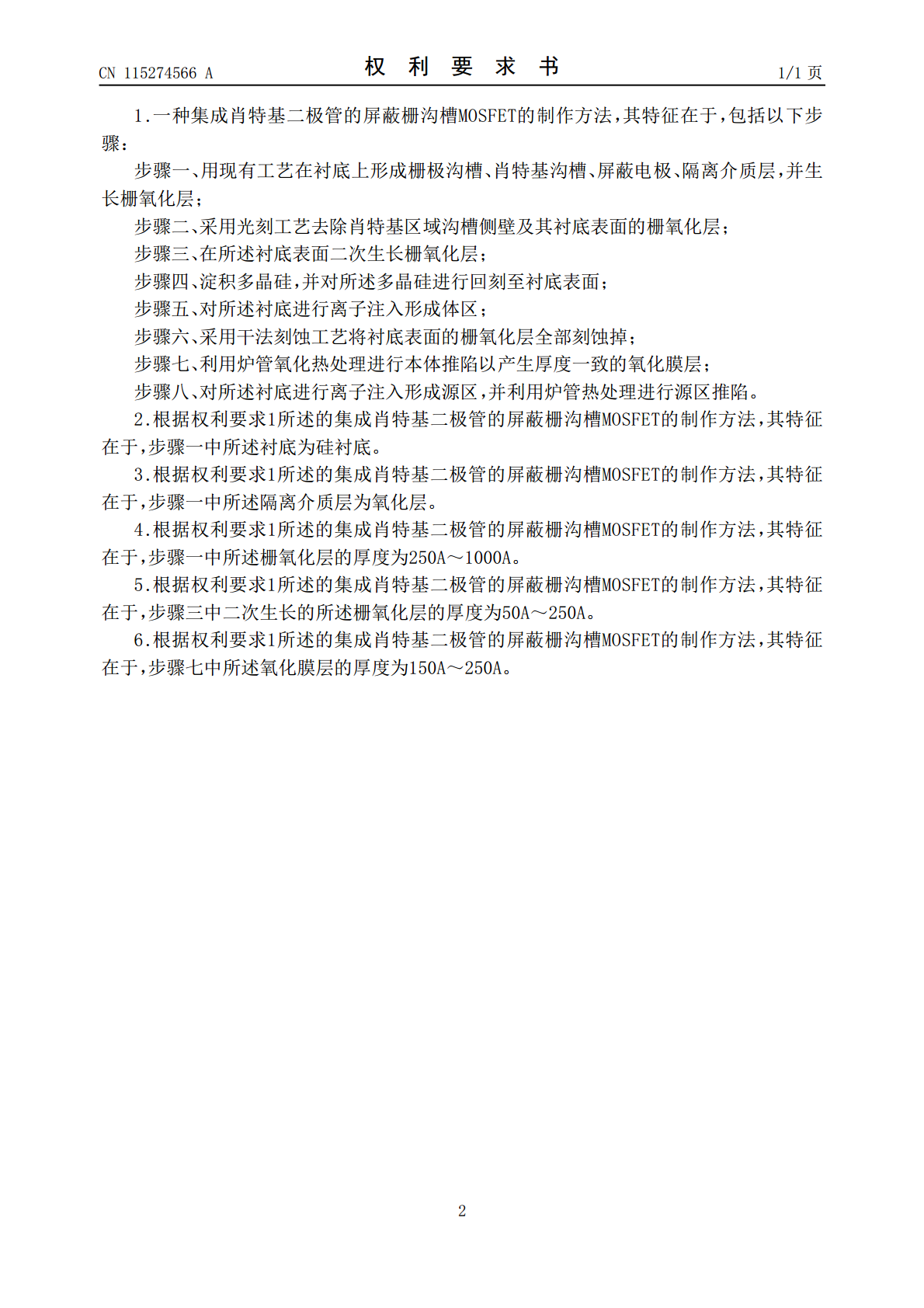

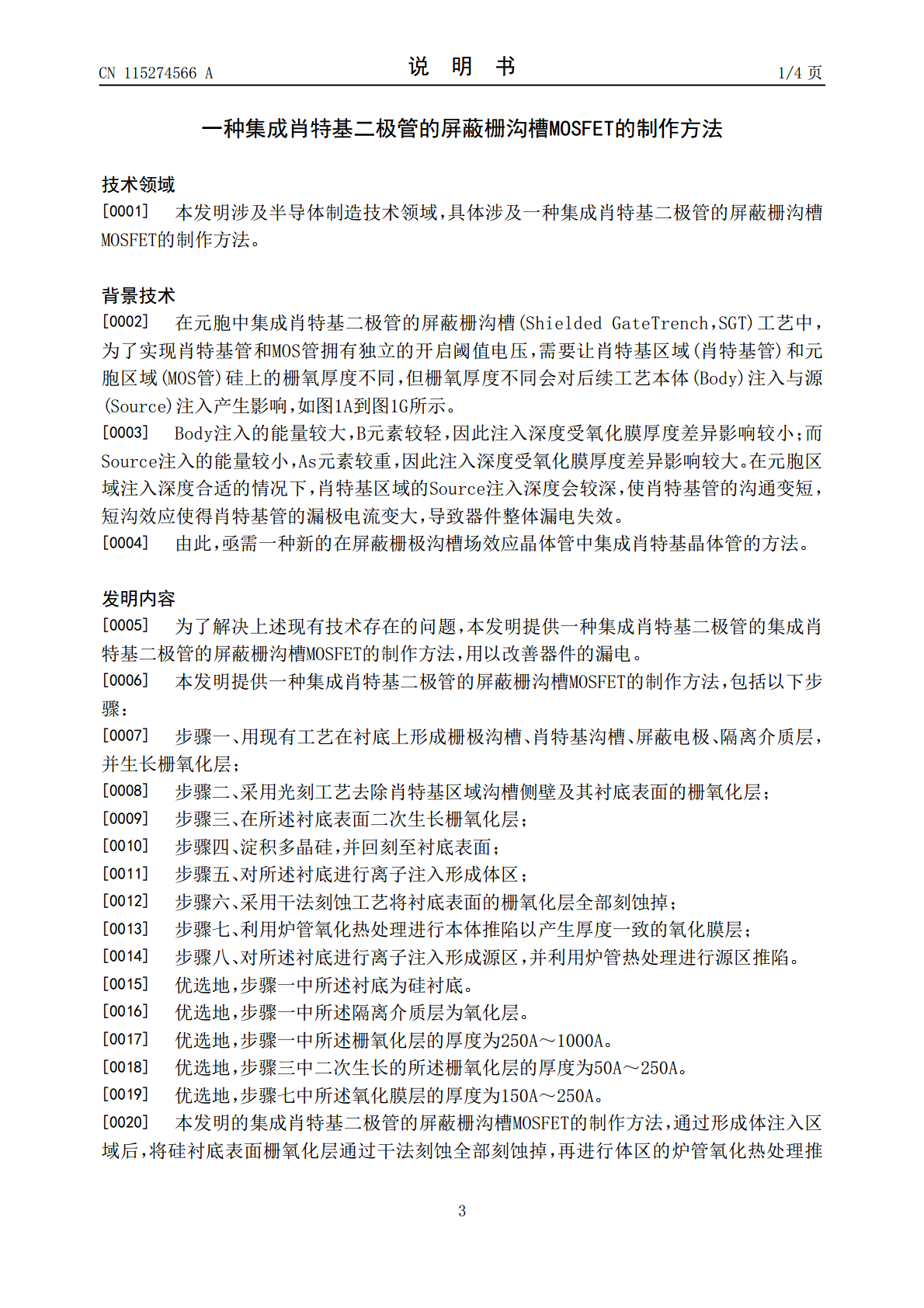

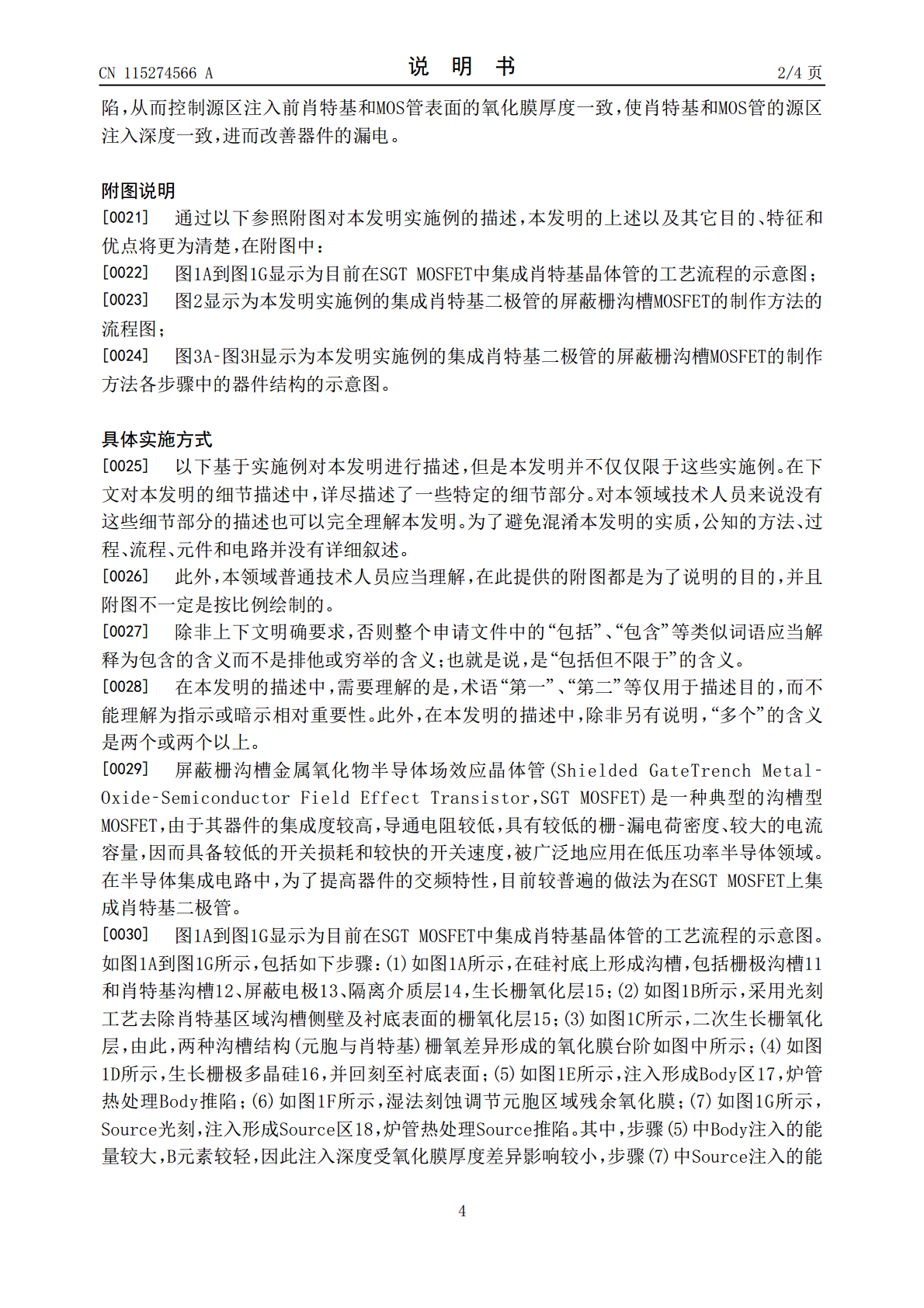

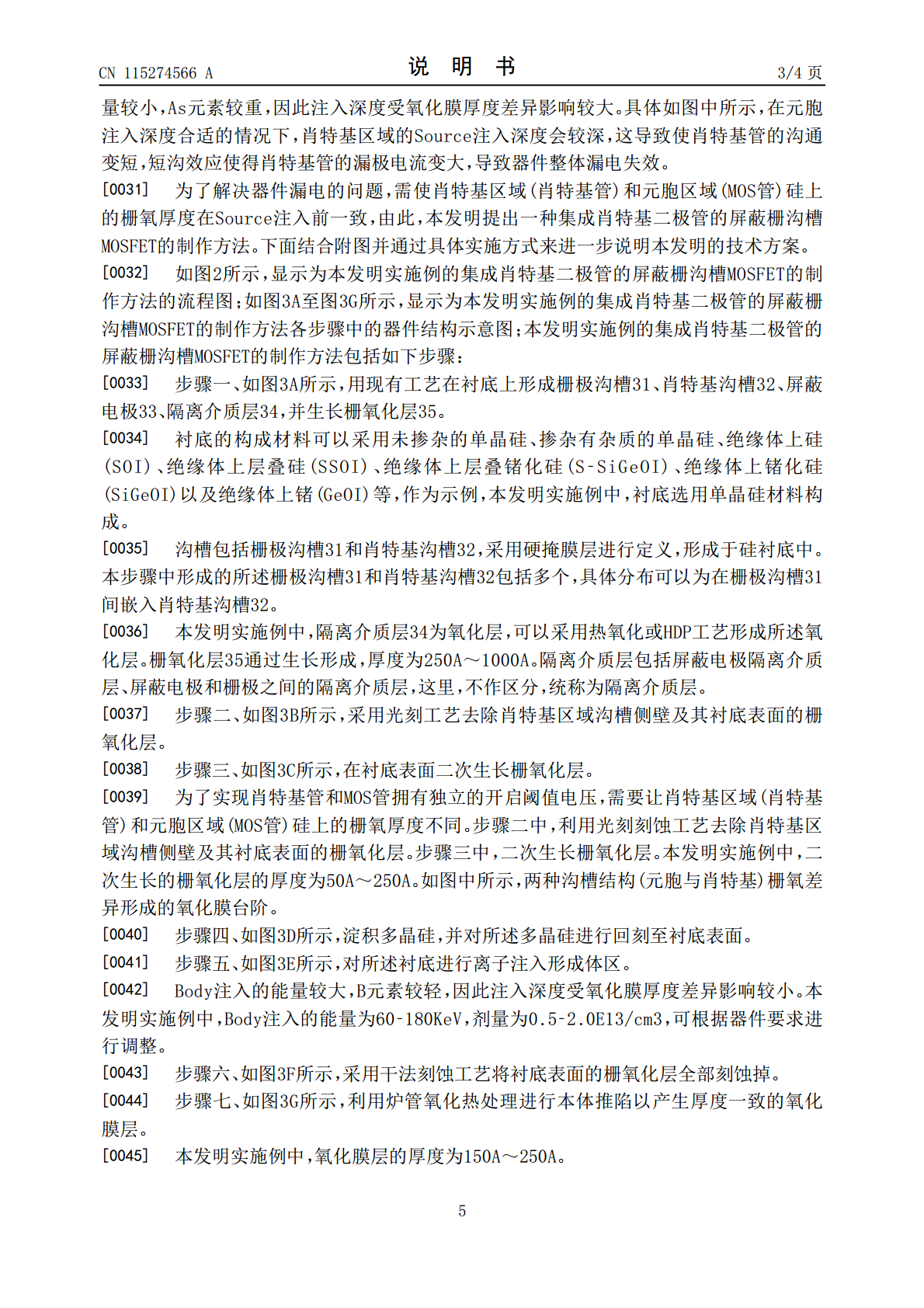

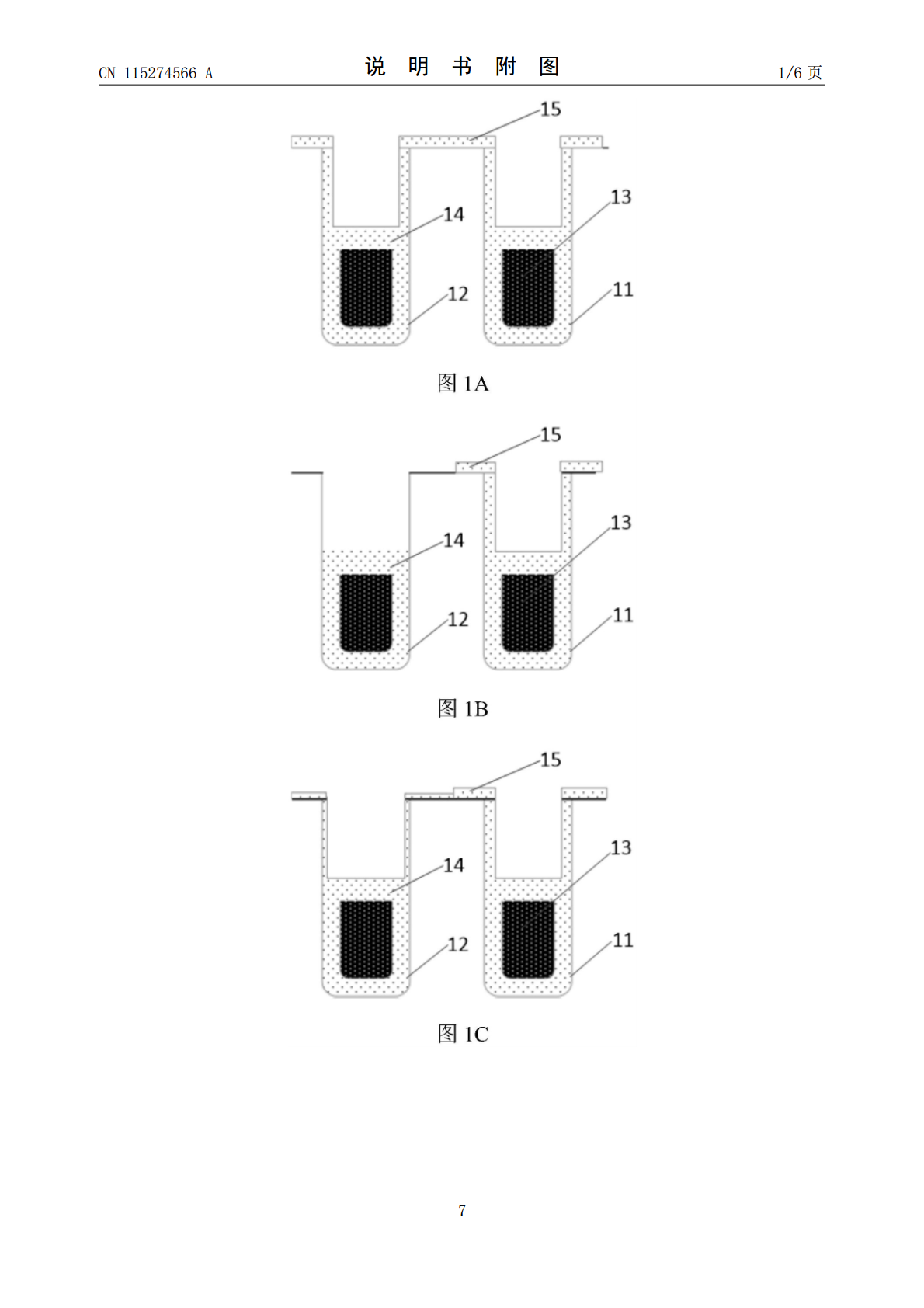

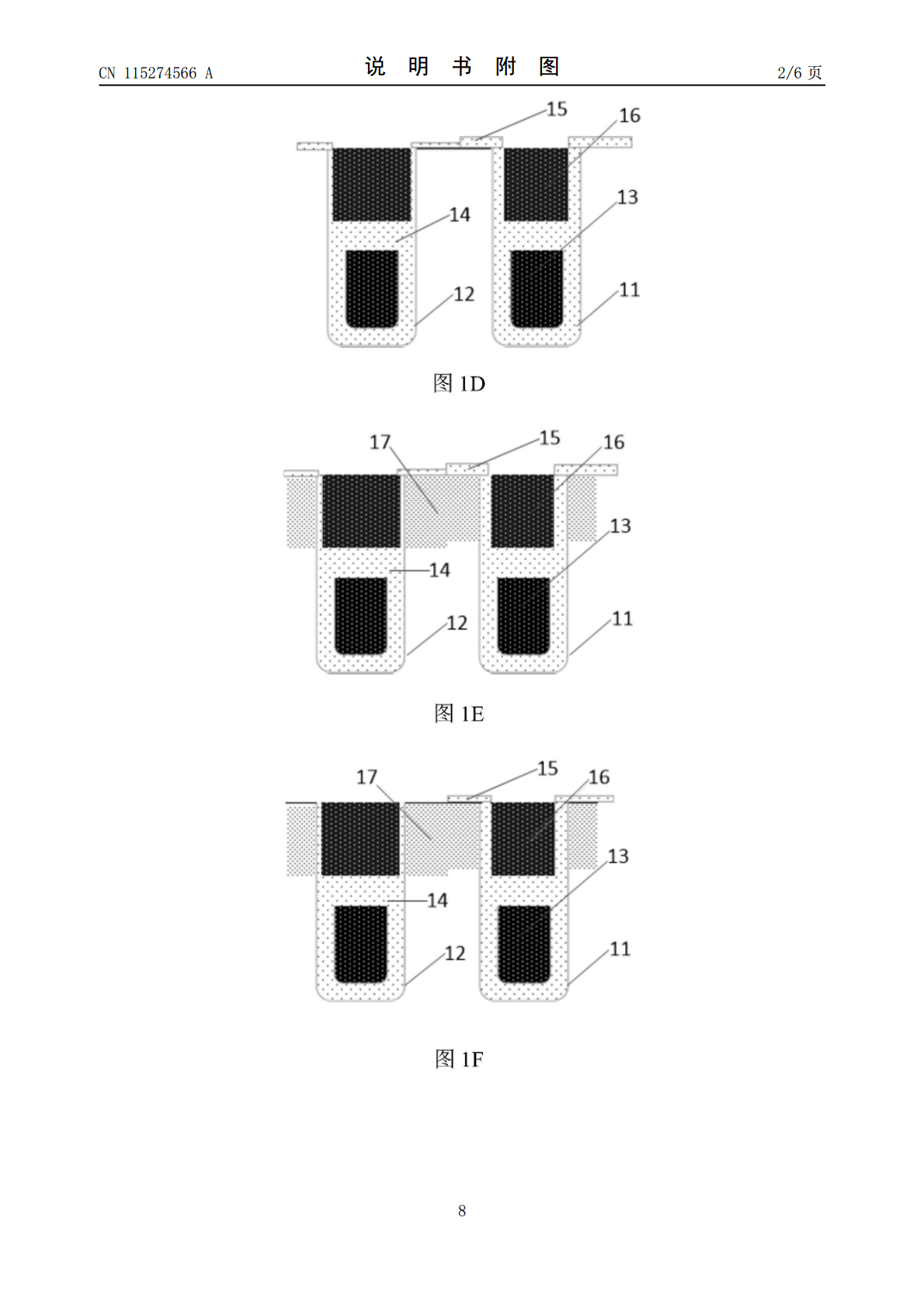

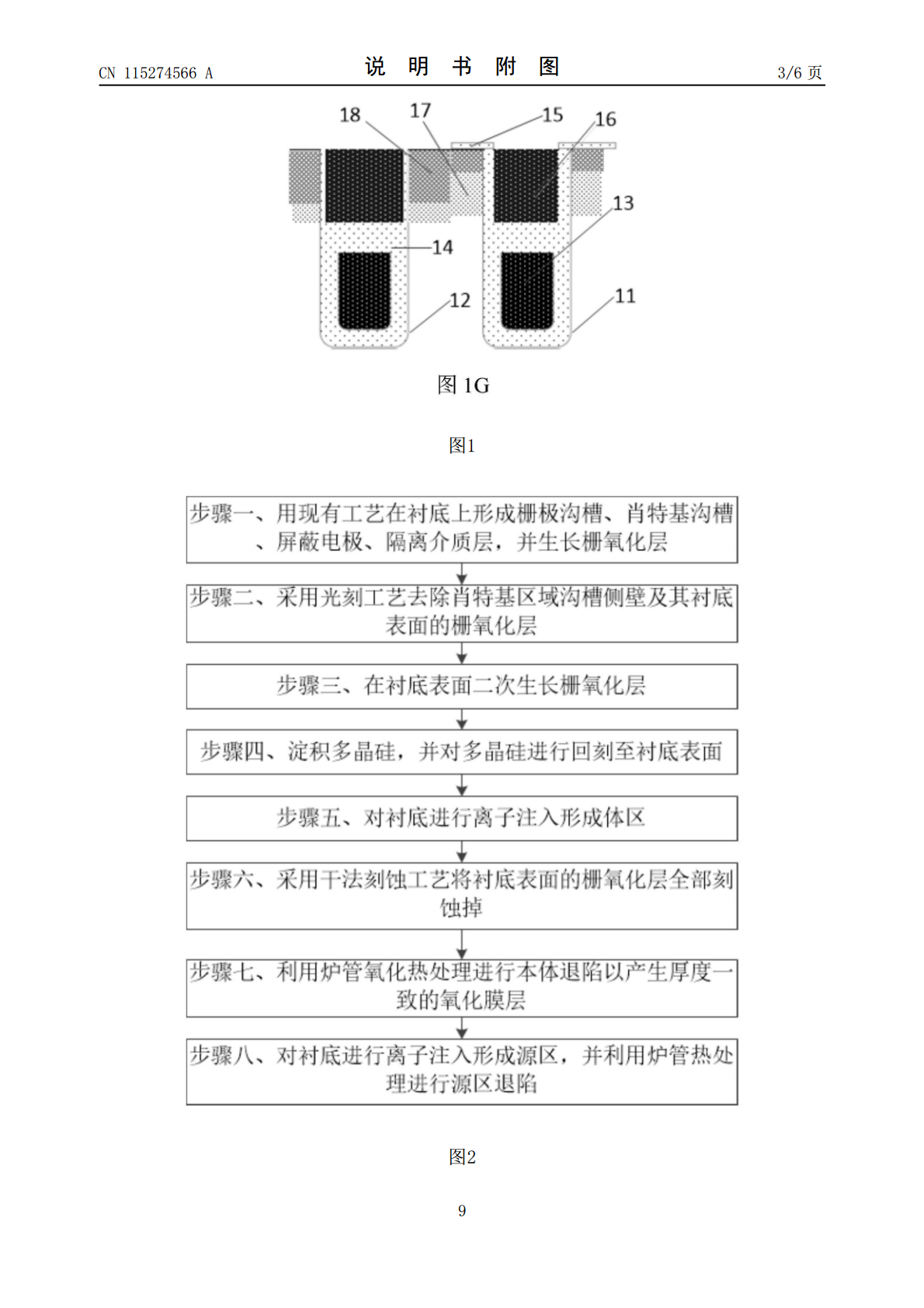

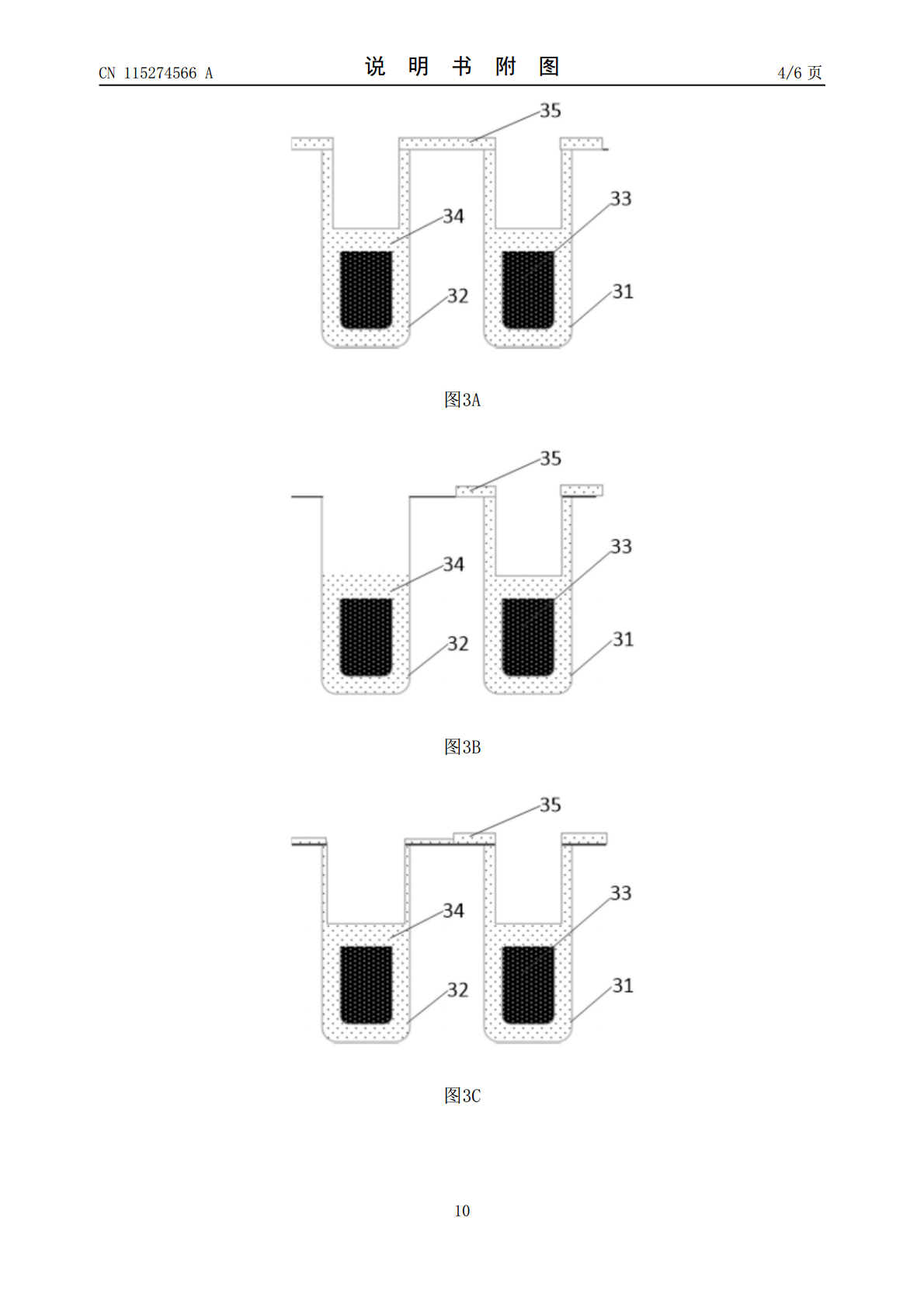

本发明提供一种集成肖特基二极管的屏蔽栅沟槽MOSFET的制作方法,用现有工艺在衬底上形成栅极沟槽、肖特基沟槽、屏蔽电极、隔离介质层,并生长栅氧化层;采用光刻工艺去除肖特基区域沟槽侧壁及其衬底表面的栅氧化层;在衬底表面二次生长栅氧化层;淀积多晶硅,并回刻至衬底表面;对衬底进行离子注入形成体区;采用干法刻蚀工艺将衬底表面的栅氧化层全部刻蚀掉;利用炉管氧化热处理进行本体推陷以产生厚度一致的氧化膜层;对衬底进行离子注入形成源区,并利用炉管热处理进行源区推陷。本发明将衬底表面栅氧化层刻蚀光,再进行带氧化体区的炉管热

一种屏蔽栅沟槽MOSFET制造方法.pdf

本申请涉及一种屏蔽栅沟槽MOSFET制造方法,在外延层的沟槽侧壁生长屏蔽栅氧化层,然后填充屏蔽栅多晶硅,将屏蔽栅多晶硅回刻至第一目标深度;淀积目标厚度T的氮化硅层,以形成隔离屏蔽栅多晶硅和器件栅极的介质隔离层,氮化硅层回刻至外延层表面处;刻蚀屏蔽栅氧化层至第二目标深度,蚀刻氮化硅层至第一目标厚度K,使得氮化硅层上表面伸出屏蔽栅氧化层表面;生长栅氧化层,淀积栅极多晶硅,蚀刻栅极多晶硅至第三目标深度,以形成屏蔽栅沟槽MOSFET,本申请具有结构稳定、生产效率高、成本低等优点。

屏蔽栅沟槽型MOSFET的制造方法.pdf

本发明公开了一种屏蔽栅沟槽型MOSFET的制造方法,包括如下步骤:步骤一、提供表面形成有硅外延层的硅衬底并进行光刻刻蚀形成沟槽;步骤二、形成底部氧化层;步骤三、形成第一层多晶硅将沟槽完全填充;步骤四、进行热退火,利用热退火使第一层多晶硅再结晶并消除第一层多晶硅的缝隙;步骤五、对第一层多晶硅进行回刻并形成由保留于沟槽底部的第一层多晶硅组成多晶硅屏蔽栅。本发明能提高多晶硅屏蔽栅的表面形貌,进而提高多晶硅屏蔽栅的表面深度的均匀性,提高多晶硅屏蔽栅的屏蔽效果。

一种屏蔽栅沟槽MOSFET及其制造方法.pdf

本申请公开了一种屏蔽栅沟槽MOSFET及其制造方法,属于集成电路领域。该屏蔽栅沟槽MOSFET主要包括:衬底片;外延层,其生长在衬底片上;硬掩膜,其通过在外延层上淀积氧化硅形成,并在形成深沟槽后移除;深沟槽,其利用沟槽掩膜版在硬掩膜上刻蚀外延层得到;场介质层,其生长在深沟槽的表面且与述源极多晶硅的表面平齐;源极多晶硅,其填充在深沟槽内的场介质层上;栅极沟槽,其利用有源区掩膜版在场介质层表面刻蚀场介质层得到;栅极氧化硅,其通过在栅极沟槽表面氧化形成;栅极多晶硅,其在栅极沟槽的栅极氧化硅上淀积。本申请通过在栅

沟槽型双层栅MOSFET的制作方法.pdf

本发明公开了一种沟槽型双层栅MOSFET的制作方法,步骤包括:1)刻蚀沟槽,生长ONO结构的沟槽层接膜;2)生长源极多晶硅,反刻蚀至沟槽上表面;3)用光刻胶保护源极多晶硅引出端,反刻蚀密集区的源极多晶硅;4)依次去除沟槽层接膜中的部分外层氧化硅膜、光刻胶、沟槽层接膜中的剩余外层氧化硅膜;5)生长多晶硅间的氧化层;6)去除沟槽层接膜中的氮化硅膜和内层氧化硅膜;7)依次生长栅极氧化层、栅极多晶硅,并反刻蚀栅极多晶硅,完成器件的制作。本发明通过优化沟槽层接膜去除工艺和减少源极多晶硅的氧化量,改善了源极多晶硅引出