半导体器件及其制作方法以及CMOS图像传感器.pdf

和裕****az

亲,该文档总共25页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体器件及其制作方法以及CMOS图像传感器.pdf

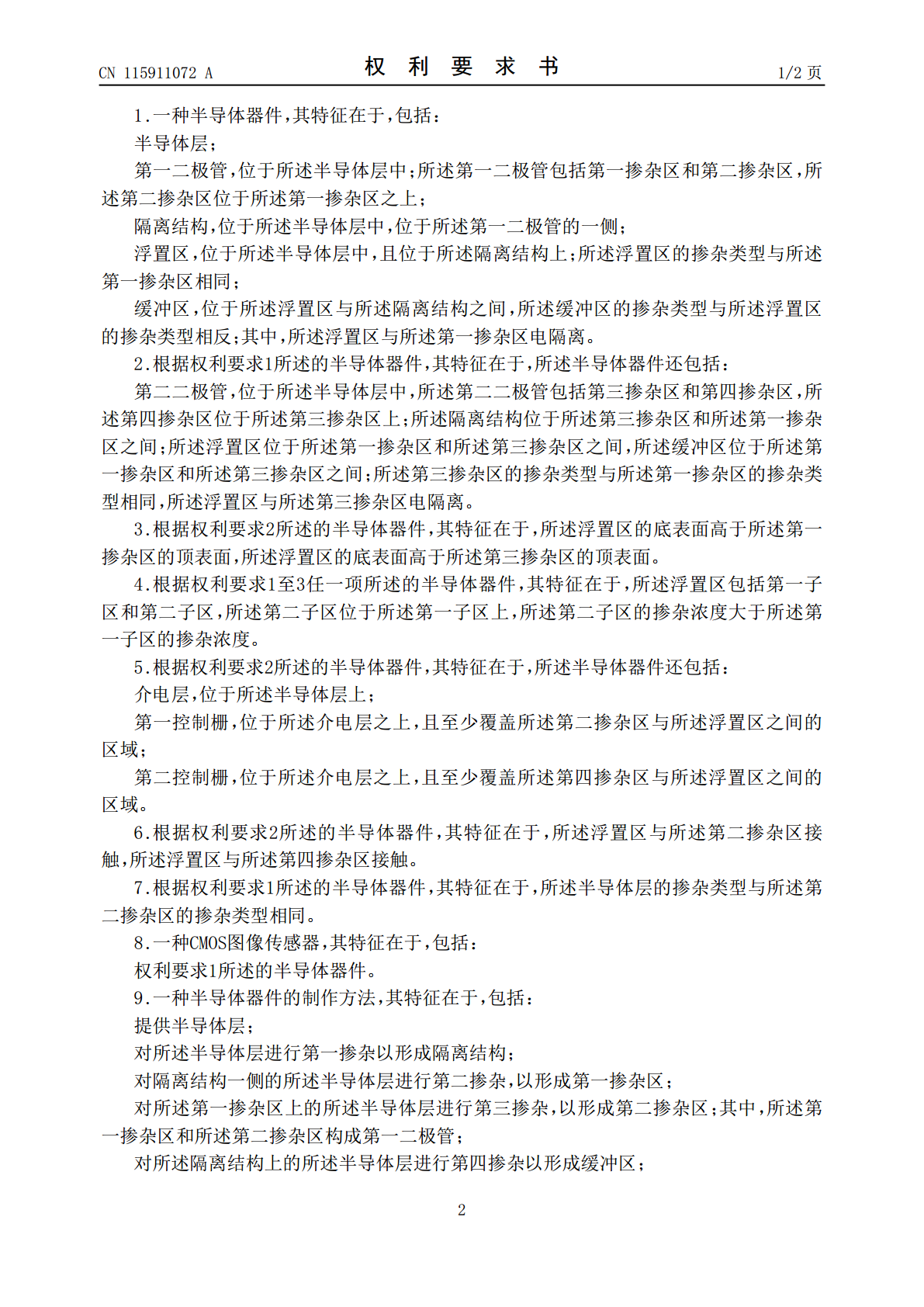

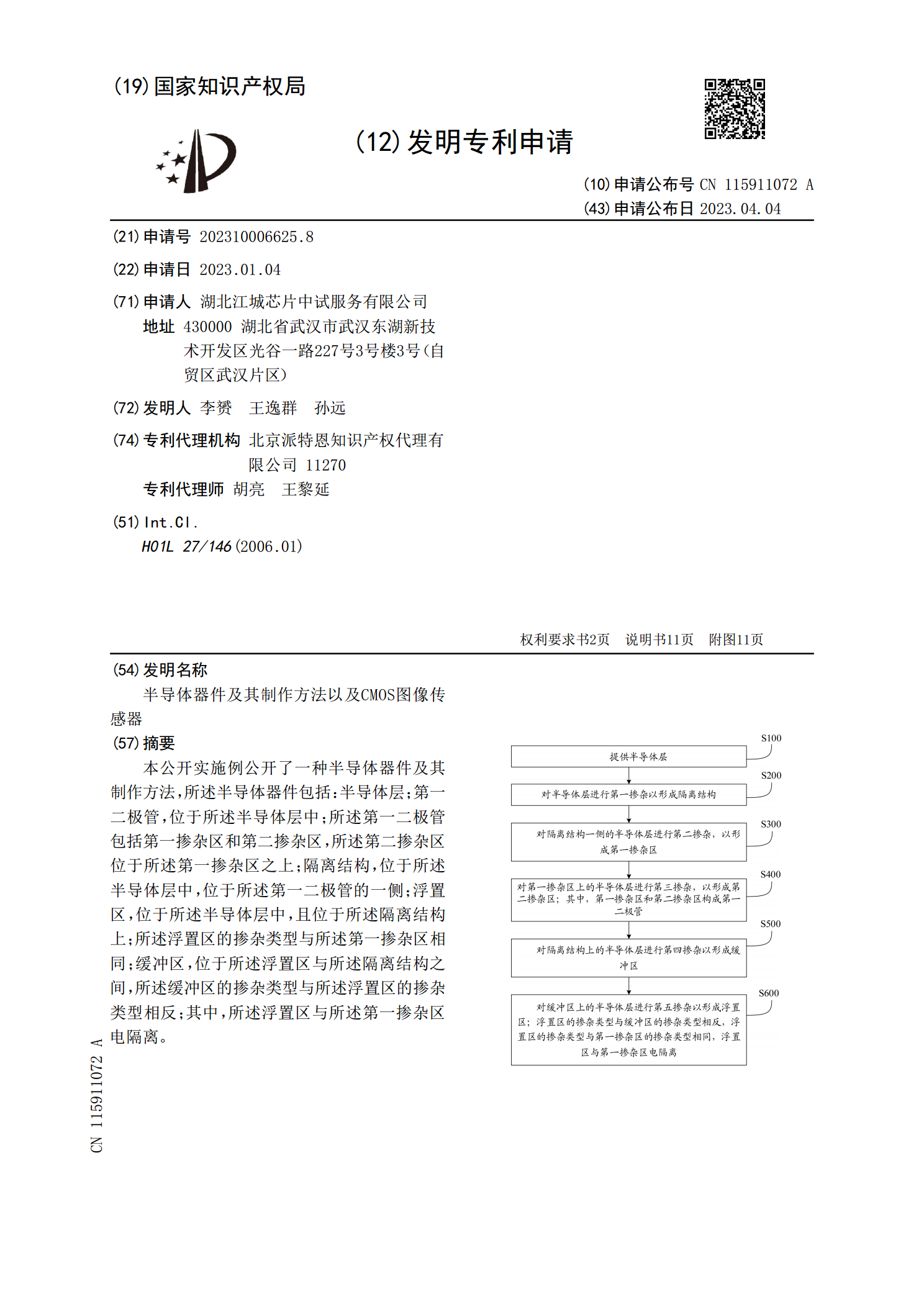

本公开实施例公开了一种半导体器件及其制作方法,所述半导体器件包括:半导体层;第一二极管,位于所述半导体层中;所述第一二极管包括第一掺杂区和第二掺杂区,所述第二掺杂区位于所述第一掺杂区之上;隔离结构,位于所述半导体层中,位于所述第一二极管的一侧;浮置区,位于所述半导体层中,且位于所述隔离结构上;所述浮置区的掺杂类型与所述第一掺杂区相同;缓冲区,位于所述浮置区与所述隔离结构之间,所述缓冲区的掺杂类型与所述浮置区的掺杂类型相反;其中,所述浮置区与所述第一掺杂区电隔离。

半导体器件的制作方法及CMOS图像传感器的制作方法.pdf

本发明提供了一种半导体器件的制作方法及CMOS图像传感器的制作方法,包括:提供一衬底,在衬底上形成图形化的第一光阻;以图形化的第一光阻为掩蔽层在衬底中注入第一类杂质离子;掩膜层填充并覆盖第一光阻;反刻蚀掩膜层以暴露出第一光阻;去除图形化的第一光阻,从而形成图形化的掩膜层,以图形化的掩膜层为掩蔽层在衬底中注入第二类杂质离子。本发明在注入第一类杂质离子后,保留第一光阻,通过掩膜层填充、反刻及去第一光阻实现第一光阻图案的反转,形成的图形化的掩膜层即所需第二类杂质离子注入的掩蔽图形,利用第一光阻反转实现自对准可有

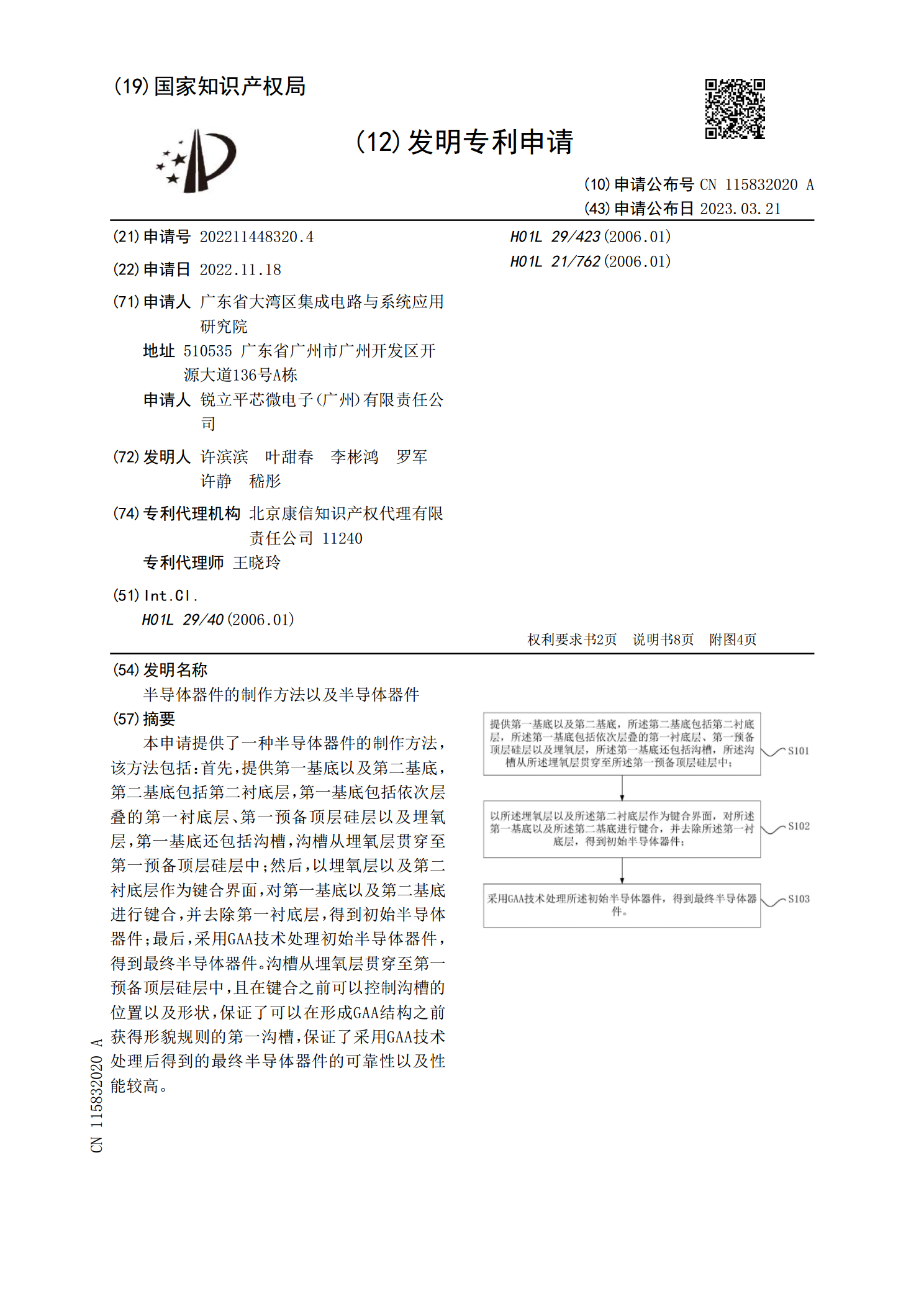

半导体器件的制作方法以及半导体器件.pdf

本申请提供了一种半导体器件的制作方法,该方法包括:首先,提供第一基底以及第二基底,第二基底包括第二衬底层,第一基底包括依次层叠的第一衬底层、第一预备顶层硅层以及埋氧层,第一基底还包括沟槽,沟槽从埋氧层贯穿至第一预备顶层硅层中;然后,以埋氧层以及第二衬底层作为键合界面,对第一基底以及第二基底进行键合,并去除第一衬底层,得到初始半导体器件;最后,采用GAA技术处理初始半导体器件,得到最终半导体器件。沟槽从埋氧层贯穿至第一预备顶层硅层中,且在键合之前可以控制沟槽的位置以及形状,保证了可以在形成GAA结构之前获得

半导体器件的制作方法以及半导体器件.pdf

本申请提供了一种半导体器件的制作方法以及半导体器件,该方法包括:提供预备基底,预备基底包括衬底以及位于衬底上的栅极;形成步骤,在预备基底的裸露表面上形成第一介质层;去除步骤,至少去除衬底的水平表面上以及栅极的水平表面上的第一介质层,剩余的第一介质层形成位于栅极两侧的子侧墙,得到基底;循环步骤,依次进行形成步骤以及去除步骤至少一次,直到栅极两侧的第一侧墙的在水平方向上的厚度达到预定厚度,第一侧墙由多个子侧墙构成,水平方向与基底的厚度方向垂直;对第一侧墙两侧的衬底进行离子注入,形成轻掺杂源区和/或轻掺杂漏区。

半导体器件的制作方法、半导体器件以及DRAM.pdf

本公开提供了一种半导体器件的制作方法、半导体器件以及DRAM,该方法包括:提供基底,基底包括衬底、多个第一电极结构以及填充结构,多个第一电极结构间隔地位于衬底上,填充结构填充在任意相邻的两个第一电极结构之间,且使得至少部分第一电极结构远离衬底一端的侧壁裸露,以形成多个第一凹槽;在部分第一凹槽中形成第一支撑部,其中,支撑区域的表面积小于开口区域的表面积,支撑区域为所有的第一支撑部覆盖填充结构的区域,开口区域为所有的第一支撑部未覆盖填充结构的区域;去除形成有第一支撑部的基底中的填充结构。本公开保证了可以尽可能