半导体元件、电子系统及其半导体元件静电放电保护方法.pdf

是你****深呀

亲,该文档总共31页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体元件、电子系统及其半导体元件静电放电保护方法.pdf

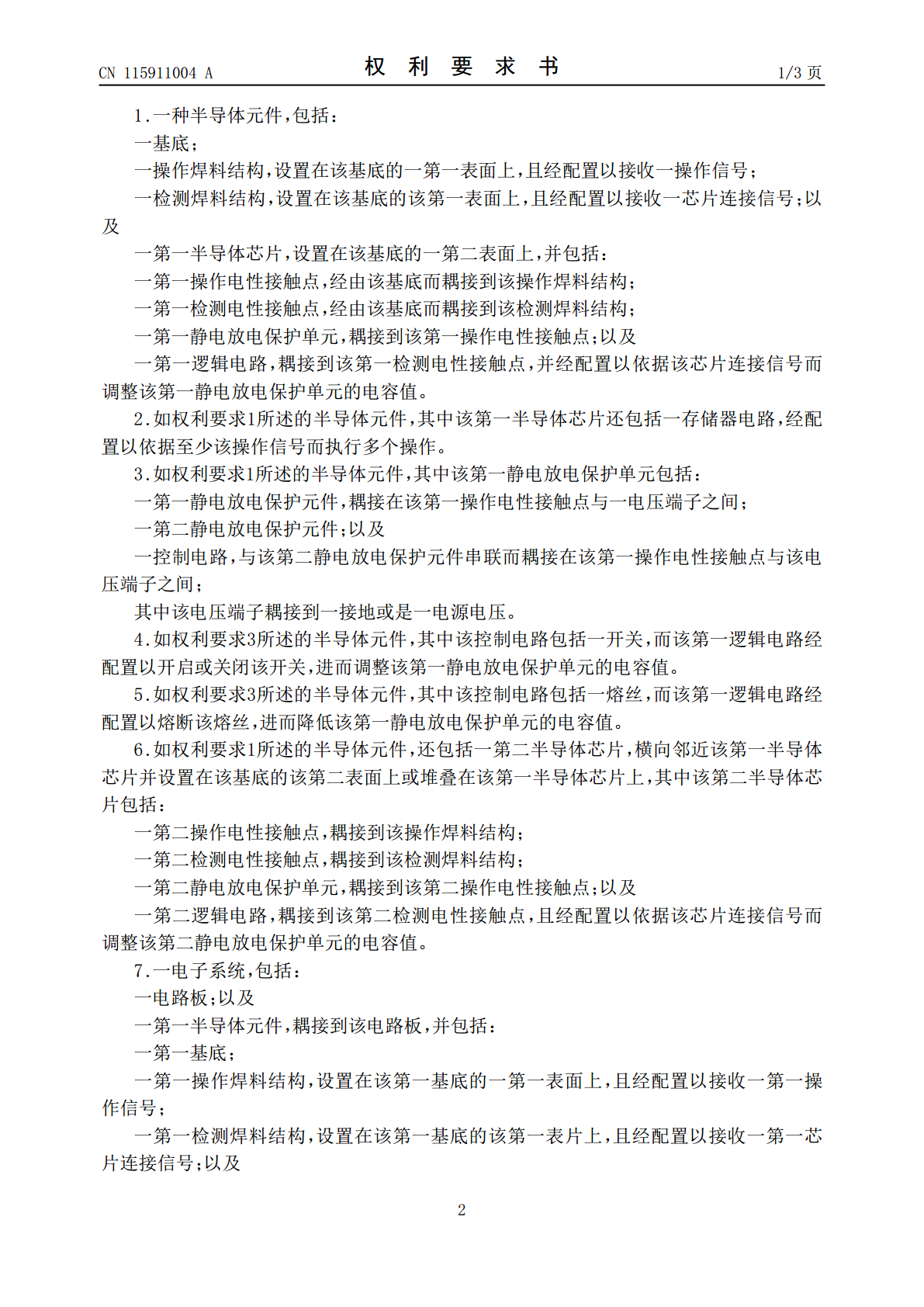

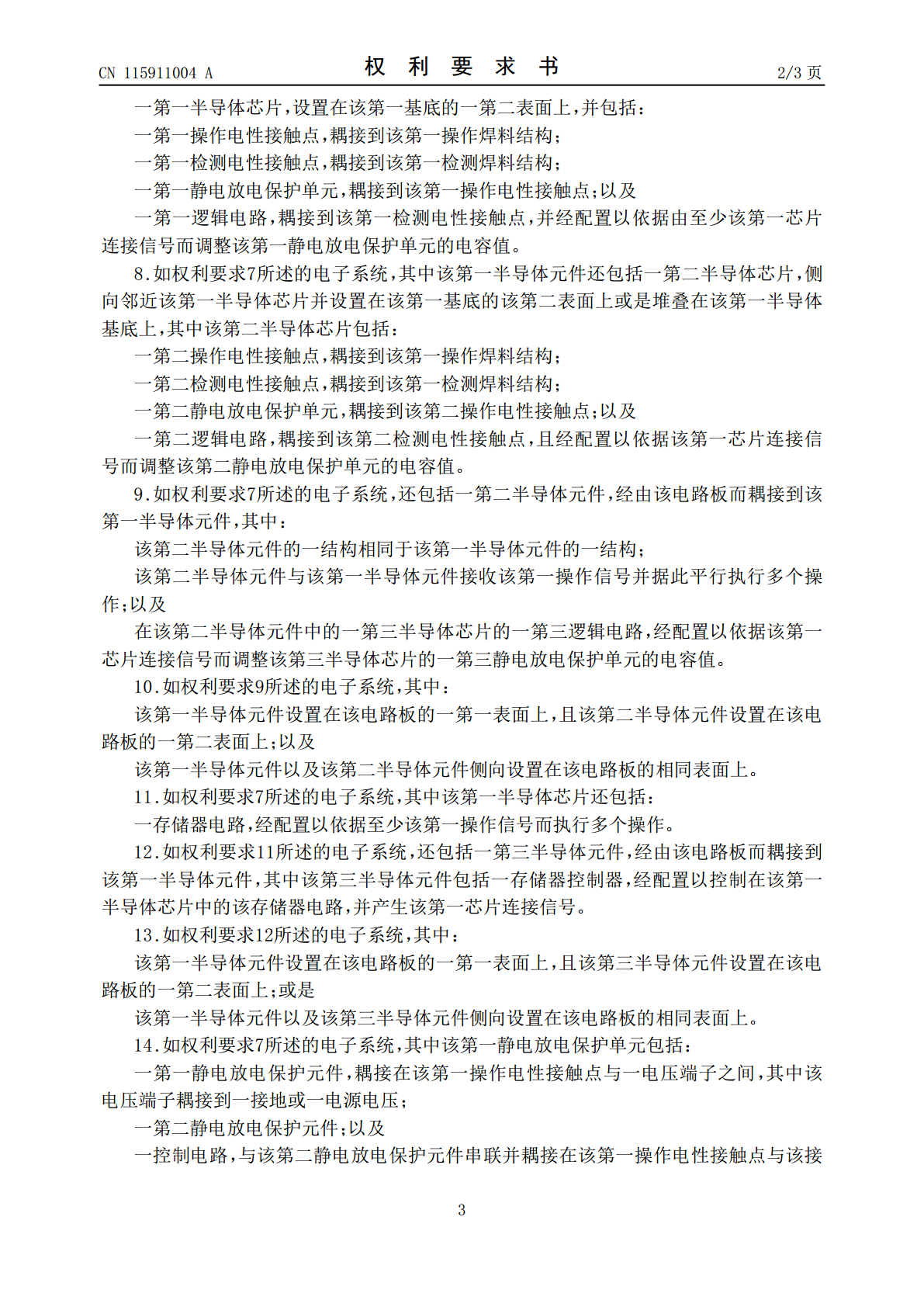

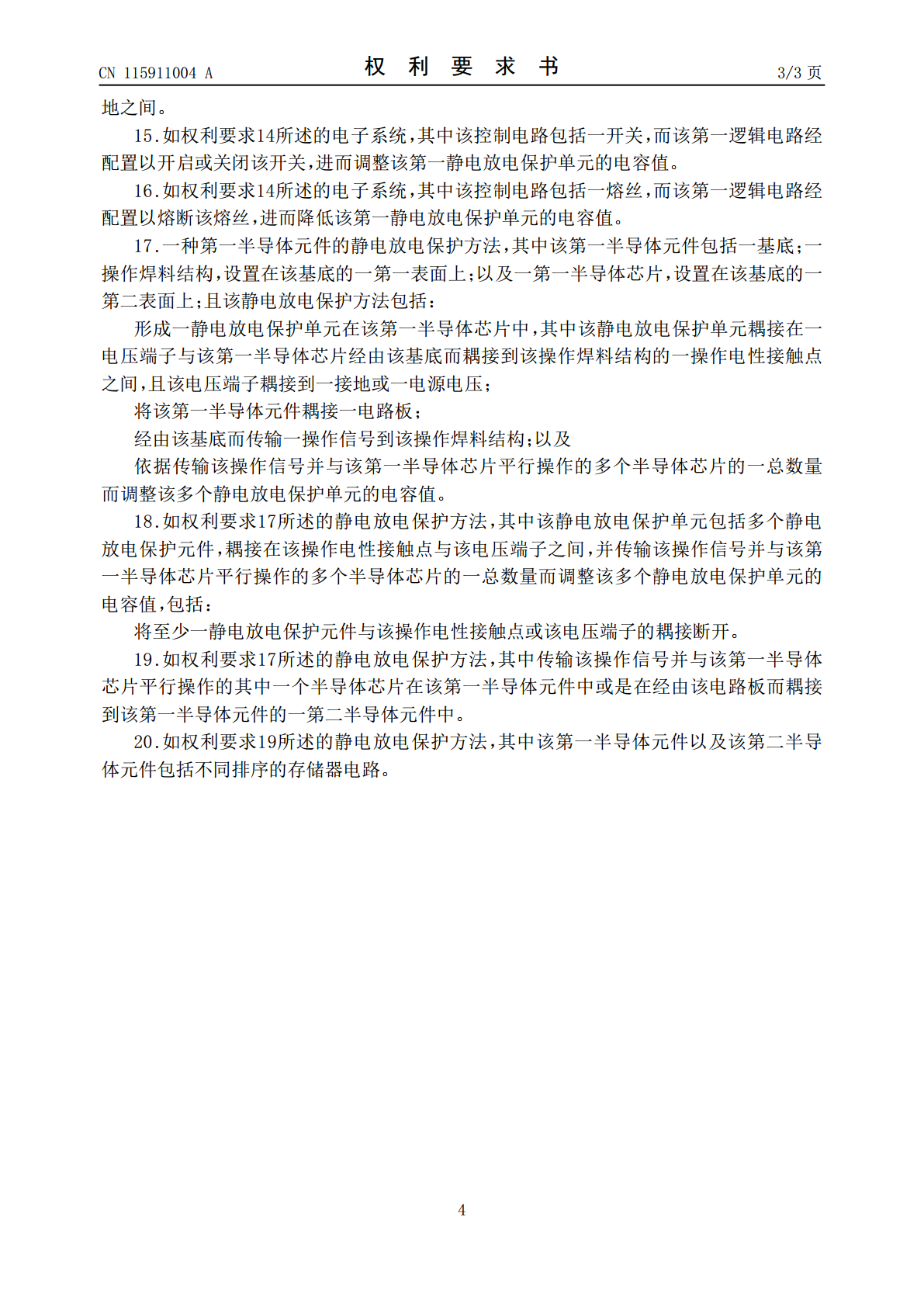

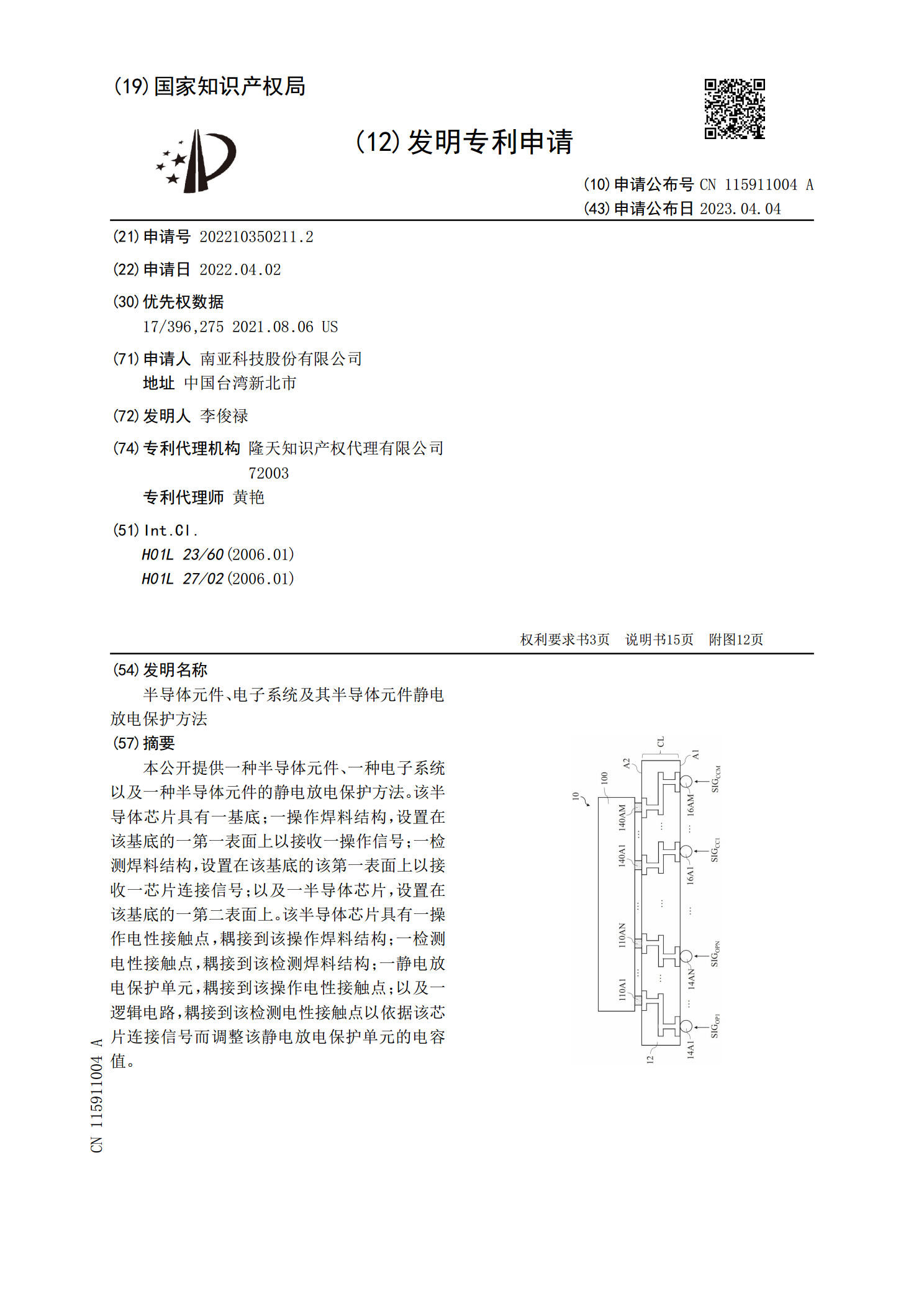

本公开提供一种半导体元件、一种电子系统以及一种半导体元件的静电放电保护方法。该半导体芯片具有一基底;一操作焊料结构,设置在该基底的一第一表面上以接收一操作信号;一检测焊料结构,设置在该基底的该第一表面上以接收一芯片连接信号;以及一半导体芯片,设置在该基底的一第二表面上。该半导体芯片具有一操作电性接触点,耦接到该操作焊料结构;一检测电性接触点,耦接到该检测焊料结构;一静电放电保护单元,耦接到该操作电性接触点;以及一逻辑电路,耦接到该检测电性接触点以依据该芯片连接信号而调整该静电放电保护单元的电容值。

半导体元件、半导体元件的封装结构及其封装方法.pdf

本发明公开了一种半导体元件,半导体元件的封装结构以及该封装结构的封装方法,半导体元件包括衬底、形成于所述衬底内的功能结构以及与所述功能结构连接的焊垫,所述功能结构包括具有网孔结构的浅槽隔离层,所述浅槽隔离层未延伸至所述焊垫,或所述浅槽隔离层延伸至所述焊垫并属于所述焊垫的一部分,其中,所述浅槽隔离层的网孔满足:网孔宽度范围为2.29μm~2.49μm。本发明的半导体元件,其能够解决由于STI(浅槽隔离)的存在导致在后续封装过程中STI(浅槽隔离)分层的问题。

半导体元件及其制备方法.pdf

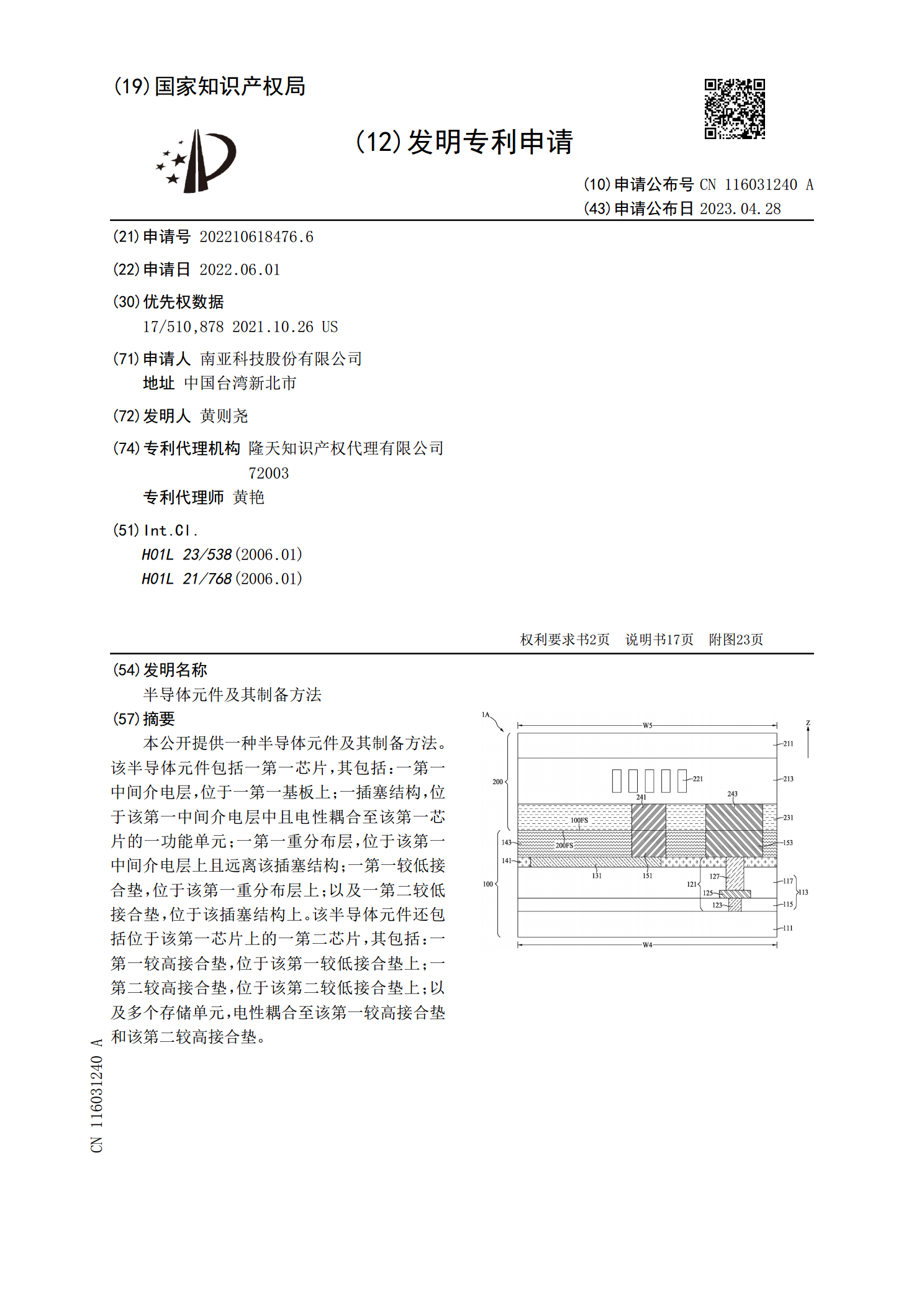

本公开提供一种半导体元件及其制备方法。该半导体元件包括一第一芯片,其包括:一第一中间介电层,位于一第一基板上;一插塞结构,位于该第一中间介电层中且电性耦合至该第一芯片的一功能单元;一第一重分布层,位于该第一中间介电层上且远离该插塞结构;一第一较低接合垫,位于该第一重分布层上;以及一第二较低接合垫,位于该插塞结构上。该半导体元件还包括位于该第一芯片上的一第二芯片,其包括:一第一较高接合垫,位于该第一较低接合垫上;一第二较高接合垫,位于该第二较低接合垫上;以及多个存储单元,电性耦合至该第一较高接合垫和该第二较

半导体元件及其制备方法.pdf

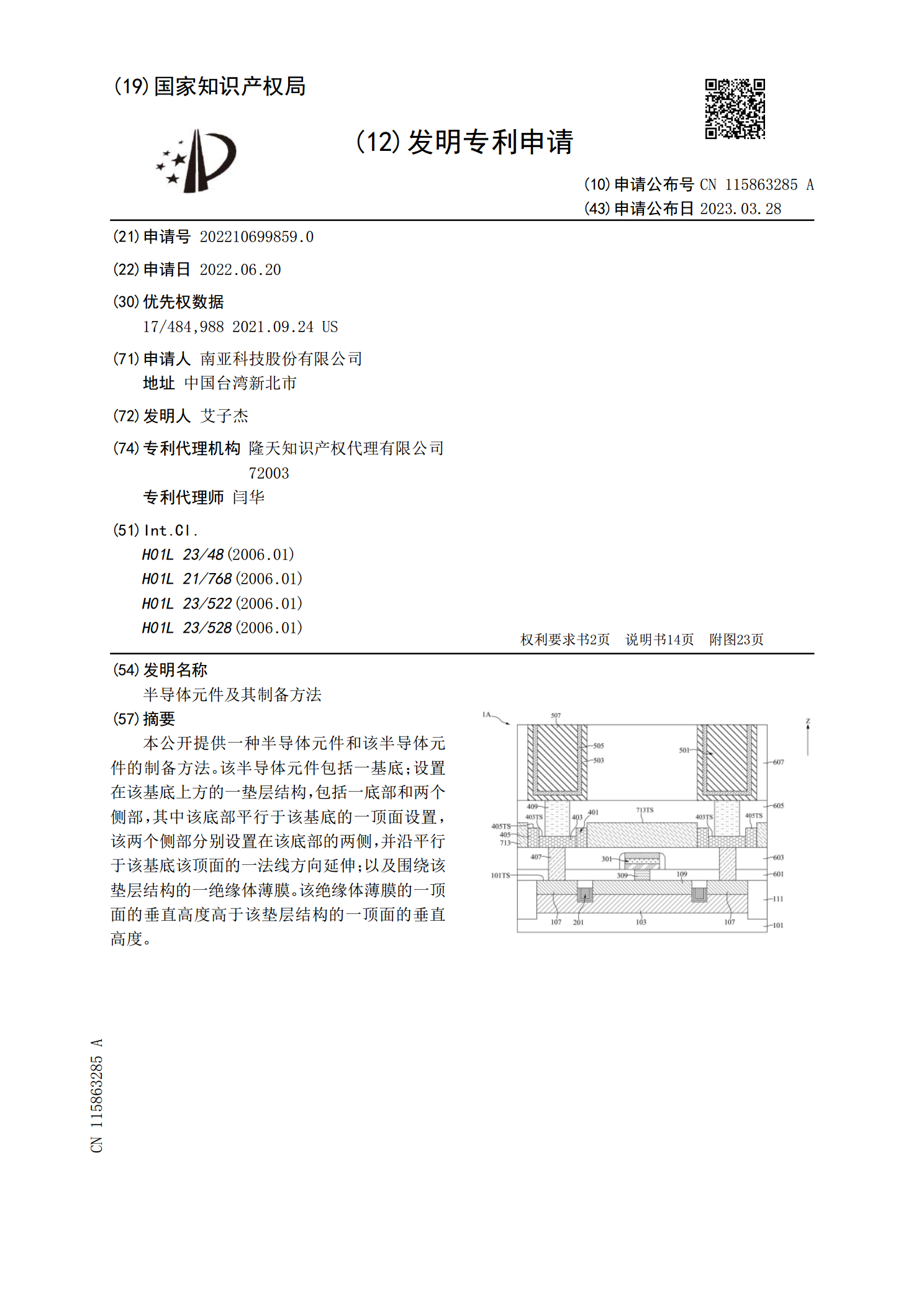

本公开提供一种半导体元件和该半导体元件的制备方法。该半导体元件包括一基底;设置在该基底上方的一垫层结构,包括一底部和两个侧部,其中该底部平行于该基底的一顶面设置,该两个侧部分别设置在该底部的两侧,并沿平行于该基底该顶面的一法线方向延伸;以及围绕该垫层结构的一绝缘体薄膜。该绝缘体薄膜的一顶面的垂直高度高于该垫层结构的一顶面的垂直高度。

半导体元件及其制备方法.pdf

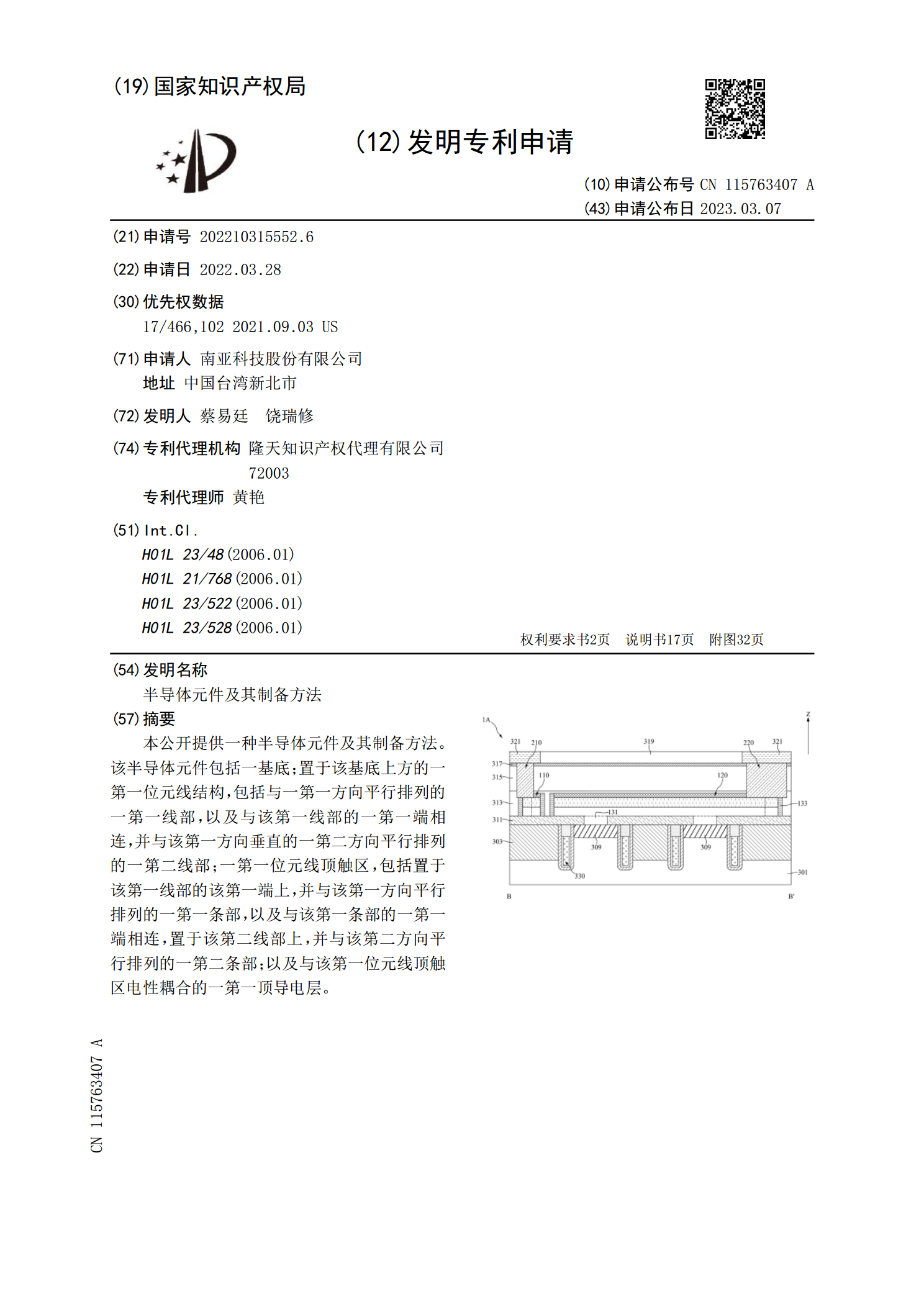

本公开提供一种半导体元件及其制备方法。该半导体元件包括一基底;置于该基底上方的一第一位元线结构,包括与一第一方向平行排列的一第一线部,以及与该第一线部的一第一端相连,并与该第一方向垂直的一第二方向平行排列的一第二线部;一第一位元线顶触区,包括置于该第一线部的该第一端上,并与该第一方向平行排列的一第一条部,以及与该第一条部的一第一端相连,置于该第二线部上,并与该第二方向平行排列的一第二条部;以及与该第一位元线顶触区电性耦合的一第一顶导电层。