一种用于叠加的封装基底、叠加型封装基底及其芯片封装结构、制备方法.pdf

猫巷****晓容

亲,该文档总共20页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种用于叠加的封装基底、叠加型封装基底及其芯片封装结构、制备方法.pdf

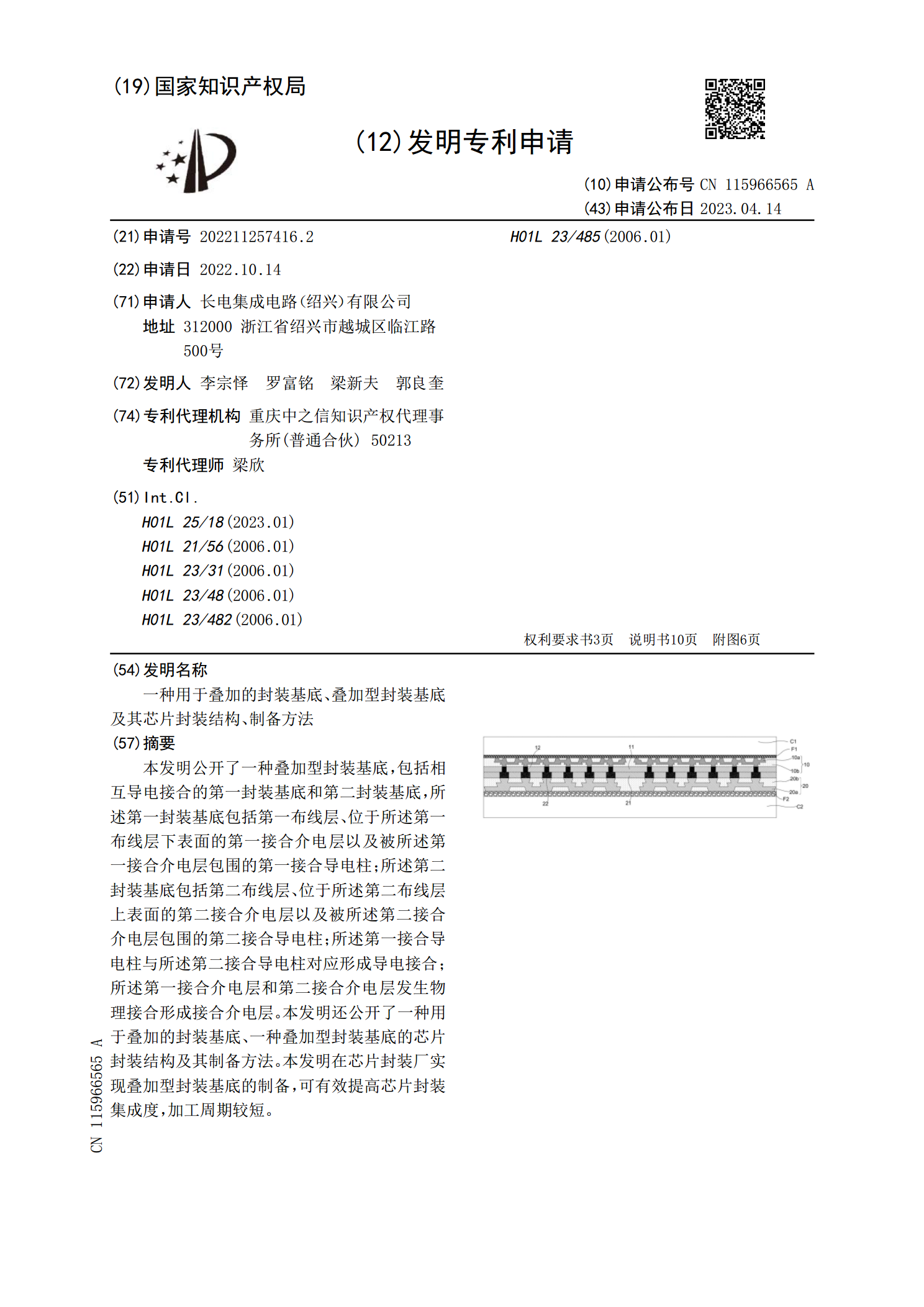

本发明公开了一种叠加型封装基底,包括相互导电接合的第一封装基底和第二封装基底,所述第一封装基底包括第一布线层、位于所述第一布线层下表面的第一接合介电层以及被所述第一接合介电层包围的第一接合导电柱;所述第二封装基底包括第二布线层、位于所述第二布线层上表面的第二接合介电层以及被所述第二接合介电层包围的第二接合导电柱;所述第一接合导电柱与所述第二接合导电柱对应形成导电接合;所述第一接合介电层和第二接合介电层发生物理接合形成接合介电层。本发明还公开了一种用于叠加的封装基底、一种叠加型封装基底的芯片封装结构及其制备

一种叠加型封装的芯片封装结构及其制备方法.pdf

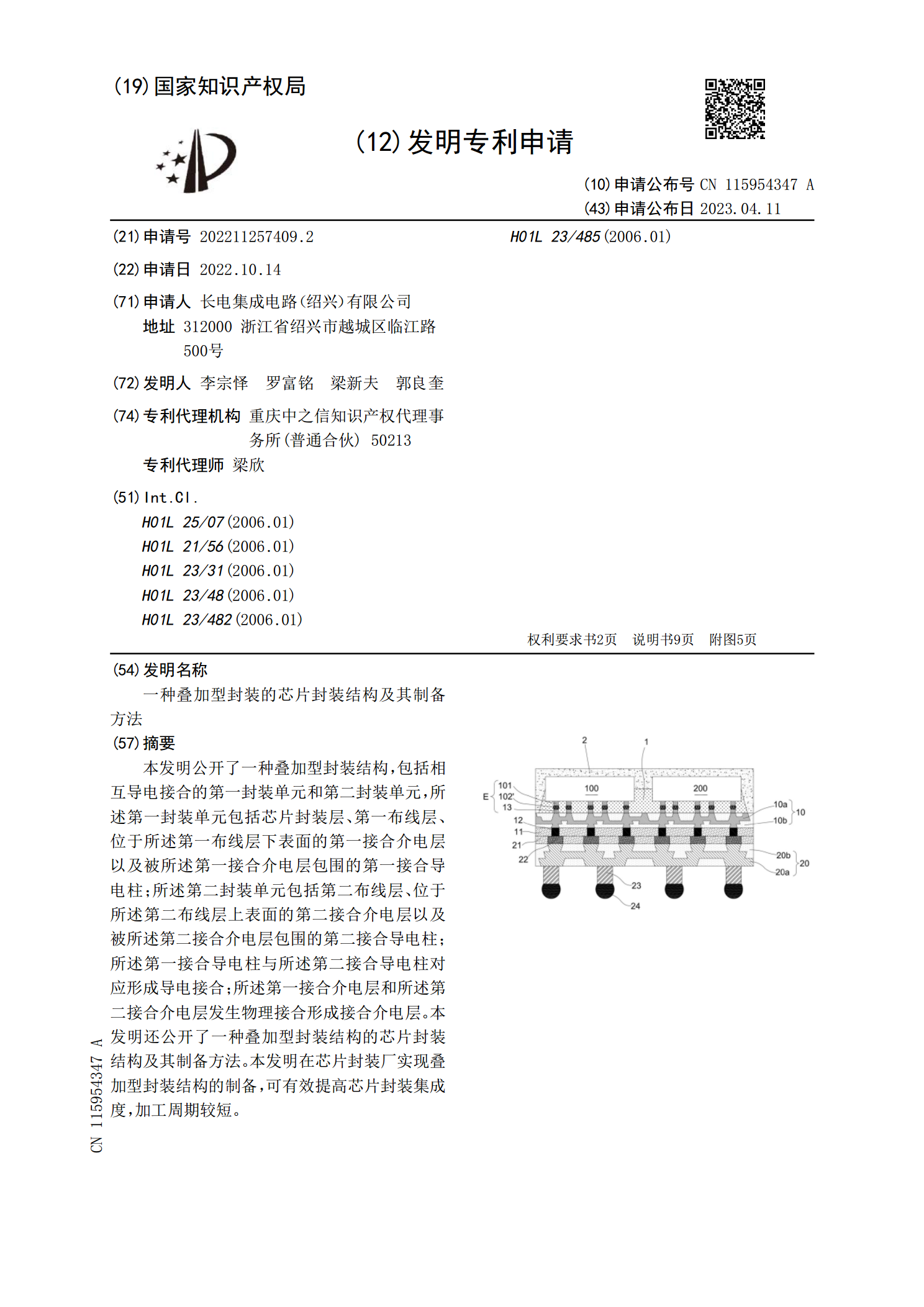

本发明公开了一种叠加型封装结构,包括相互导电接合的第一封装单元和第二封装单元,所述第一封装单元包括芯片封装层、第一布线层、位于所述第一布线层下表面的第一接合介电层以及被所述第一接合介电层包围的第一接合导电柱;所述第二封装单元包括第二布线层、位于所述第二布线层上表面的第二接合介电层以及被所述第二接合介电层包围的第二接合导电柱;所述第一接合导电柱与所述第二接合导电柱对应形成导电接合;所述第一接合介电层和所述第二接合介电层发生物理接合形成接合介电层。本发明还公开了一种叠加型封装结构的芯片封装结构及其制备方法。本

芯片封装结构及其封装方法.pdf

本发明提供一种芯片封装结构及其封装方法,芯片封装结构包括硅基板、位于所述硅基板的正面的钝化层、位于所述钝化层的正面的介电层、至少包覆所述硅基板的侧壁的塑封层,所述硅基板的正面嵌设有芯片电极,所述钝化层以及所述介电层上设有供所述芯片电极向外暴露的导通孔,所述芯片电极的正面连接有金属凸块;所述塑封层靠近所述硅基板的正面的一端与所述钝化层相接合;相较于现有的所述塑封层与所述介电层相接合,增加了所述塑封层与芯片之间的结合力,所述塑封层不易因受力而脱落,同时,在封装过程中,所述钝化层使芯片之间相互固定在一起,能够防

芯基底和封装结构.pdf

提供了芯基底和封装结构。所述封装结构包括:芯基底,包括包含多个第一空腔和多个第二空腔的基底基体、位于所述多个第二空腔中的多个块以及在所述多个块中的每个与基底基体之间延伸的多个桥结构;多个半导体芯片,位于所述多个第一空腔中;以及模制层,被构造为覆盖芯基底和所述多个半导体芯片,模制层的一部分位于所述多个第一空腔和所述多个第二空腔中。

芯片封装结构及其制备方法.pdf

本发明提供一种芯片封装结构及其制备方法,其中芯片封装结构包括:散热盖、加固片、芯片、辅助电子器件和基板;加固片、芯片和辅助电子器件固定设置于基板的同一表面上,散热盖位于加固片背离基板的一侧,散热盖与加固片固定连接,散热盖与芯片焊接,基板与加固片和散热盖合围成一安装腔,芯片位于安装腔内;加固片朝向基板的表面开设有容纳腔,辅助电子器件位于容纳腔内。本发明能够提高芯片封装的良率。