芯片封装方法及封装体.pdf

闪闪****魔王

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

芯片封装方法及封装体.pdf

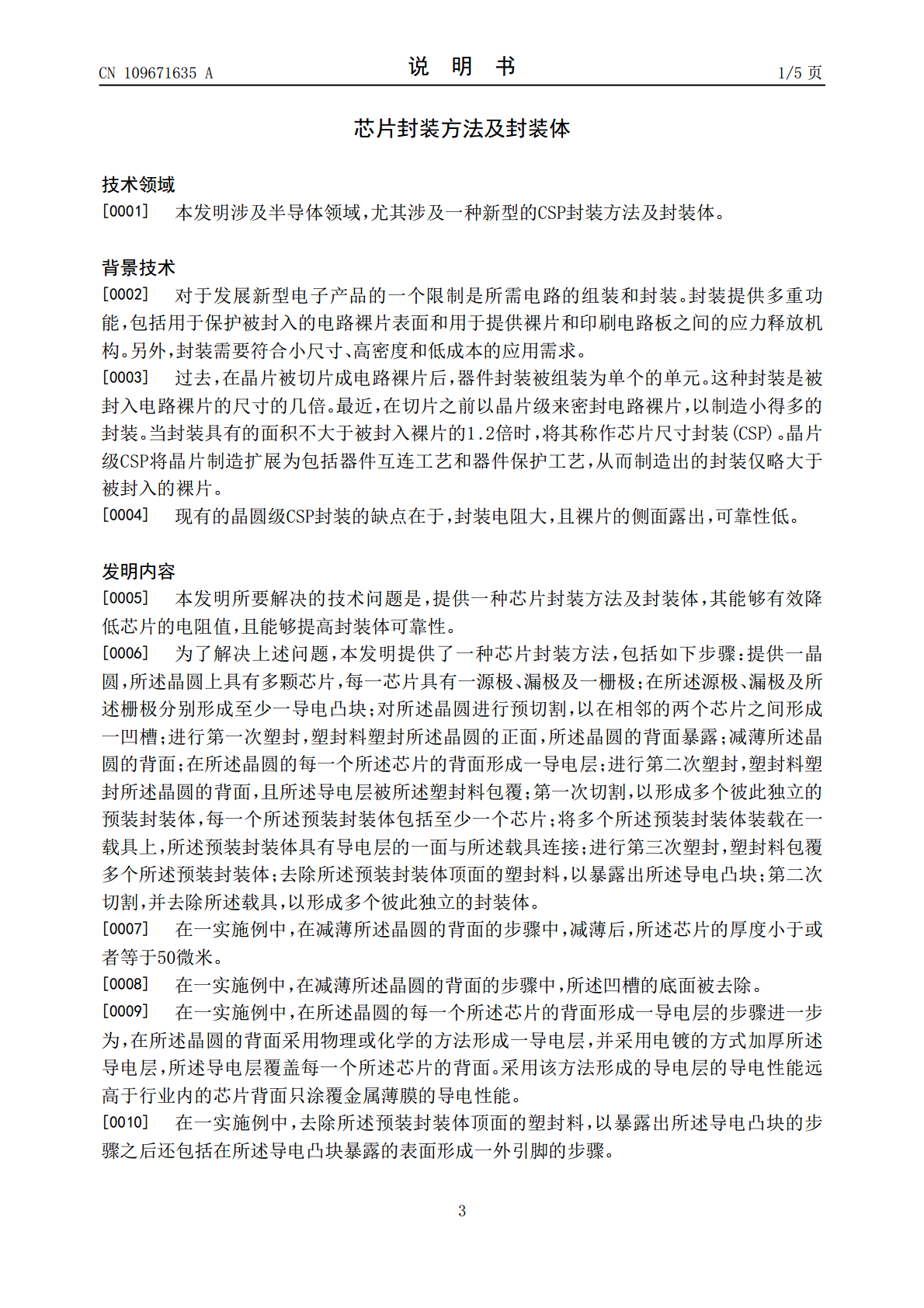

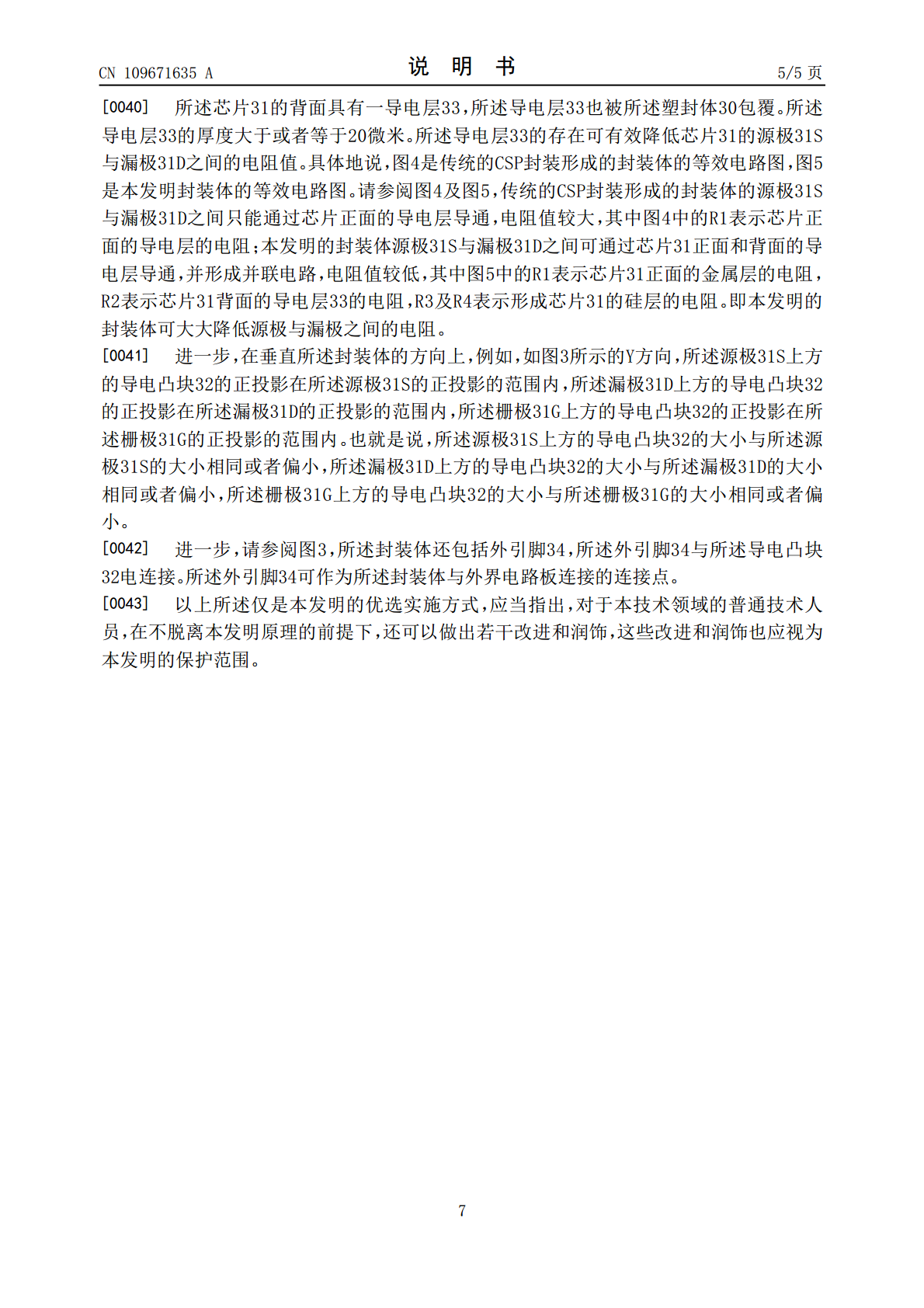

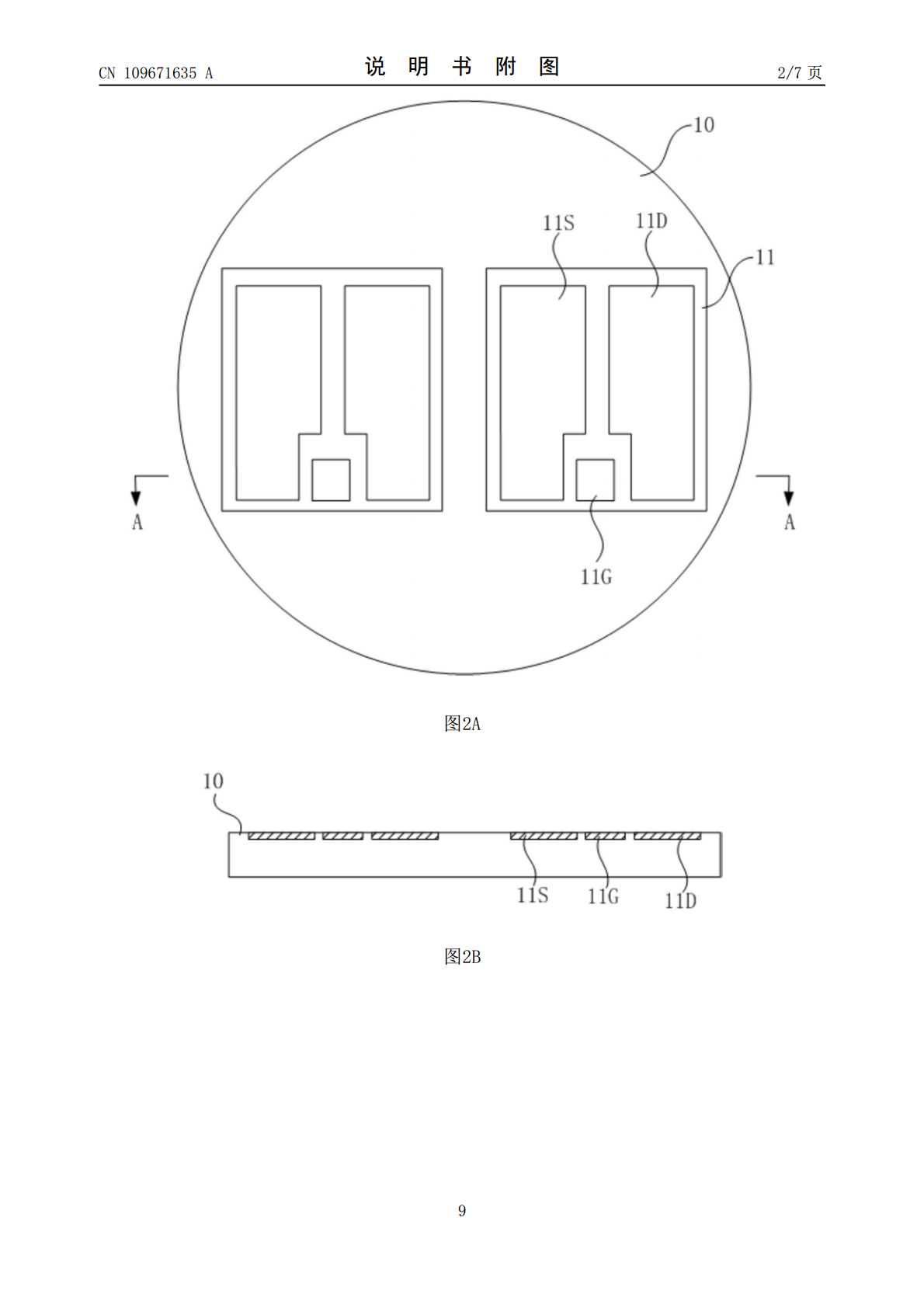

本发明提供一种芯片封装方法及封装体,具体地说,本发明提供一种CSP封装方法,本发明的优点在于,(1)芯片被减薄,有效降低大功率芯片的电阻值;(2)芯片背面形成导电层,可以降低芯片的源极和漏极之间的电阻值;(3)封装体的六个面除了与外部电路连接的连接引脚露出,其余部分完全由塑封体保护,无芯片露出,可靠性高。

芯片的封装方法以及芯片封装体.pdf

本发明公开了一种芯片的封装方法以及芯片封装体。芯片的封装方法包括:获取到陶瓷基板,陶瓷基板的一表面形成有多个焊盘;将至少一个芯片的各引脚与对应的焊盘进行焊接;在陶瓷基板的一侧面固定且贴合设置导流件,导流件的一表面与陶瓷基板靠近芯片的一表面平齐;利用导流件将粘合剂导流至各芯片与陶瓷基板之间,以完成芯片的封装。上述方案,能够减少空洞以及填充不完全的现象发生,从而提高各芯片与陶瓷基板之间的结合力,提高各芯片与陶瓷基板之间的结构稳定性与可靠性。

封装母板、芯片的封装方法及封装体.pdf

本申请公开了一种封装母板、芯片的封装方法及封装体。封装母板包括芯片,载板,第一塑封体和导电件;第一金属层包括若干第一焊盘,第二金属层包括若干第二焊盘,第一焊盘与第二焊盘电连接;每一第一焊盘上固定有芯片,在两相邻芯片之间的预设区域设置第二盲孔;每一第二盲孔用于两侧的导电件连接第二金属层,或,每一第二盲孔用于一侧的导电件连接第二金属层,还用于另一侧的第一焊盘连接第二金属层。上述封装母板,第二盲孔共用的设计,一方面,通过半个盲孔给各芯片转移引脚,节省了占据体积,能实现大尺寸芯片的封装,另一方面减少第二盲孔的制作

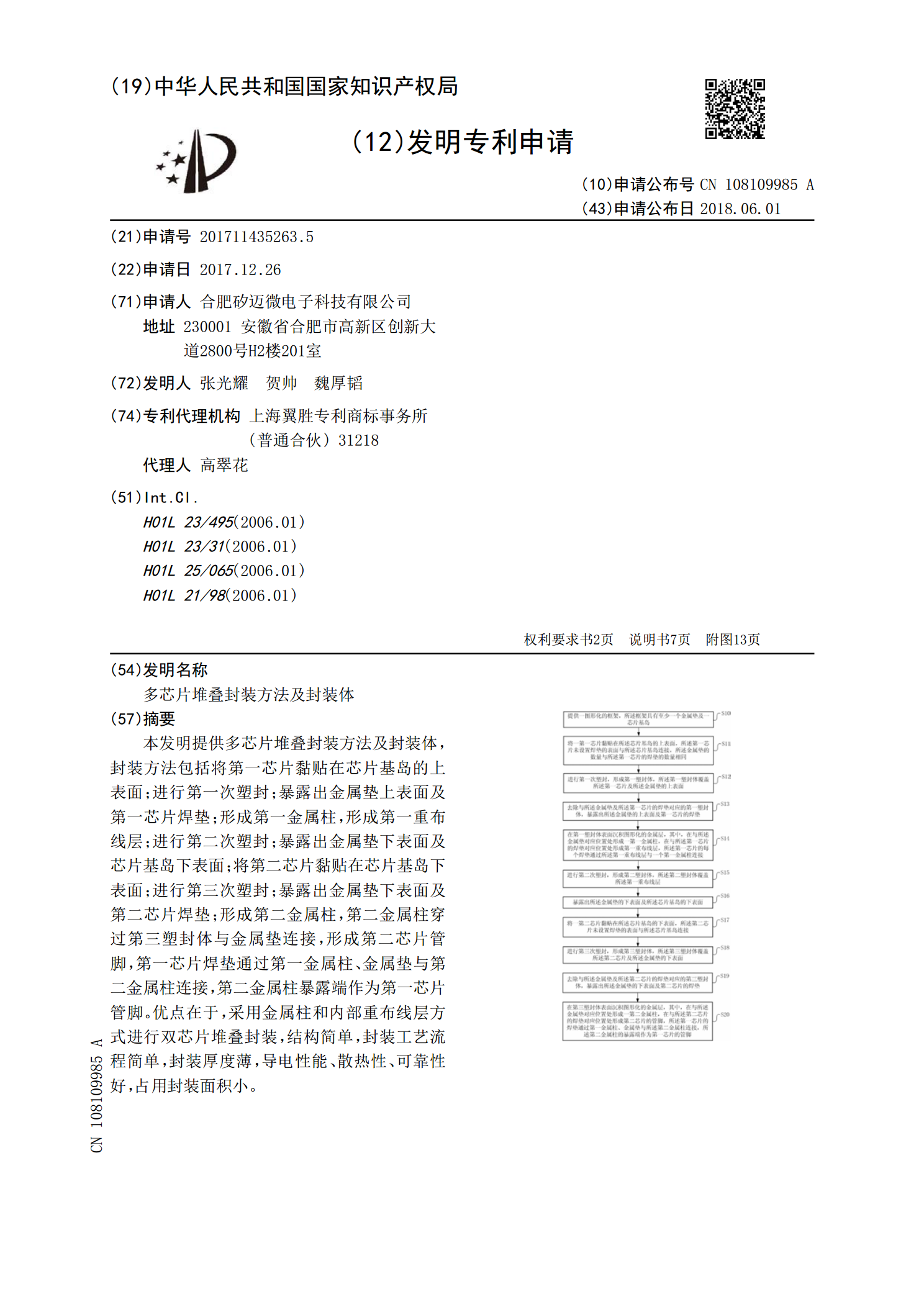

多芯片堆叠封装方法及封装体.pdf

本发明提供多芯片堆叠封装方法及封装体,封装方法包括将第一芯片黏贴在芯片基岛的上表面;进行第一次塑封;暴露出金属垫上表面及第一芯片焊垫;形成第一金属柱,形成第一重布线层;进行第二次塑封;暴露出金属垫下表面及芯片基岛下表面;将第二芯片黏贴在芯片基岛下表面;进行第三次塑封;暴露出金属垫下表面及第二芯片焊垫;形成第二金属柱,第二金属柱穿过第三塑封体与金属垫连接,形成第二芯片管脚,第一芯片焊垫通过第一金属柱、金属垫与第二金属柱连接,第二金属柱暴露端作为第一芯片管脚。优点在于,采用金属柱和内部重布线层方式进行双芯片堆

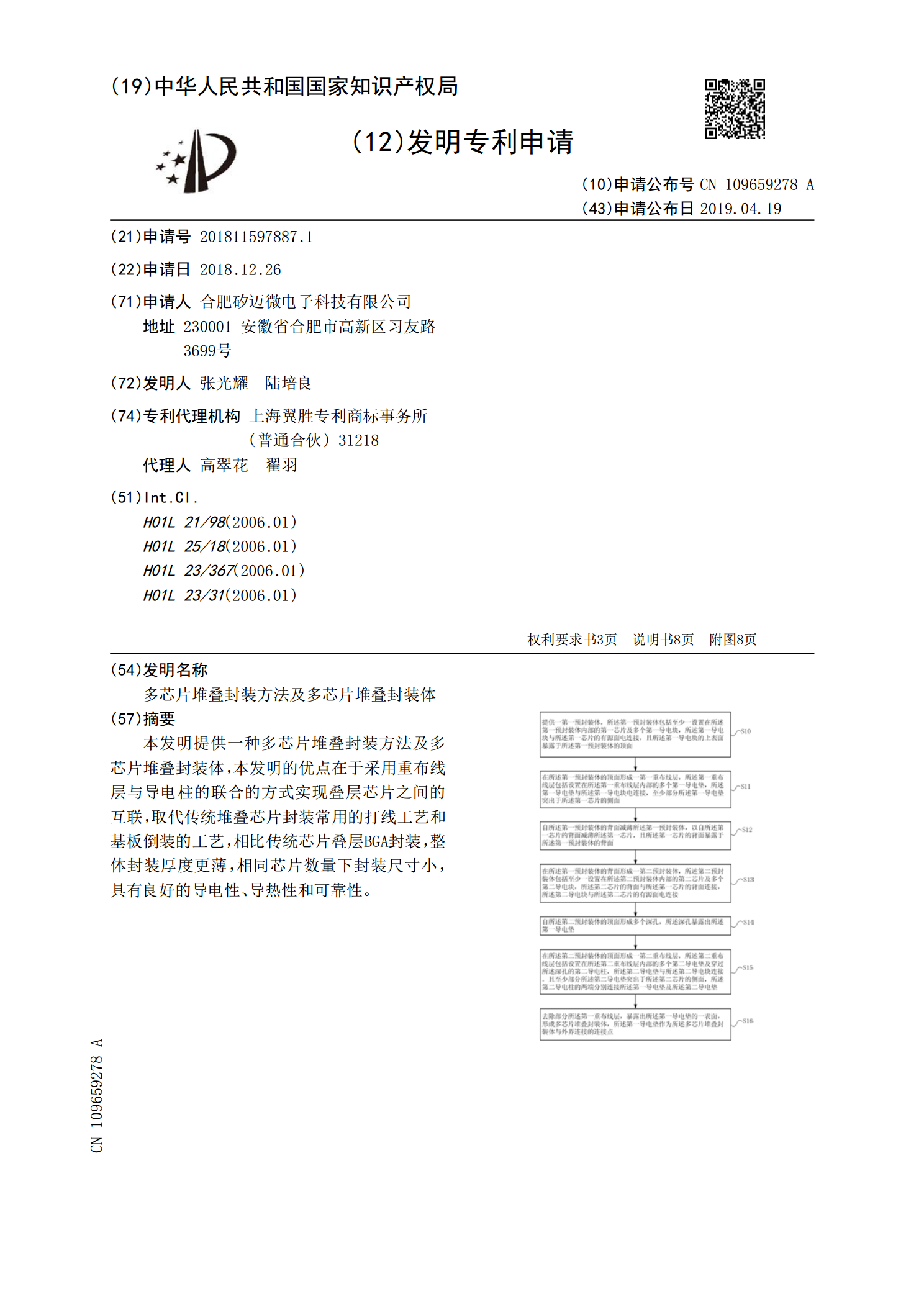

多芯片堆叠封装方法及多芯片堆叠封装体.pdf

本发明提供一种多芯片堆叠封装方法及多芯片堆叠封装体,本发明的优点在于采用重布线层与导电柱的联合的方式实现叠层芯片之间的互联,取代传统堆叠芯片封装常用的打线工艺和基板倒装的工艺,相比传统芯片叠层BGA封装,整体封装厚度更薄,相同芯片数量下封装尺寸小,具有良好的导电性、导热性和可靠性。