沟槽型功率器件的制造方法.pdf

猫巷****婉慧

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

沟槽型功率器件的制造方法.pdf

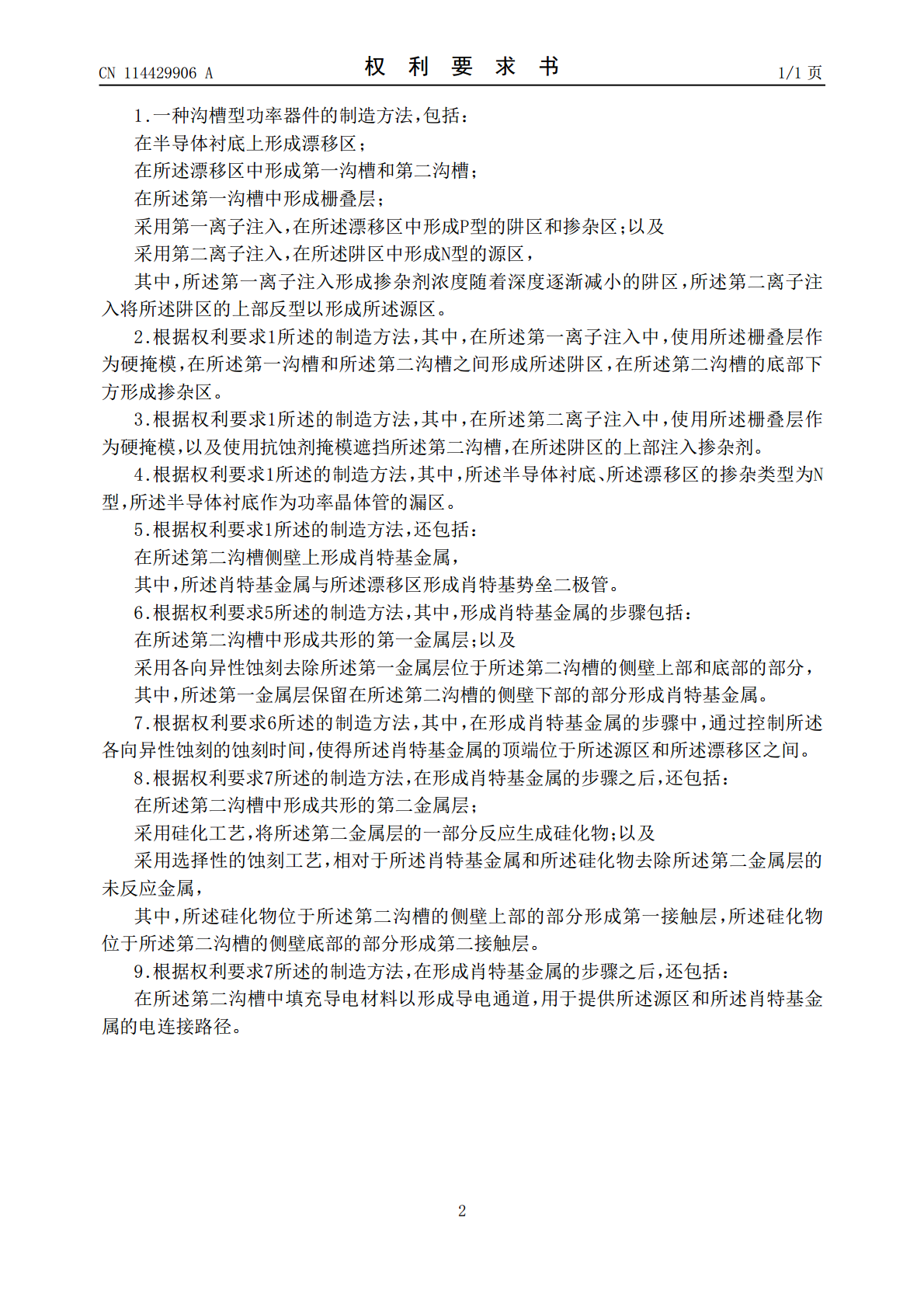

本申请公开了沟槽型功率器件的制造方法。所述制造方法包括:在半导体衬底上形成漂移区;在所述漂移区中形成第一沟槽和第二沟槽;在所述第一沟槽中形成栅叠层;采用第一离子注入,在所述漂移区中形成P型的阱区和掺杂区;以及采用第二离子注入,在所述阱区中形成N型的源区,其中,所述第一离子注入形成掺杂剂浓度随着深度逐渐减小的阱区,所述第二离子注入将所述阱区的上部反型以形成所述源区。该制造方法在公共的离子注入步骤中以自对准方式形成P型的阱区和掺杂区,不仅可以提高功率器件的性能,而且可以减少离子注入的工艺步骤和掩模数量,从而降

沟槽型功率器件及其制造方法.pdf

本申请公开了沟槽型功率器件及其制造方法。所述沟槽型功率器件包括:半导体衬底;位于所述半导体衬底上的漂移区;位于所述漂移区中的第一沟槽和第二沟槽;位于所述第一沟槽中的栅叠层;以及位于所述第二沟槽侧壁上的肖特基金属,其中,所述肖特基金属与所述漂移区形成肖特基势垒二极管。该沟槽型功率器件采用双沟槽结构,将沟槽型MOSFET和肖特基势垒二极管相结合且将肖特基金属形成在沟槽侧壁上,不仅可以提高功率器件的性能,而且可以减小功率器件的单元面积。

沟槽型功率器件的沟槽栅结构及其制造方法.pdf

一种沟槽型功率器件的沟槽栅结构及其制造方法,在半导体基底的沟槽内底部的设有厚氧化层,沟槽侧壁形成沟槽型功率器件的栅氧化层,及在沟槽内沉积形成一个塞状多晶硅栅极,且在厚氧化层上方及多晶硅栅极下方设有第一限制部,及包覆第一限制部的第二限制部。透过第一限制部及第二限制部的存在,在后续工序中将保留第二限制部下方的厚氧化层,从而能降低工艺成本;能在更小深宽比的沟槽中形成良好的TBO(ThickBottomOxide),从而能适用于各种深宽比的沟槽的TBO形成,从而具有较大的使用范围。

沟槽功率器件及其制造方法.pdf

本发明提供一种沟槽功率器件及其制造方法,所述沟槽功率器件的制造方法包括:提供一衬底,包括器件单元区及电极连接区,并具有第一沟槽;形成隔离材料层,并以剩余的第一沟槽作为第二沟槽;形成屏蔽栅材料层;在第二沟槽中形成屏蔽栅,屏蔽栅具有平坦的顶面;在器件单元区的第一沟槽中形成控制栅结构。本发明中,通过形成具有平坦的顶面的屏蔽栅,从而可利用其平坦的顶面在后续形成控制栅结构的过程中防止控制栅材料层残留于屏蔽栅的顶面,进而减少或防止因在电极连接区引出屏蔽栅时因残留于屏蔽栅上的控制栅材料层与控制栅短路的风险。

沟槽型MOS器件的制造方法.pdf

本发明提供了一种沟槽型MOS器件的制造方法,采用碳膜层和氮氧化硅层作为硬掩膜层,所述碳膜层和所述氮氧化硅层具有很高的刻蚀选择比,由此,可以采用较薄的氮氧化硅层,以形成小尺寸的开口用以执行离子注入工艺并且还易于控制所形成的开口的形貌,从而能够将有源区注入结构的尺寸降下来,并进而可以减小整个MOS器件的尺寸。