栅极驱动电路.pdf

努力****甲寅

亲,该文档总共21页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

栅极驱动电路.pdf

提供了一种栅极驱动电路。根据实施方式的栅极驱动电路包括包含多个级的移位寄存器。多个级中的第n级包括锁存器控制电路,该锁存器控制电路包括连接至QB节点的第一NMOS晶体管、连接至Q节点的第二NMOS晶体管以及具有输入有第一时钟的栅电极并且连接至第一NMOS晶体管和第二NMOS晶体管的第三NMOS晶体管,其中n是正整数。锁存器连接在Q节点与QB节点之间。传输门连接至Q节点和QB节点。在栅极驱动电路中,前一级和后一级的输出信号被控制为与第一时钟同步以抑制毛刺。

栅极驱动电路.pdf

本发明公开了一种栅极驱动电路,其包括包含多个级的移位寄存器。多个级中的第n级包括根据Q节点处的电压将第一时钟输出至输出节点的上拉开关元件、根据QB节点处的电压将栅极低电压输出至输出节点的下拉开关元件以及将Q节点处的电压和QB节点处的电压反相并输出的逻辑单元。逻辑单元包括:第一开关元件,其位于提供起始电压的起始电压线与Q节点之间;第二开关元件,其连接至QB节点;第三开关元件,其位于第二开关元件与栅极低电压线之间;第四开关元件,其位于栅极高电压线与QB节点之间;第五开关元件,其位于Q节点与栅极低电压线之间;第

栅极驱动电路.pdf

本发明提供一种栅极驱动电路,实现遮挡时间的精度提高及对误动作的宽容度的提高。本发明的栅极驱动电路对电力半导体开关进行驱动,其特征在于包括:比较电路,将所述电力半导体开关的集电极‑发射极电压、与规定的阈值电压进行比较;以及时间测量电路,在所述比较电路检测到所述集电极‑发射极电压超过所述阈值电压后开始测量时间,且所述栅极驱动电路包括:输出电路,在所述时间测量电路测量了待机保留时间(遮挡时间)后,输出意指电力半导体开关为异常状态的异常信号。

栅极驱动电路以及包括栅极驱动电路的显示装置.pdf

提供一种栅极驱动电路以及包括栅极驱动电路的显示装置。栅极驱动电路包括:多个信号传输器;以及多个第一缓存器,每个连接至多个信号传输器的其中之一并且包括:第一晶体管;以及第二晶体管,连接至第一晶体管,其中在第一和第二晶体管之间具有用于输出栅极脉冲的第一输出节点,其中多个信号传输器包括:第一控制器,在第一单位时间向第一控制器输入激活时钟时控制第一控制节点用作导通第一晶体管的上拉控制节点,并且在第二单位时间向第一控制器输入失活时钟时禁用;以及第二控制器,在第二单位时间向第二控制器输入激活时钟时控制第二控制节点用作

栅极驱动电路以及包括栅极驱动电路的显示装置.pdf

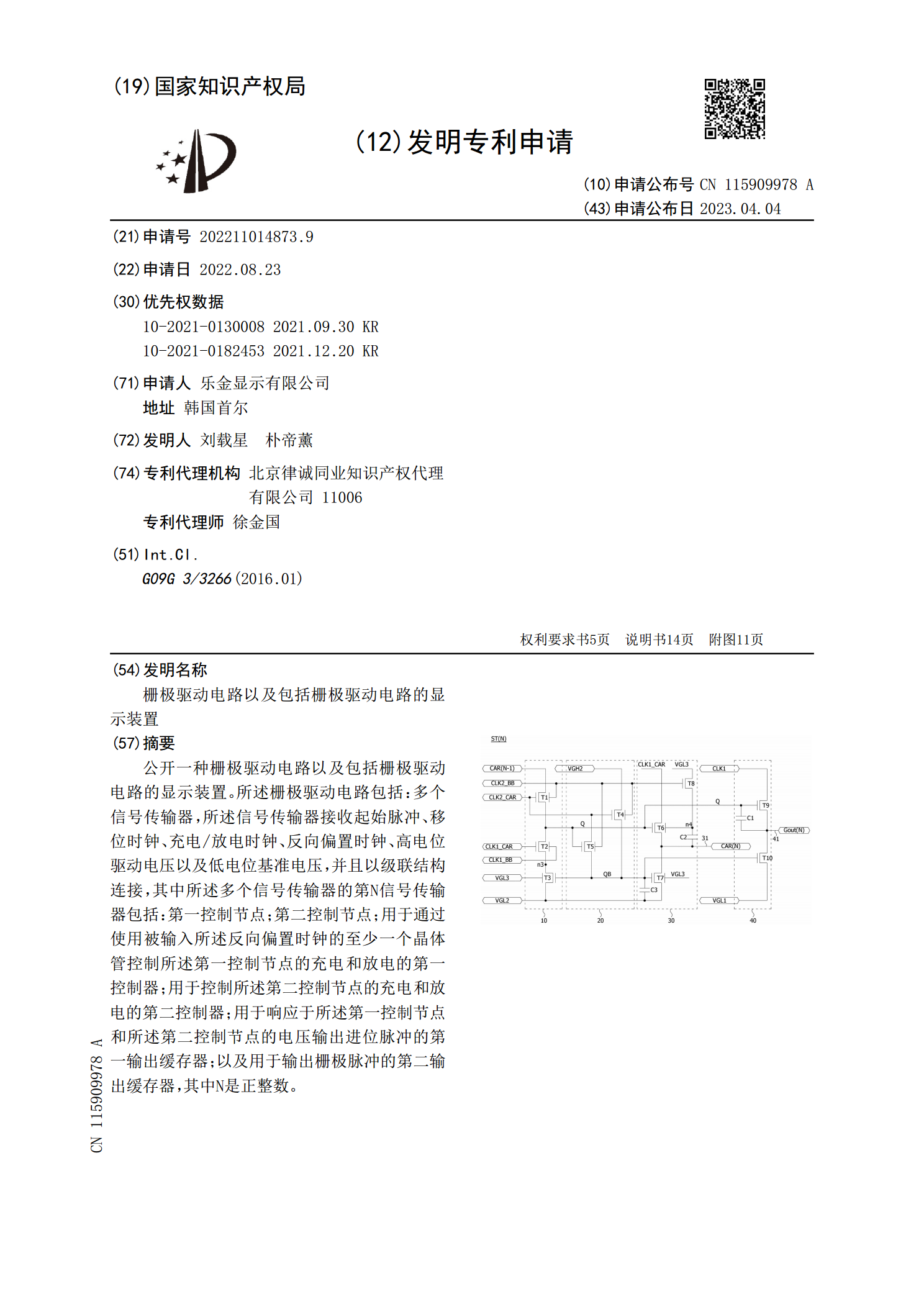

公开一种栅极驱动电路以及包括栅极驱动电路的显示装置。所述栅极驱动电路包括:多个信号传输器,所述信号传输器接收起始脉冲、移位时钟、充电/放电时钟、反向偏置时钟、高电位驱动电压以及低电位基准电压,并且以级联结构连接,其中所述多个信号传输器的第N信号传输器包括:第一控制节点;第二控制节点;用于通过使用被输入所述反向偏置时钟的至少一个晶体管控制所述第一控制节点的充电和放电的第一控制器;用于控制所述第二控制节点的充电和放电的第二控制器;用于响应于所述第一控制节点和所述第二控制节点的电压输出进位脉冲的第一输出缓存器;