栅极驱动电路以及包括栅极驱动电路的显示装置.pdf

靖烟****魔王

亲,该文档总共31页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

栅极驱动电路以及包括栅极驱动电路的显示装置.pdf

提供一种栅极驱动电路以及包括栅极驱动电路的显示装置。栅极驱动电路包括:多个信号传输器;以及多个第一缓存器,每个连接至多个信号传输器的其中之一并且包括:第一晶体管;以及第二晶体管,连接至第一晶体管,其中在第一和第二晶体管之间具有用于输出栅极脉冲的第一输出节点,其中多个信号传输器包括:第一控制器,在第一单位时间向第一控制器输入激活时钟时控制第一控制节点用作导通第一晶体管的上拉控制节点,并且在第二单位时间向第一控制器输入失活时钟时禁用;以及第二控制器,在第二单位时间向第二控制器输入激活时钟时控制第二控制节点用作

栅极驱动电路以及包括栅极驱动电路的显示装置.pdf

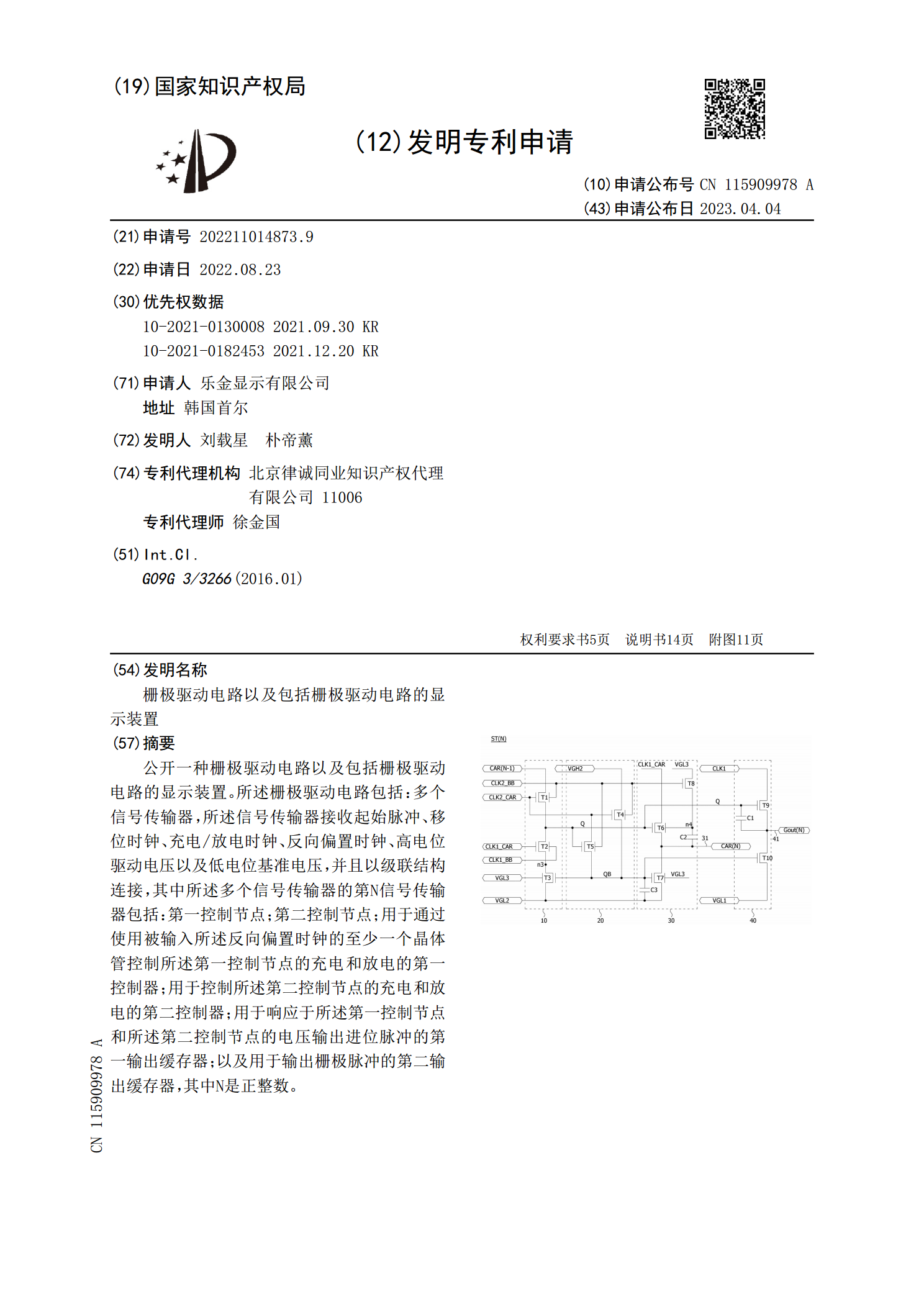

公开一种栅极驱动电路以及包括栅极驱动电路的显示装置。所述栅极驱动电路包括:多个信号传输器,所述信号传输器接收起始脉冲、移位时钟、充电/放电时钟、反向偏置时钟、高电位驱动电压以及低电位基准电压,并且以级联结构连接,其中所述多个信号传输器的第N信号传输器包括:第一控制节点;第二控制节点;用于通过使用被输入所述反向偏置时钟的至少一个晶体管控制所述第一控制节点的充电和放电的第一控制器;用于控制所述第二控制节点的充电和放电的第二控制器;用于响应于所述第一控制节点和所述第二控制节点的电压输出进位脉冲的第一输出缓存器;

栅极驱动电路以及包括该栅极驱动电路的显示装置.pdf

本申请涉及栅极驱动电路以及包括该栅极驱动电路的显示装置。栅极驱动电路可以包括依赖地彼此连接的多个级。多个级中的每个级可以包括:输出单元,用于响应于Q节点的电压和QB节点的电压而输出作为栅极输出电压的第一时钟信号;第一节点控制器,用于响应于来自前一级的输出信号而对Q节点的电压进行充电;第二节点控制器,用于响应于具有与第一时钟信号不同相位的第二时钟信号而对QB节点的电压进行充电;第一节点稳定器,用于在未施加第二时钟信号的情况下,阻挡Q节点的漏电流路径;以及第二节点稳定器,用于在未施加第二时钟信号,阻挡QB节点

栅极驱动电路和包括该栅极驱动电路的显示装置.pdf

提供了一种栅极驱动电路和包括该栅极驱动电路的显示装置。栅极驱动电路包括:用于输出在栅极导通电压和第一栅极截止电压之间摆动的第一扫描脉冲的第一输出部;用于输出在栅极导通电压和第二栅极截止电压之间摆动的第二扫描脉冲的第二输出部;以及用于控制第一和第二输出部的控制器。第一栅极截止电压被设定为高于或低于第二栅极截止电压。

栅极驱动电路以及使用该栅极驱动电路的显示装置.pdf

本发明公开了一种栅极驱动电路以及使用该栅极驱动电路的显示装置。该栅极驱动电路包括:第一移位寄存器,该第一移位寄存器配置为响应栅极移位时钟而使栅极起始脉冲顺序移位并且以每个块为基础输出被移位的栅极脉冲,每个块包括多条栅极线;第二移位寄存器,该第二移位寄存器配置为响应栅极移位时钟而使栅极起始脉冲顺序移位并且以每条栅极线为基础输出被移位的栅极脉冲;以及控制器,该控制器配置为将栅极移位时钟提供给第一移位寄存器和第二移位寄存器中的之一。