一种沟槽式肖特基势垒二极管整流器件及制造方法.pdf

小代****回来

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

沟槽式肖特基势垒二极管整流器件及制造方法.pdf

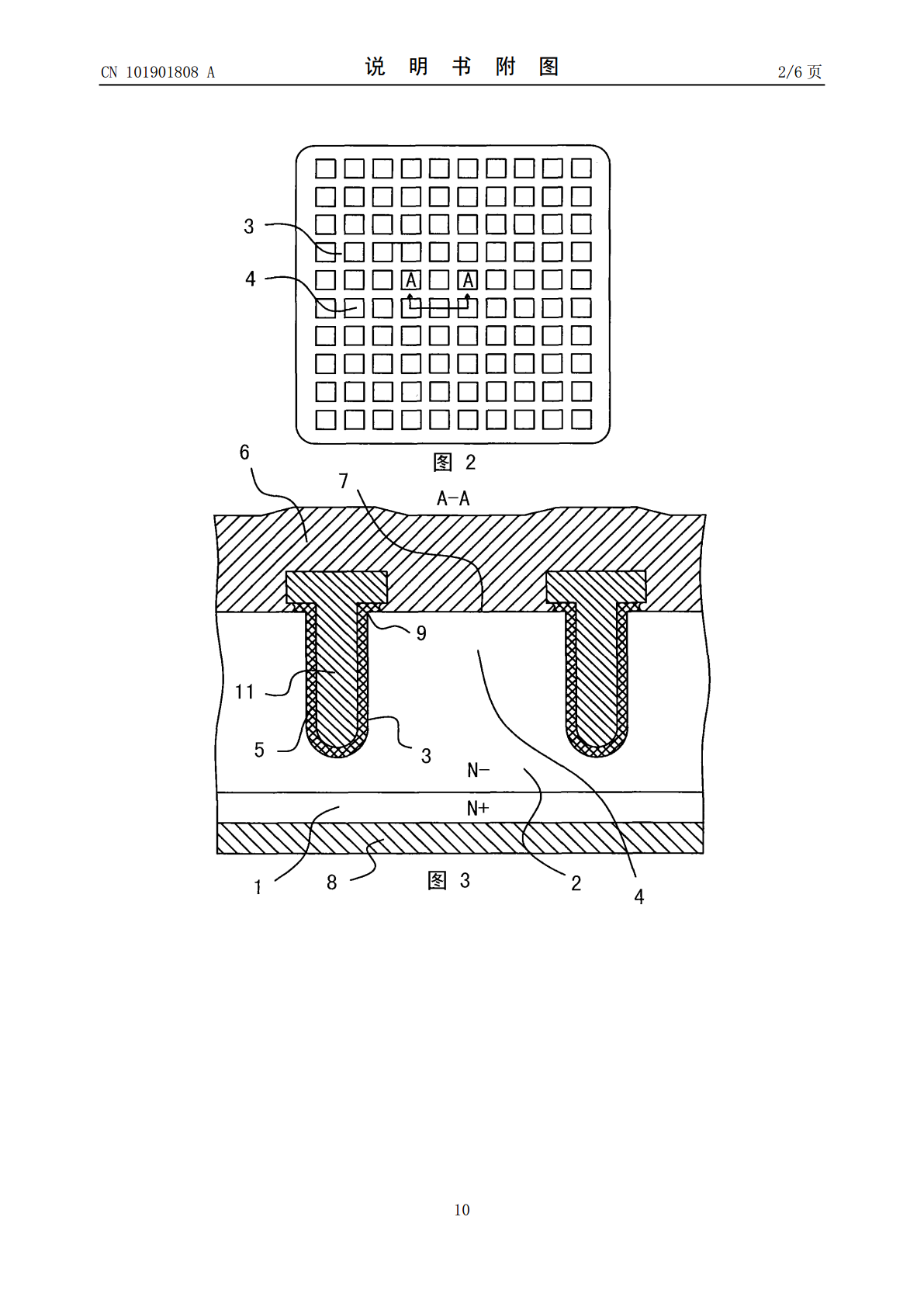

一种沟槽式肖特基势垒二极管整流器件及制造方法,本发明在现有沟槽式肖特基二极管整流器件基础上,利用沟槽中导电多晶硅T形头的两肩和延伸段二氧化硅层来遮蔽沟槽两侧的凸台结构顶角,克服凸台顶角与上金属层接触产生尖端放电效应,引起反向漏电变大,反向阻断能力下降的问题。在T形头的两侧面上设有介质侧墙,保护了凸台顶角侧面的二氧化硅层局部在制造过程中不受损伤,解决了凸台顶角侧面直接与上金属层接触,引起反向漏电变大,反向阻断能力下降的问题。另外,采用导电多晶硅替代常规上金属层铝、钛等材料来填充沟槽,一方面觖决了沟槽填充留下

一种沟槽式肖特基势垒二极管整流器件及制造方法.pdf

一种沟槽式肖特基势垒二极管整流器件及制造方法,本发明在现有沟槽式肖特基二极管整流器件基础上,利用沟槽中导电多晶硅T形头的两肩和延伸段二氧化硅层来遮蔽沟槽两侧的凸台结构顶角,克服凸台顶角与上金属层接触产生尖端放电效应,引起反向漏电变大,反向阻断能力下降的问题。另外,采用导电多晶硅替代常规上金属层铝、钛等材料来填充沟槽,一方面觖决了沟槽填充留下空洞,影响器件可靠性的问题,另一方面为器件的沟槽开口宽度与深度比例提供了更为灵活的设计空间。

一种沟槽栅IGBT器件及其制造方法.pdf

本发明公开了一种沟槽栅IGBT器件及其制造方法。该沟槽栅IGBT器件主要包括:P型基区;通过向P型基区注入N型离子而形成的两个第一N+掺杂区;两个沟槽,其宽度分别小于对应的两个第一N+掺杂区的宽度,使得两个沟槽在靠近彼此的一侧分别留有部分第一N+掺杂区;通过向位于两个部分第一N+掺杂区之间的P型基区注入N型离子而形成的第二N+掺杂区;接触孔,其底部的宽度小于第二N+掺杂区的宽度,使得接触孔两侧留有部分第二N+掺杂区;通过接触孔向P型基区的位于两个部分第一N+掺杂区之间的区域注入P型离子而形成的P+掺杂区;

沟槽型MOS器件的制造方法.pdf

本发明提供了一种沟槽型MOS器件的制造方法,采用碳膜层和氮氧化硅层作为硬掩膜层,所述碳膜层和所述氮氧化硅层具有很高的刻蚀选择比,由此,可以采用较薄的氮氧化硅层,以形成小尺寸的开口用以执行离子注入工艺并且还易于控制所形成的开口的形貌,从而能够将有源区注入结构的尺寸降下来,并进而可以减小整个MOS器件的尺寸。

沟槽功率器件及其制造方法.pdf

本发明提供一种沟槽功率器件及其制造方法,所述沟槽功率器件的制造方法包括:提供一衬底,包括器件单元区及电极连接区,并具有第一沟槽;形成隔离材料层,并以剩余的第一沟槽作为第二沟槽;形成屏蔽栅材料层;在第二沟槽中形成屏蔽栅,屏蔽栅具有平坦的顶面;在器件单元区的第一沟槽中形成控制栅结构。本发明中,通过形成具有平坦的顶面的屏蔽栅,从而可利用其平坦的顶面在后续形成控制栅结构的过程中防止控制栅材料层残留于屏蔽栅的顶面,进而减少或防止因在电极连接区引出屏蔽栅时因残留于屏蔽栅上的控制栅材料层与控制栅短路的风险。