用于制备应变沟道CMOS的等效应变记忆方法.pdf

闪闪****魔王

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

用于制备应变沟道CMOS的等效应变记忆方法.pdf

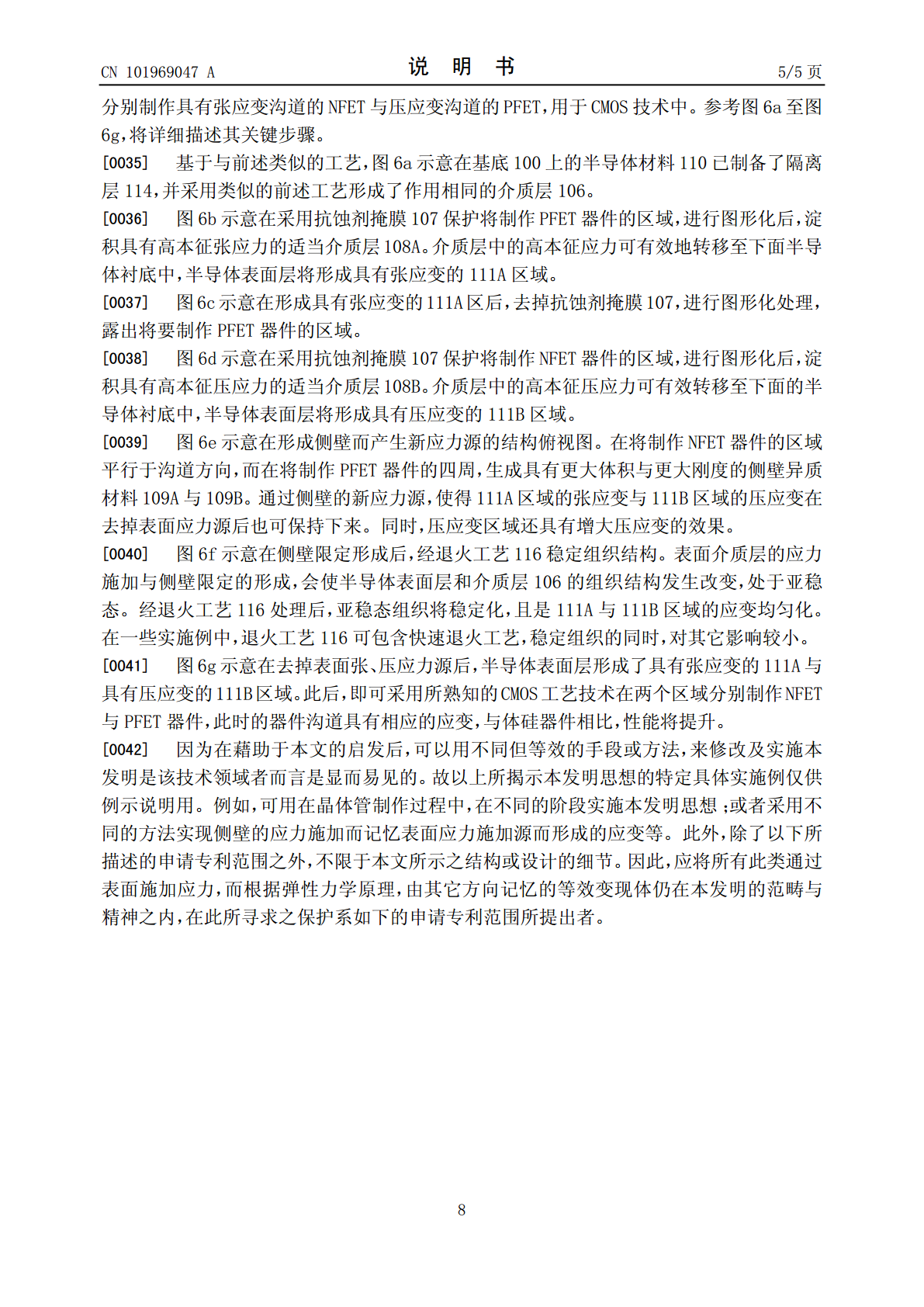

本发明制备应变沟道CMOS的等效应变记忆方法是涉及集成电路的制作,特别是通过等效应变记忆方法引入的应变技术,分别为互补金属氧化物半导体场效应晶体管CMOS中的NFET与PFET器件提供张应变与压应变。该发明提供的记忆方法是通过表面剪切应力在衬底表面引入应变,此应变的大小会随纵向深度不同而变化,但不随表面内横向尺寸的改变而变化,并通过侧壁正应力而保留沿沟道方向的等效应变。用本方法制作出来的晶体管在特征尺寸为几微米情况下,沟道仍具有较大应变,并能提高器件与电路的频率特性。

基于GOI的应变SiGe沟道槽型栅CMOS集成器件的制备方法.pdf

本发明涉及一种基于GOI的应变SiGe沟道槽型栅CMOS集成器件的制备方法,该制备方法包括:选取GOI衬底;生长N型应变SiGe层,离子注入工艺进行N型掺杂;在N型应变SiGe层表面生长N型Si帽层,形成增强型NMOS有源区和耗尽型PMOS有源区;在其之间形成隔离沟槽;采用刻蚀工艺在NMOS栅极区表面形成双倒梯形凹槽;在NMOS有源区和耗尽型PMOS有源区表面生长氧化层,利用干法刻蚀工艺形成PMOS栅介质层;离子注入工艺形成PMOS源漏区;生长栅极材料形成PMOS栅极;生长栅极材料以形成NMOS栅极;金属

应变硅MOSFET沟道应变的有限元研究.docx

应变硅MOSFET沟道应变的有限元研究随着现代集成电路制造技术的快速发展,芯片的成本不断降低,性能不断提高。然而,芯片制造技术已经进入到了纳米级别,达到甚至超过了物理的极限。因此,研究微米级别以下的应变硅MOSFET已成为了科研人员的热门话题。本文就该话题开展一定的研究。应变硅MOSFET的重要性应变硅MOSFET是一种通过向硅沟道施加应变来增强电子迁移效应的器件,它能够在当前的制造技术下提高集成电路中器件的性能。通过改变硅沟道的晶格结构,可以提高载流子迁移速率,从而提高器件的开关速度和性能。这种技术的研

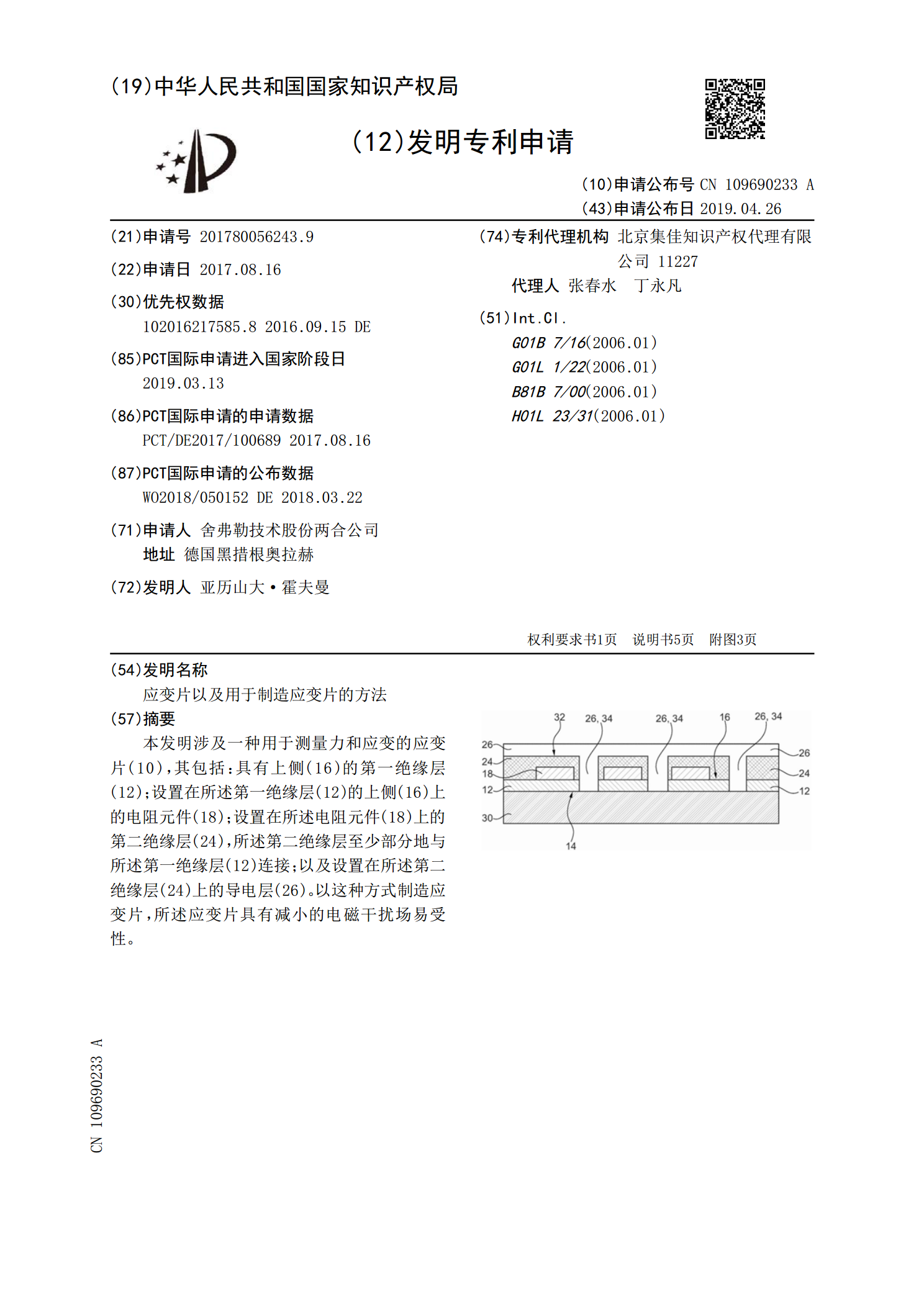

应变片以及用于制造应变片的方法.pdf

本发明涉及一种用于测量力和应变的应变片(10),其包括:具有上侧(16)的第一绝缘层(12);设置在所述第一绝缘层(12)的上侧(16)上的电阻元件(18);设置在所述电阻元件(18)上的第二绝缘层(24),所述第二绝缘层至少部分地与所述第一绝缘层(12)连接;以及设置在所述第二绝缘层(24)上的导电层(26)。以这种方式制造应变片,所述应变片具有减小的电磁干扰场易受性。

应变硅NMOS晶体管沟道应变的模拟研究.docx

应变硅NMOS晶体管沟道应变的模拟研究1.引言近年来,随着科学技术的不断发展,芯片制造技术也得到了长足的发展。这其中,应变硅技术在制造高性能芯片中已经得到了广泛的应用。应变硅技术通过在晶体管沟道中引入应力,从而改变电子传输的能带结构,提高晶体管的电性能。因此,研究应变硅NMOS晶体管沟道应变的模拟研究对芯片性能的提高具有重要的意义。2.应变硅效应介绍应变硅效应是指在硅芯片中施加应力,从而改变晶体管沟道电子能带结构,使得晶体管的电性能得到提高的现象。在晶体管中,源、漏端之间的沟道是电子传输的主要通道。通过引