半导体集成电感的制作方法及结构.pdf

秋花****姐姐

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

半导体集成电感的制作方法及结构.pdf

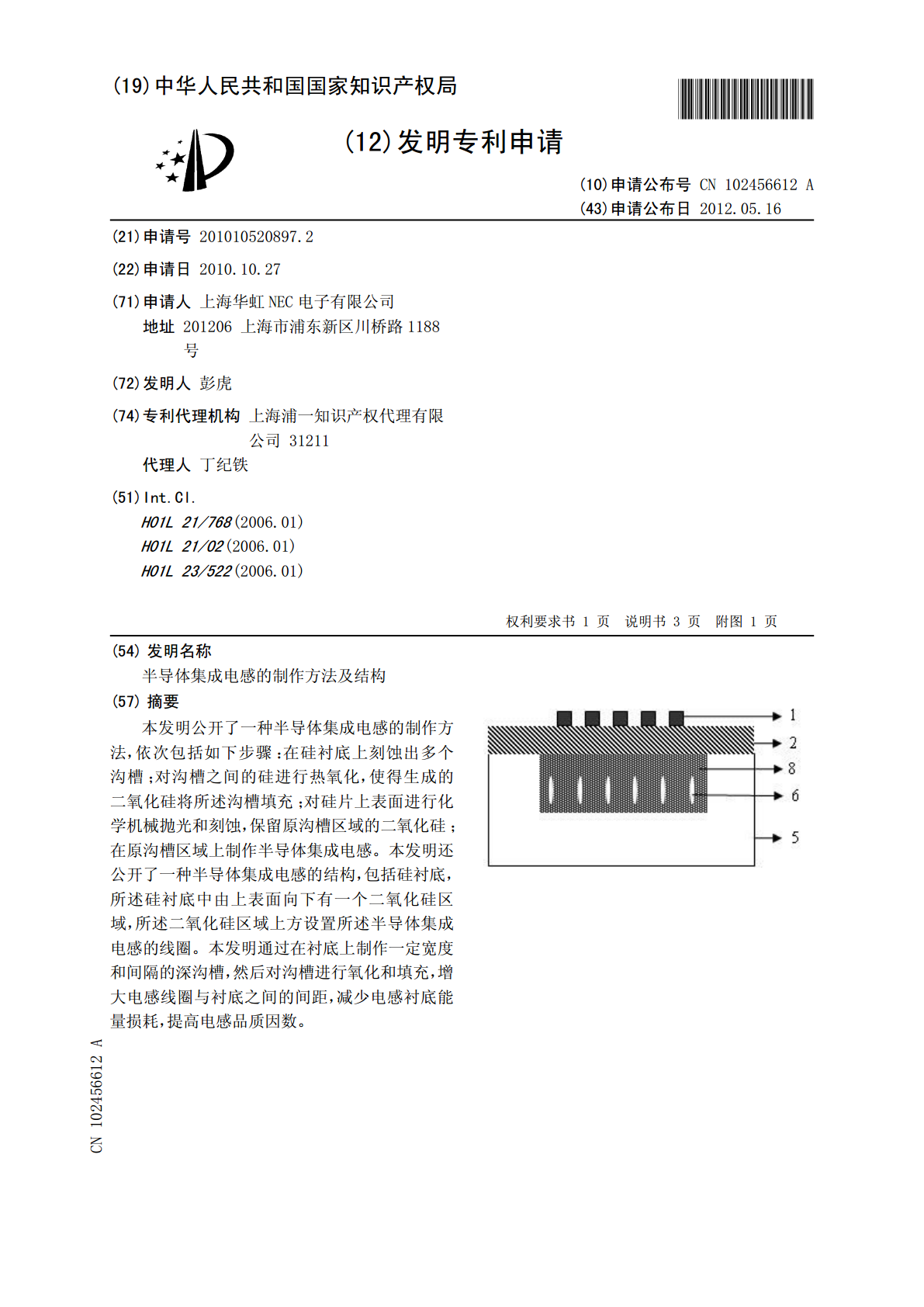

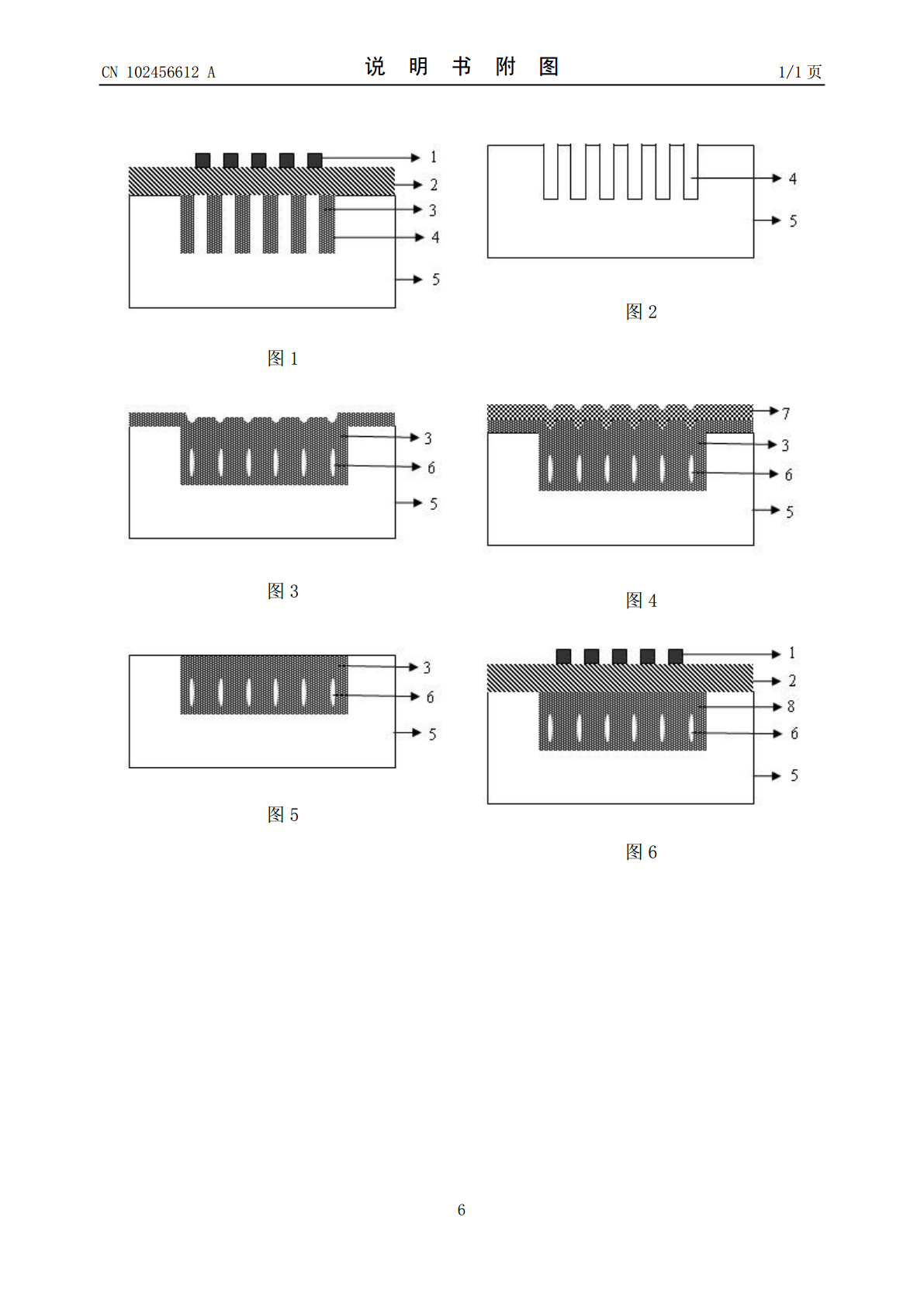

本发明公开了一种半导体集成电感的制作方法,依次包括如下步骤:在硅衬底上刻蚀出多个沟槽;对沟槽之间的硅进行热氧化,使得生成的二氧化硅将所述沟槽填充;对硅片上表面进行化学机械抛光和刻蚀,保留原沟槽区域的二氧化硅;在原沟槽区域上制作半导体集成电感。本发明还公开了一种半导体集成电感的结构,包括硅衬底,所述硅衬底中由上表面向下有一个二氧化硅区域,所述二氧化硅区域上方设置所述半导体集成电感的线圈。本发明通过在衬底上制作一定宽度和间隔的深沟槽,然后对沟槽进行氧化和填充,增大电感线圈与衬底之间的间距,减少电感衬底能量损耗

集成电感结构及制作方法.pdf

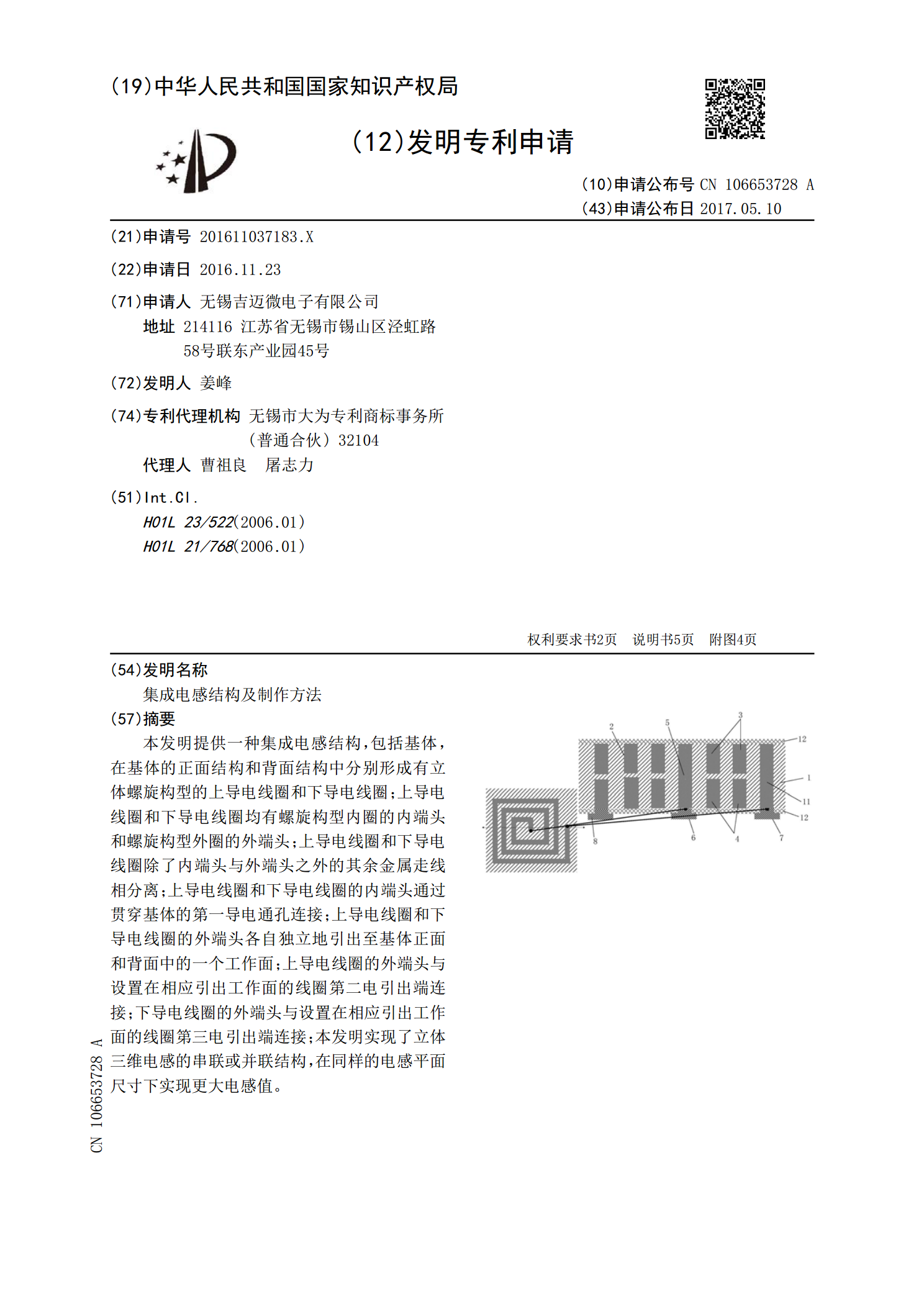

本发明提供一种集成电感结构,包括基体,在基体的正面结构和背面结构中分别形成有立体螺旋构型的上导电线圈和下导电线圈;上导电线圈和下导电线圈均有螺旋构型内圈的内端头和螺旋构型外圈的外端头;上导电线圈和下导电线圈除了内端头与外端头之外的其余金属走线相分离;上导电线圈和下导电线圈的内端头通过贯穿基体的第一导电通孔连接;上导电线圈和下导电线圈的外端头各自独立地引出至基体正面和背面中的一个工作面;上导电线圈的外端头与设置在相应引出工作面的线圈第二电引出端连接;下导电线圈的外端头与设置在相应引出工作面的线圈第三电引出端

半导体结构制作方法及半导体结构.pdf

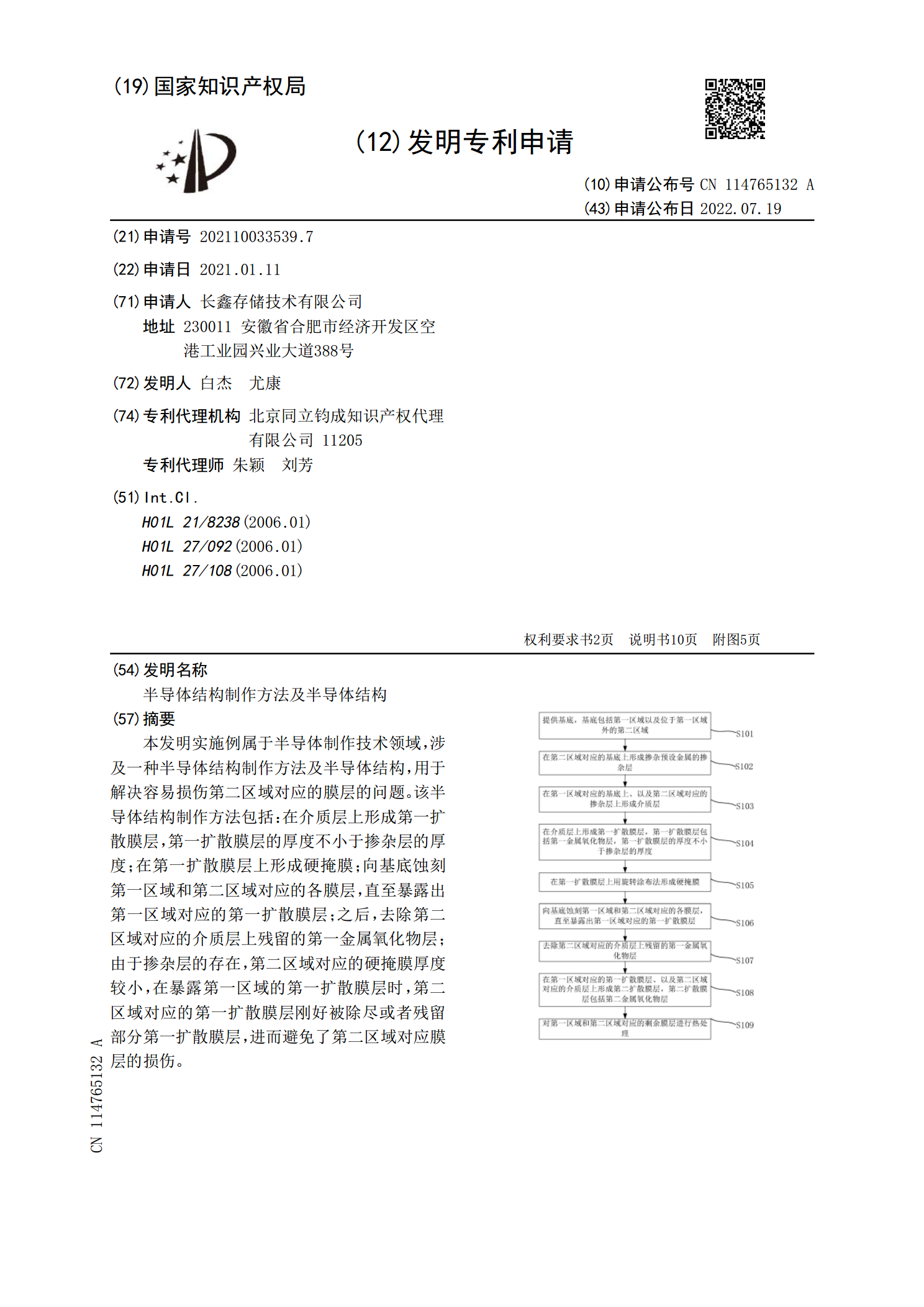

本发明实施例属于半导体制作技术领域,涉及一种半导体结构制作方法及半导体结构,用于解决容易损伤第二区域对应的膜层的问题。该半导体结构制作方法包括:在介质层上形成第一扩散膜层,第一扩散膜层的厚度不小于掺杂层的厚度;在第一扩散膜层上形成硬掩膜;向基底蚀刻第一区域和第二区域对应的各膜层,直至暴露出第一区域对应的第一扩散膜层;之后,去除第二区域对应的介质层上残留的第一金属氧化物层;由于掺杂层的存在,第二区域对应的硬掩膜厚度较小,在暴露第一区域的第一扩散膜层时,第二区域对应的第一扩散膜层刚好被除尽或者残留部分第一扩散

半导体结构制作方法及半导体结构.pdf

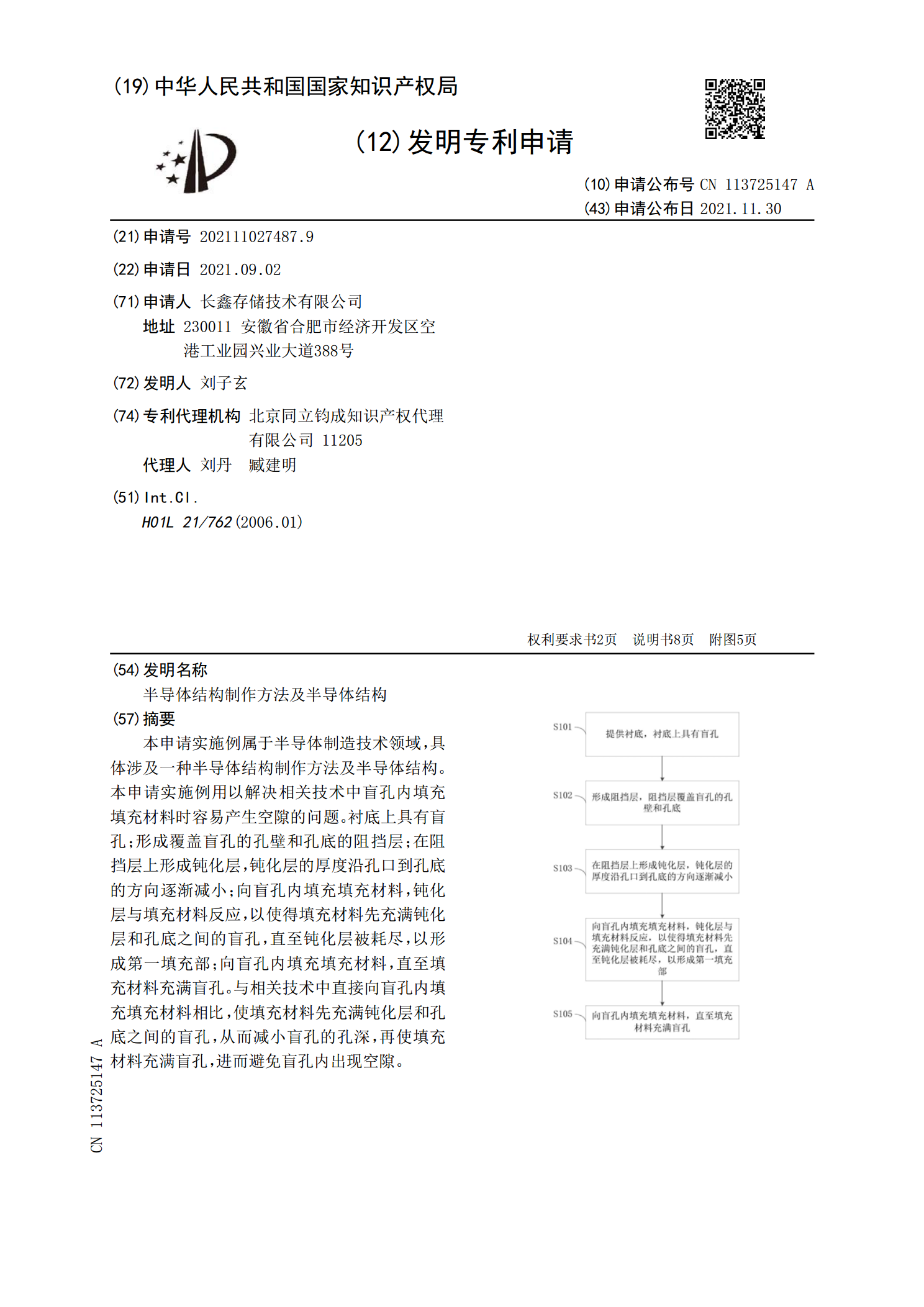

本申请实施例属于半导体制造技术领域,具体涉及一种半导体结构制作方法及半导体结构。本申请实施例用以解决相关技术中盲孔内填充填充材料时容易产生空隙的问题。衬底上具有盲孔;形成覆盖盲孔的孔壁和孔底的阻挡层;在阻挡层上形成钝化层,钝化层的厚度沿孔口到孔底的方向逐渐减小;向盲孔内填充填充材料,钝化层与填充材料反应,以使得填充材料先充满钝化层和孔底之间的盲孔,直至钝化层被耗尽,以形成第一填充部;向盲孔内填充填充材料,直至填充材料充满盲孔。与相关技术中直接向盲孔内填充填充材料相比,使填充材料先充满钝化层和孔底之间的盲孔

单片集成半导体结构.pdf

本发明涉及一种包含下列层结构的单片集成半导体结构:A)基于掺杂的或未掺杂的Si的载体层,B)任选地具有组成BxAly-GazNtPv的层,其中x=0-0.1,y=0-1,z=0-1,t=0-0.1和v=0.9-1,C)具有组成BxAly-GazInuPvSbw的松弛层,其中x=0-0.1,y=0-1,z=0-1,u=0-1,v=0-1和w=0-1,其中w和/或u在朝向层A)或B)的一侧小于、等于或大于其在背离层A)或B)的一侧,和其中v=1-w和/或y=1-u-x-z,D)任选地具有组成BxAlyGazI