一种叠层芯片的晶圆级铜凸块封装结构.pdf

鸿朗****ka

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种叠层芯片的晶圆级铜凸块封装结构.pdf

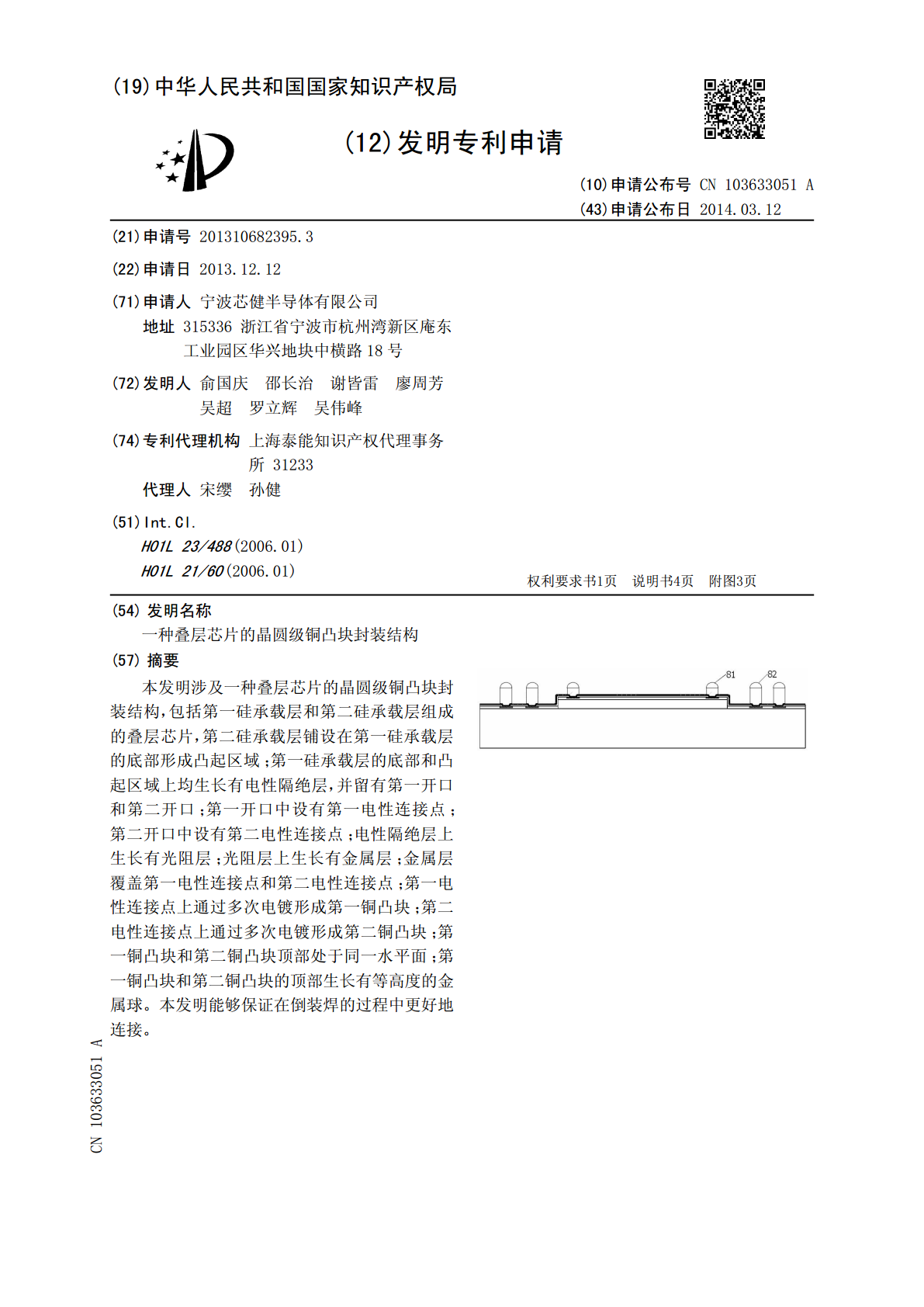

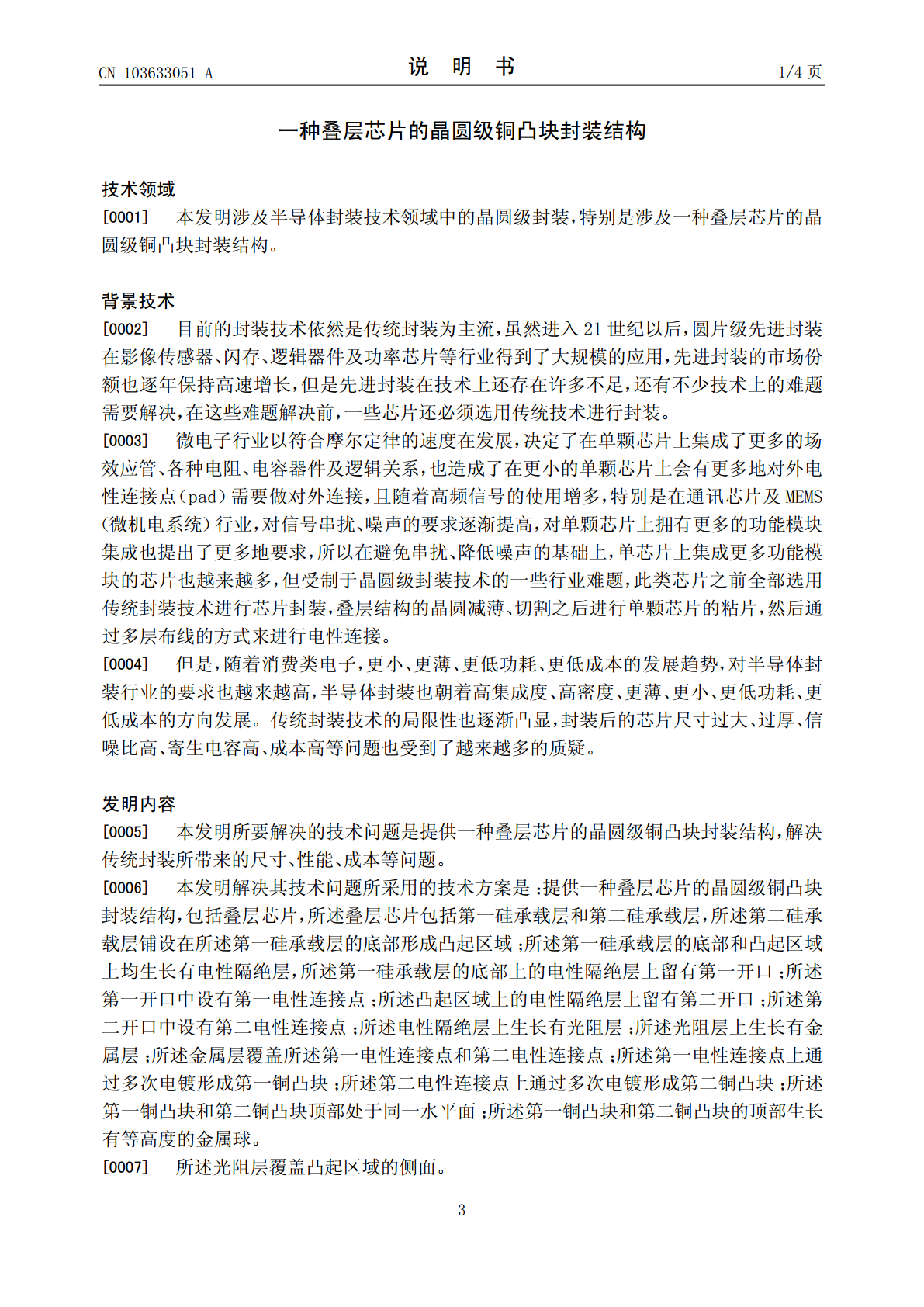

本发明涉及一种叠层芯片的晶圆级铜凸块封装结构,包括第一硅承载层和第二硅承载层组成的叠层芯片,第二硅承载层铺设在第一硅承载层的底部形成凸起区域;第一硅承载层的底部和凸起区域上均生长有电性隔绝层,并留有第一开口和第二开口;第一开口中设有第一电性连接点;第二开口中设有第二电性连接点;电性隔绝层上生长有光阻层;光阻层上生长有金属层;金属层覆盖第一电性连接点和第二电性连接点;第一电性连接点上通过多次电镀形成第一铜凸块;第二电性连接点上通过多次电镀形成第二铜凸块;第一铜凸块和第二铜凸块顶部处于同一水平面;第一铜凸块和

一种用于覆晶封装芯片的凸块结构.pdf

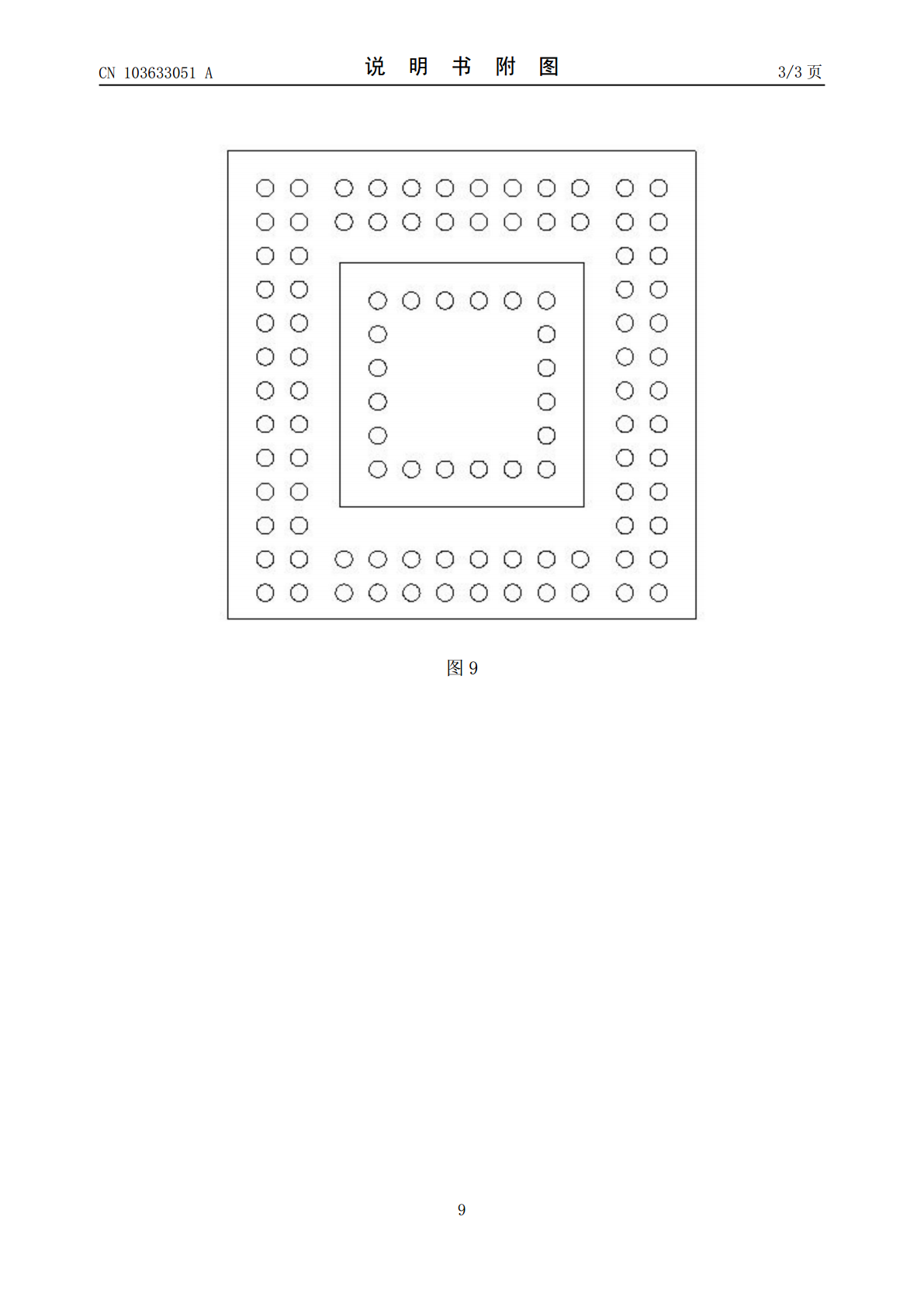

本发明公开了一种用于覆晶封装芯片的凸块结构,该凸块结构包括在凸块顶面布置的导流式凹槽,该凹槽居中地布置在凸块顶面上且贯穿凸块整个表面,其两端具有开口,仅在左右两侧形成凸起边界。与回字型凸起边界的凸块结构相比,本发明采用导流式凹槽凸块结构,在薄膜覆晶封装应用和卷带式覆晶封装应用时效果更优越。

晶圆级芯片封装结构及封装方法.pdf

本发明涉及晶圆级芯片封装结构及制造方法,包括芯片单元,其具有相对设置的第一表面和第二表面,所述第一表面布置至少一个用于电联接的焊窗;所述第二表面设置与焊窗连接的TSV结构,所述TSV结构包括贯穿第一表面和第二表面的通孔和在第二表面设置的开槽,开槽的边界距离第二表面的边缘大于10um。相对现有技术获得的进步是提高了芯片的结构强度。

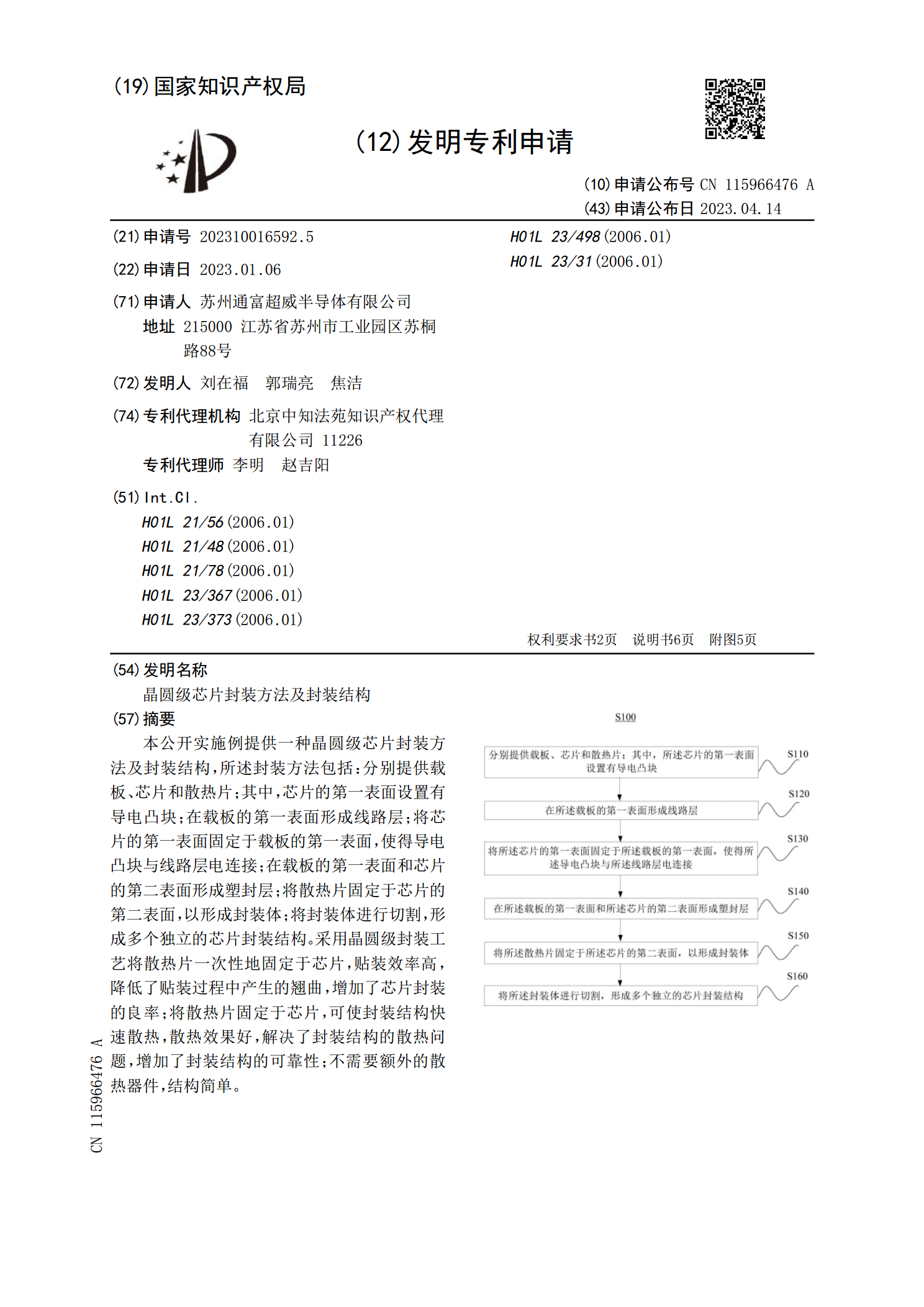

晶圆级芯片封装方法及封装结构.pdf

本公开实施例提供一种晶圆级芯片封装方法及封装结构,所述封装方法包括:分别提供载板、芯片和散热片;其中,芯片的第一表面设置有导电凸块;在载板的第一表面形成线路层;将芯片的第一表面固定于载板的第一表面,使得导电凸块与线路层电连接;在载板的第一表面和芯片的第二表面形成塑封层;将散热片固定于芯片的第二表面,以形成封装体;将封装体进行切割,形成多个独立的芯片封装结构。采用晶圆级封装工艺将散热片一次性地固定于芯片,贴装效率高,降低了贴装过程中产生的翘曲,增加了芯片封装的良率;将散热片固定于芯片,可使封装结构快速散热,

晶圆级芯片封装方法、晶圆级芯片封装结构和电子设备.pdf

本申请提供了一种晶圆级芯片封装方法、晶圆级芯片封装结构和电子设备,涉及半导体领域。晶圆级芯片封装方法包括在基材正面铺设贴片膜,在贴片膜上贴装晶粒,利用塑封材料对晶粒进行晶圆级塑封,并制作电连接于晶粒的锡球,然后从基材的背面去除部分基材的材料,以减薄基材的厚度。在本申请实施例中,最终并不移出基材,而是保留部分基材。减薄后基材的厚度可以根据整体封装结构的尺寸来决定。由于保留了部分基材,基材具有一定结构强度,能够起到较佳的支撑作用,来抵抗塑封体中的应力,避免变形。这样制作出来的整个晶圆级芯片封装结构不容易存在翘