低温多晶硅TFT阵列基板的制作方法.pdf

猫巷****傲柏

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

低温多晶硅TFT阵列基板的制作方法.pdf

本发明提供一种低温多晶硅TFT阵列基板的制作方法,该方法通过连续两次光阻灰化和去光阻处理将离子掺杂后残留的固化光阻完全去除干净,有效解决光阻层在第一次灰化处理之前某些区域可能覆盖有杂质颗粒而阻挡第一次灰化处理造成的固化光阻残留的问题,能够改善栅极绝缘层和层间绝缘层的界面清洁度,避免界面问题导致的产品良率下降。

TFT阵列基板的制作方法.pdf

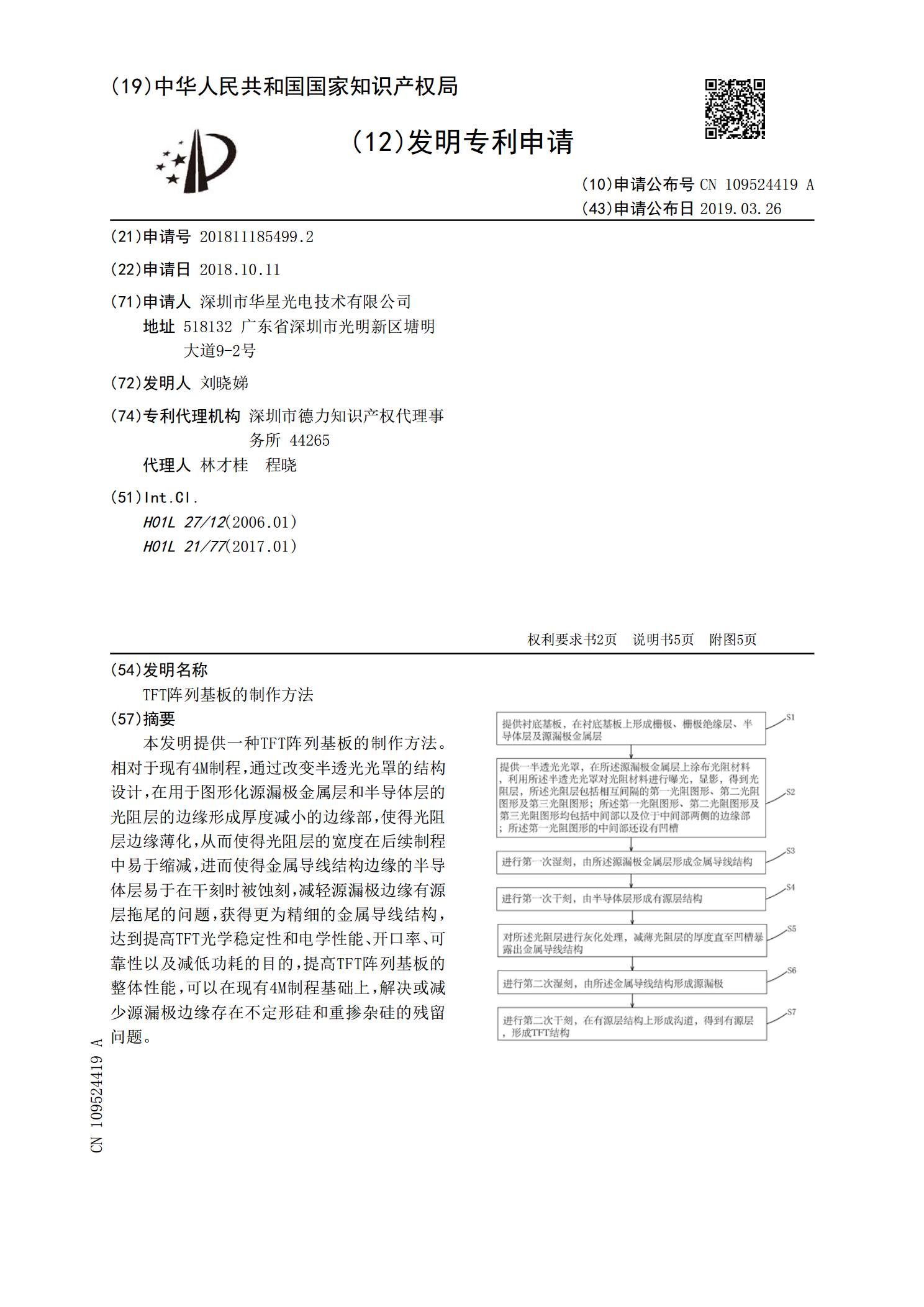

本发明提供一种TFT阵列基板的制作方法。相对于现有4M制程,通过改变半透光光罩的结构设计,在用于图形化源漏极金属层和半导体层的光阻层的边缘形成厚度减小的边缘部,使得光阻层边缘薄化,从而使得光阻层的宽度在后续制程中易于缩减,进而使得金属导线结构边缘的半导体层易于在干刻时被蚀刻,减轻源漏极边缘有源层拖尾的问题,获得更为精细的金属导线结构,达到提高TFT光学稳定性和电学性能、开口率、可靠性以及减低功耗的目的,提高TFT阵列基板的整体性能,可以在现有4M制程基础上,解决或减少源漏极边缘存在不定形硅和重掺杂硅的残留

TFT阵列基板的制作方法.pdf

本发明提供一种TFT阵列基板的制作方法,以半色调掩膜板(3)为工具进行曝光,使得第二金属层(M2)中放电TFT(T3)的漏极(D3)及其爬坡处的上方保留薄层的光阻(PR),在后续的干法蚀刻过程中被保留的薄层的光阻(PR)对位于所述放电TFT(T3)的漏极(D3)的爬坡处以下的栅极绝缘层(GI)进行保护,避免栅极绝缘层(GI)在放电TFT(T3)的漏极(D3)的爬坡处因材质差异发生过蚀刻及底切问题,降低导电薄膜(9)破膜的风险,使得放电TFT(T3)的漏极(D3)与公共电压线(Com)之间的桥接可靠,且不会

TFT阵列基板的制作方法.pdf

本发明提供一种TFT阵列基板的制作方法,在源极与漏极上涂布形成平坦层后,先不做过孔处理,然后沉积并图案化公共电极层、沉积并图案化钝化保护层,在钝化保护层上形成过孔至露出平坦层后,再对平坦层进行灰化处理形成过孔以露出漏极,相比于现有的先在平坦层形成过孔后再沉积并图案化公共电极层的方法,该方法不会导致图案化公共电极层时导电材料残留于平坦层的过孔内而使平坦层过孔处出现短路的问题,另外在像素区域内在平坦层上通过采用灰化处理的干蚀刻方式形成过孔,可使形成的过孔具有较高的斜坡角度,从而一定程度可减少TFT的大小,有利

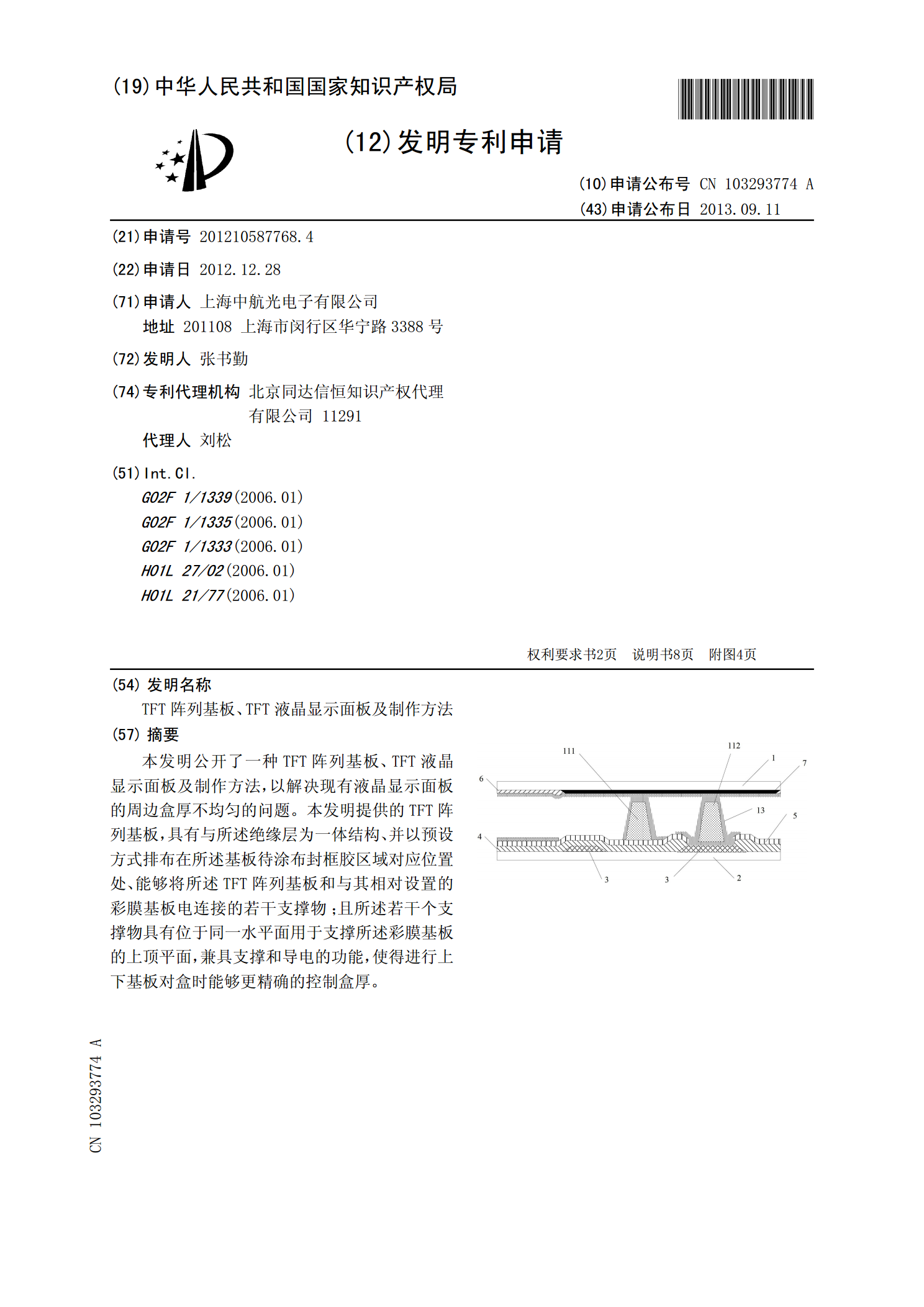

TFT阵列基板、TFT液晶显示面板及制作方法.pdf

本发明公开了一种TFT阵列基板、TFT液晶显示面板及制作方法,以解决现有液晶显示面板的周边盒厚不均匀的问题。本发明提供的TFT阵列基板,具有与所述绝缘层为一体结构、并以预设方式排布在所述基板待涂布封框胶区域对应位置处、能够将所述TFT阵列基板和与其相对设置的彩膜基板电连接的若干支撑物;且所述若干个支撑物具有位于同一水平面用于支撑所述彩膜基板的上顶平面,兼具支撑和导电的功能,使得进行上下基板对盒时能够更精确的控制盒厚。