一种浮栅及其制备方法.pdf

是向****23

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种浮栅及其制备方法.pdf

本发明公开了一种浮栅及其制备方法。所述制备方法包括:在衬底上依次形成衬垫氧化层和保护介质层,对所述保护介质层、所述衬垫氧化层和所述衬底进行图像化处理,形成有源区和浅沟槽隔离区,并对所述浅沟槽隔离区进行氧化层填充;剥离剩余保护介质层形成第一凹槽;在所述第一凹槽内壁上形成侧墙;去除剩余衬垫氧化层,以保留靠近所述侧墙的浅沟槽氧化层;依次去除所述侧墙和多余的浅沟槽氧化层,形成第二凹槽;在所述第二凹槽内露出的有源区上形成隧穿氧化层;在所述隧穿氧化层上形成栅极。本发明实施例提供的技术方案,在保证衬垫氧化层去除干净的前

一种浮栅的制备方法.pdf

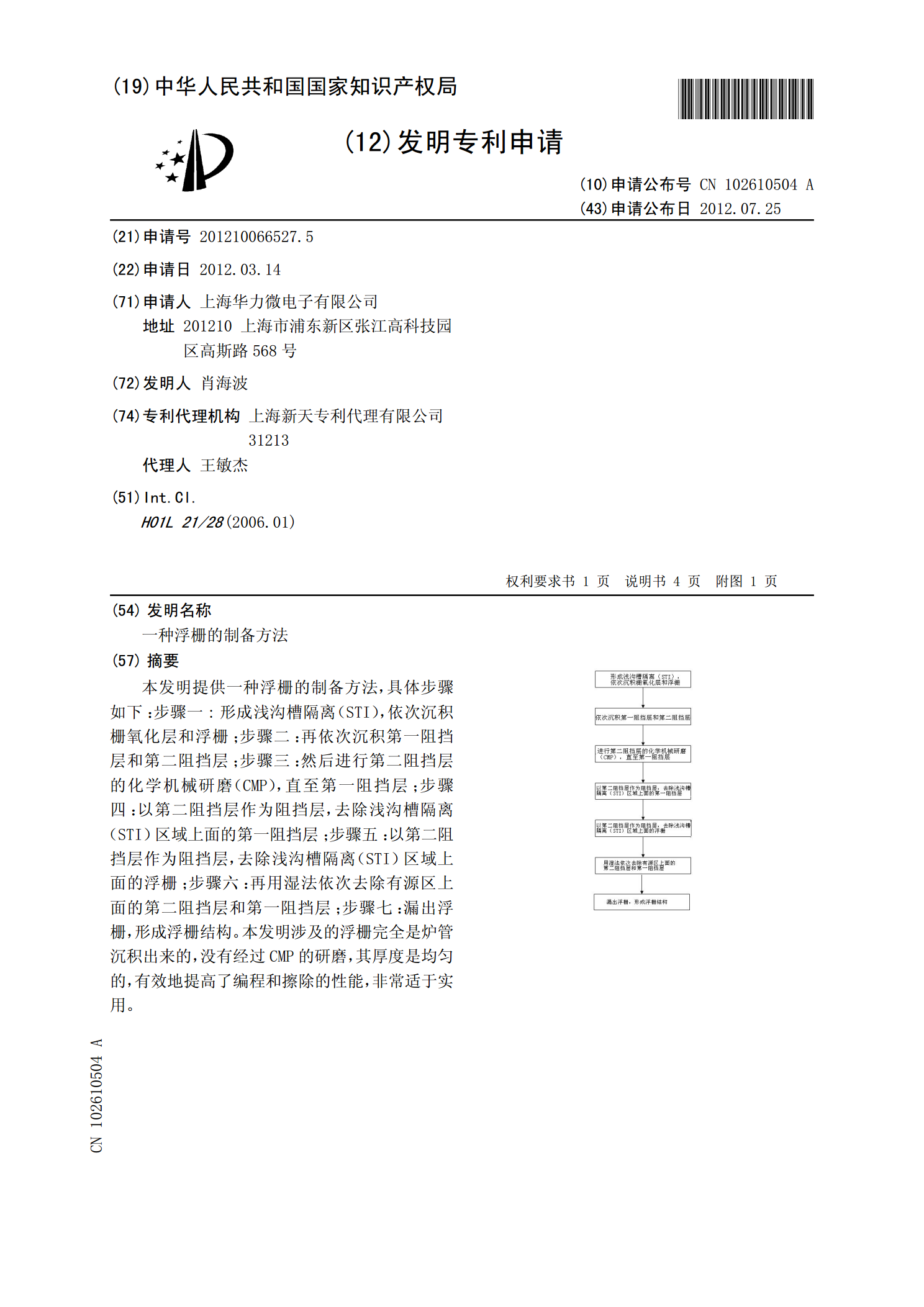

本发明提供一种浮栅的制备方法,具体步骤如下:步骤一:形成浅沟槽隔离(STI),依次沉积栅氧化层和浮栅;步骤二:再依次沉积第一阻挡层和第二阻挡层;步骤三:然后进行第二阻挡层的化学机械研磨(CMP),直至第一阻挡层;步骤四:以第二阻挡层作为阻挡层,去除浅沟槽隔离(STI)区域上面的第一阻挡层;步骤五:以第二阻挡层作为阻挡层,去除浅沟槽隔离(STI)区域上面的浮栅;步骤六:再用湿法依次去除有源区上面的第二阻挡层和第一阻挡层;步骤七:漏出浮栅,形成浮栅结构。本发明涉及的浮栅完全是炉管沉积出来的,没有经过CMP的研

浮栅的制备方法.pdf

本发明公开了一种浮栅的制备方法,包括提供一基底,在基底上自下至上依次形成浮栅层及掩膜层;在浮栅层和掩膜层中形成一沟槽,并在沟槽的两内侧形成第一侧墙;去除掩膜层,暴露出浮栅层;在暴露的浮栅层的上表面形成一浮栅保护层;对浮栅保护层和浮栅层进行浮栅刻蚀工艺,保留第一侧墙下方的浮栅层,以形成浮栅;在浮栅刻蚀工艺的击穿步刻蚀中,击穿步刻蚀的时间等于刻蚀浮栅保护层的固定时间与刻蚀部分浮栅层的时间之和。本发明通过上述击穿步刻蚀可以防止因所述浮栅层的厚度偏厚而导致浮栅尖端过高的现象,确保后续形成稳定的浮栅尖端,保证闪存性

一种边缘接触的高速浮栅存储器及其制备方法.pdf

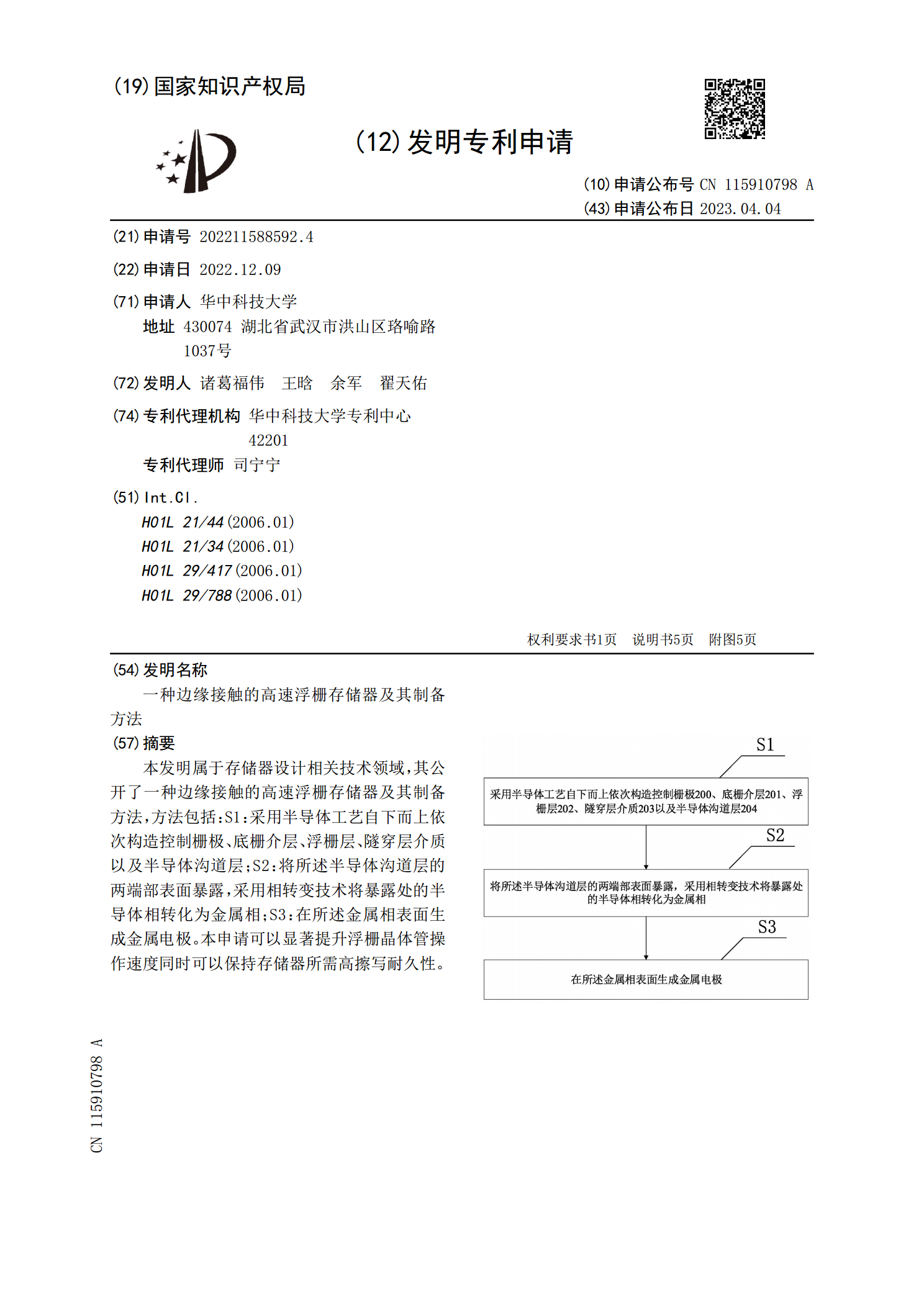

本发明属于存储器设计相关技术领域,其公开了一种边缘接触的高速浮栅存储器及其制备方法,方法包括:S1:采用半导体工艺自下而上依次构造控制栅极、底栅介层、浮栅层、隧穿层介质以及半导体沟道层;S2:将所述半导体沟道层的两端部表面暴露,采用相转变技术将暴露处的半导体相转化为金属相;S3:在所述金属相表面生成金属电极。本申请可以显著提升浮栅晶体管操作速度同时可以保持存储器所需高擦写耐久性。

一种二硫化铪为沟道的浮栅结构晶体管及其制备方法.pdf

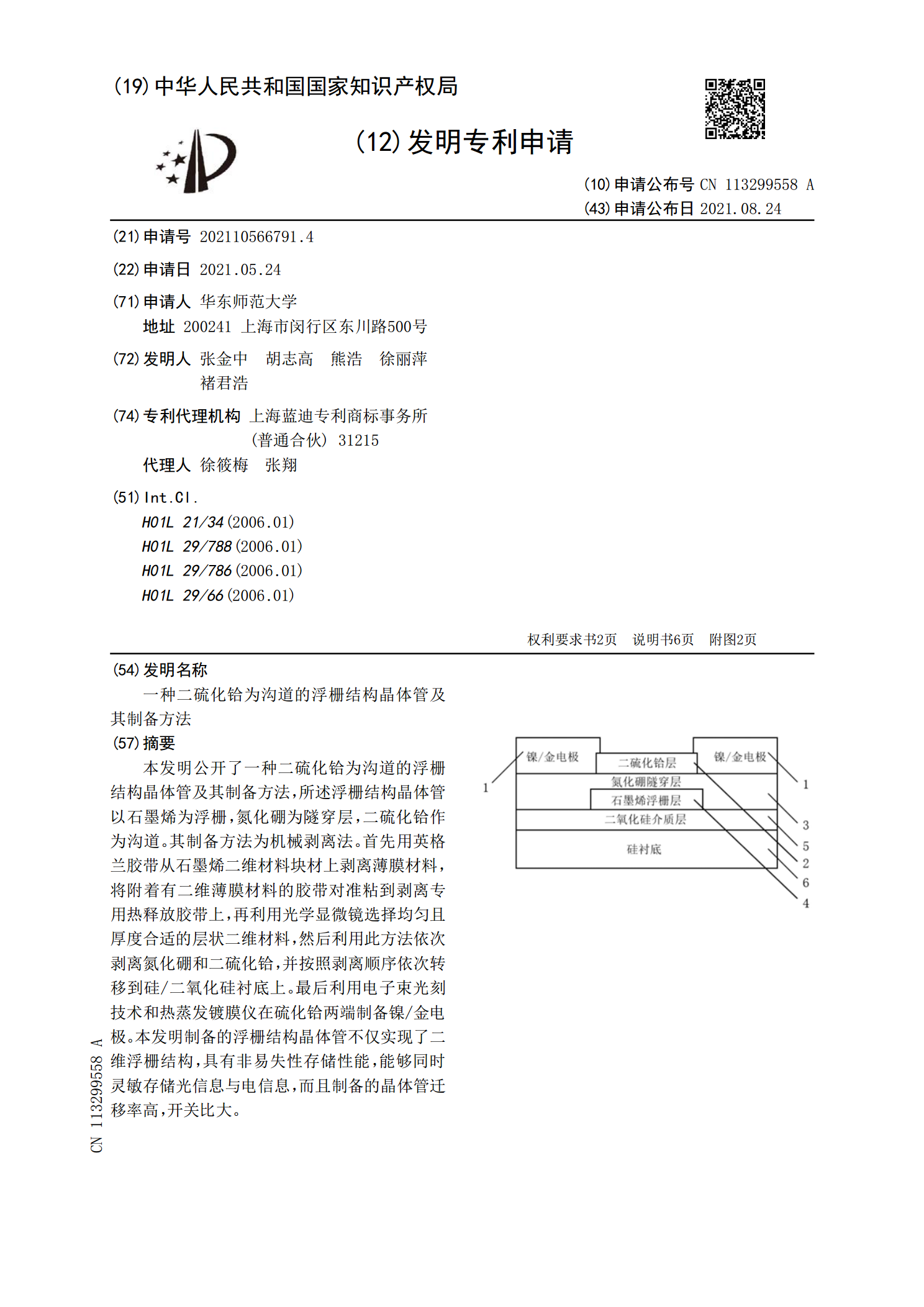

本发明公开了一种二硫化铪为沟道的浮栅结构晶体管及其制备方法,所述浮栅结构晶体管以石墨烯为浮栅,氮化硼为隧穿层,二硫化铪作为沟道。其制备方法为机械剥离法。首先用英格兰胶带从石墨烯二维材料块材上剥离薄膜材料,将附着有二维薄膜材料的胶带对准粘到剥离专用热释放胶带上,再利用光学显微镜选择均匀且厚度合适的层状二维材料,然后利用此方法依次剥离氮化硼和二硫化铪,并按照剥离顺序依次转移到硅/二氧化硅衬底上。最后利用电子束光刻技术和热蒸发镀膜仪在硫化铪两端制备镍/金电极。本发明制备的浮栅结构晶体管不仅实现了二维浮栅结构,具