一种边缘接触的高速浮栅存储器及其制备方法.pdf

是丹****ni

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种边缘接触的高速浮栅存储器及其制备方法.pdf

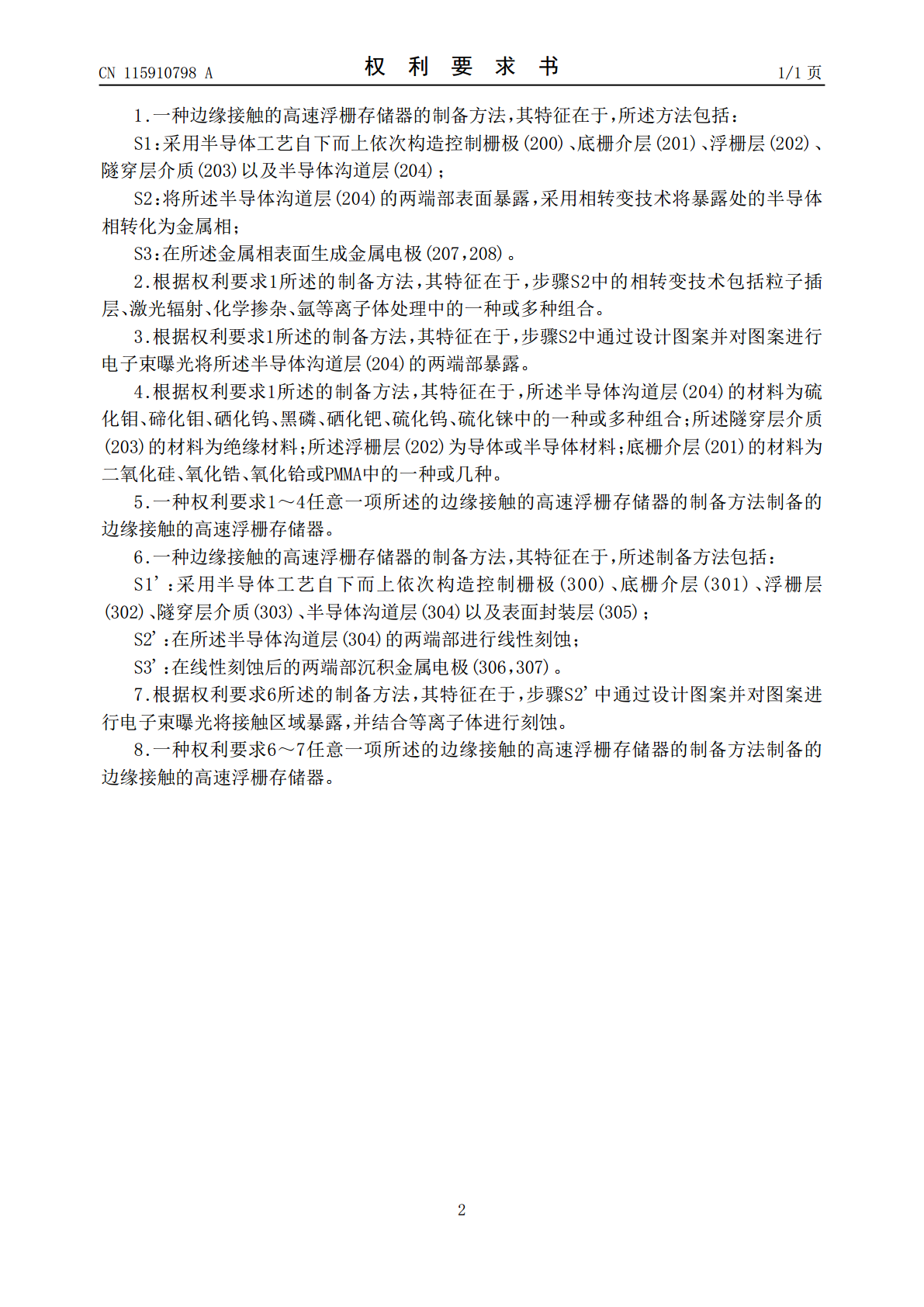

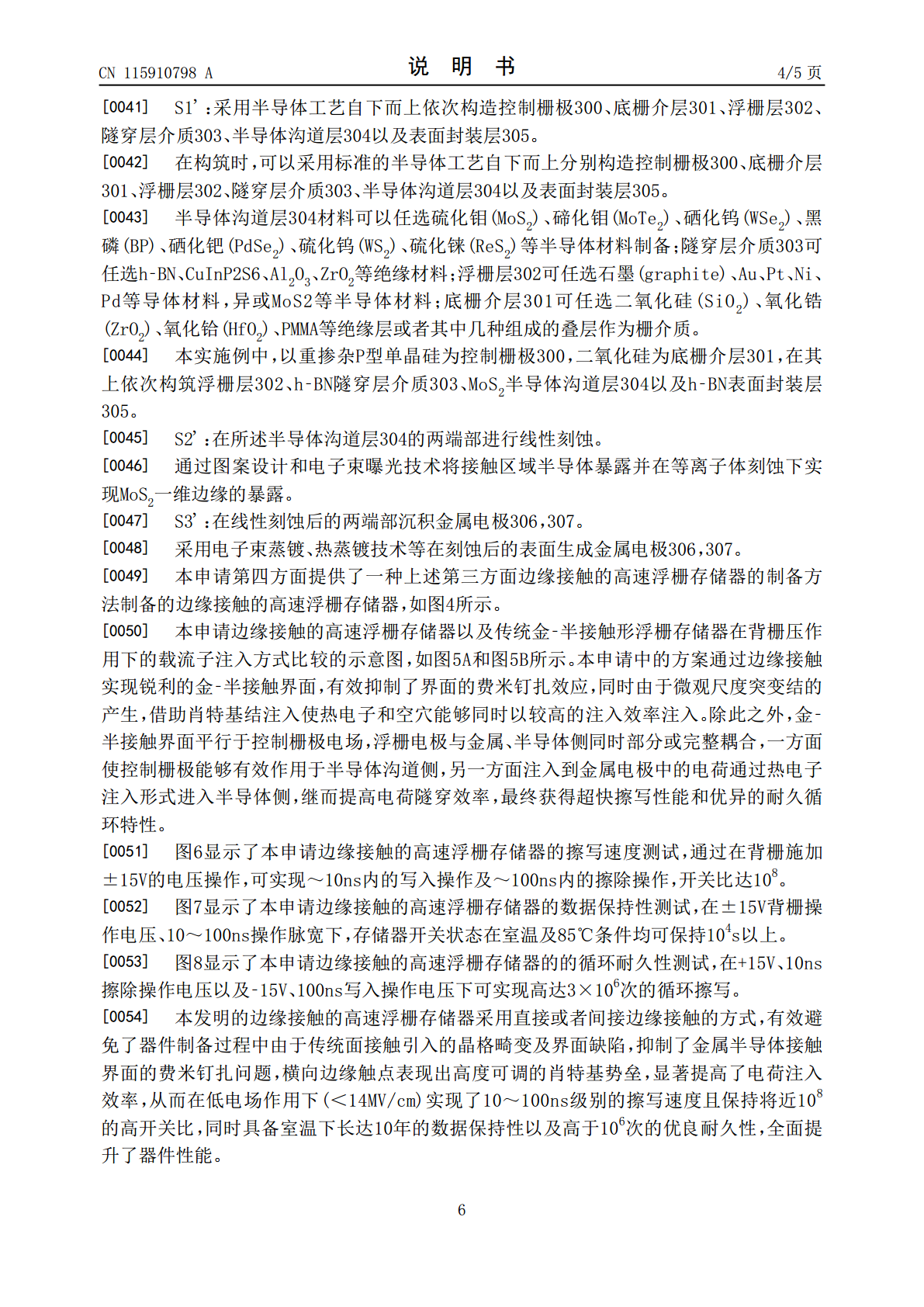

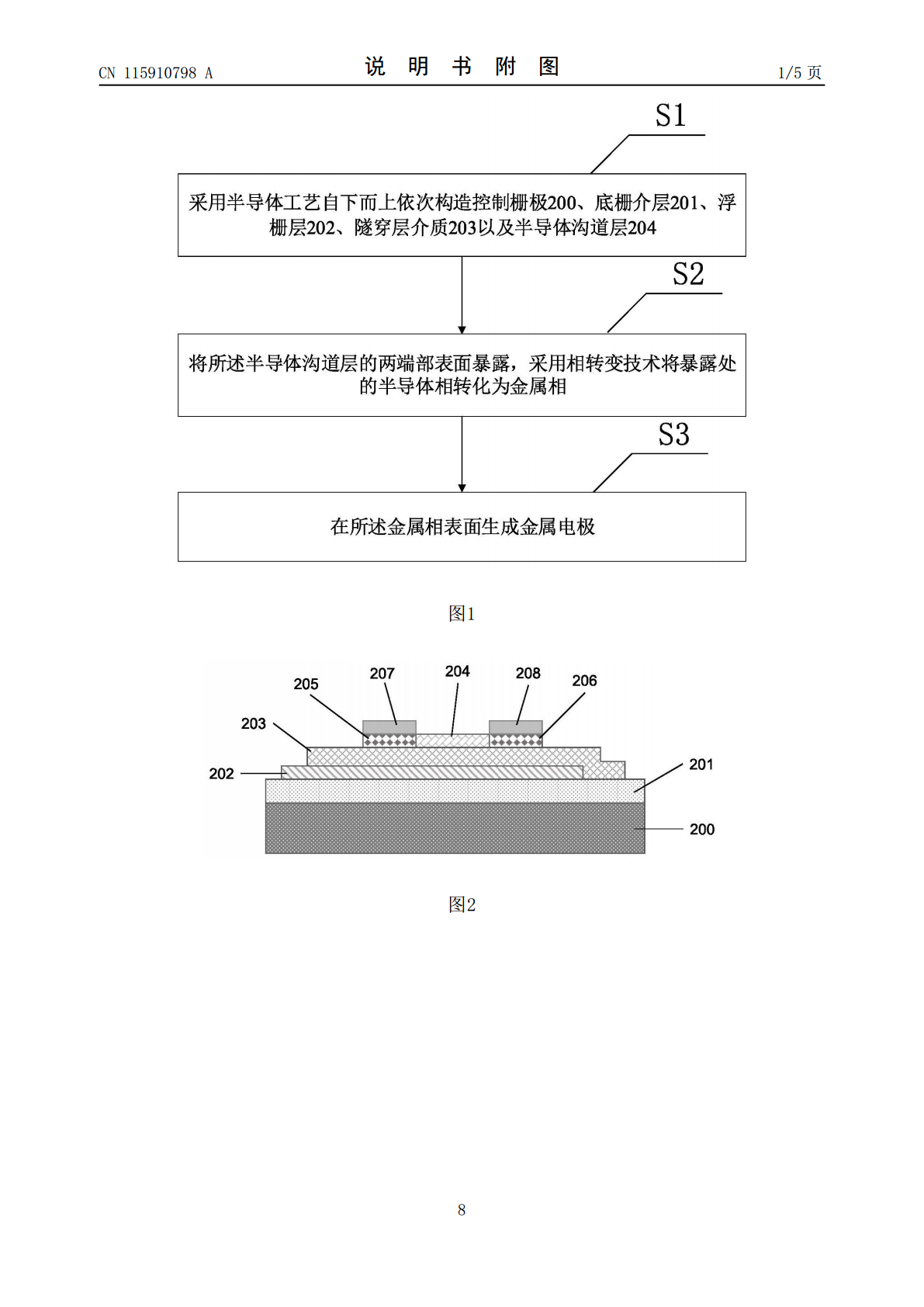

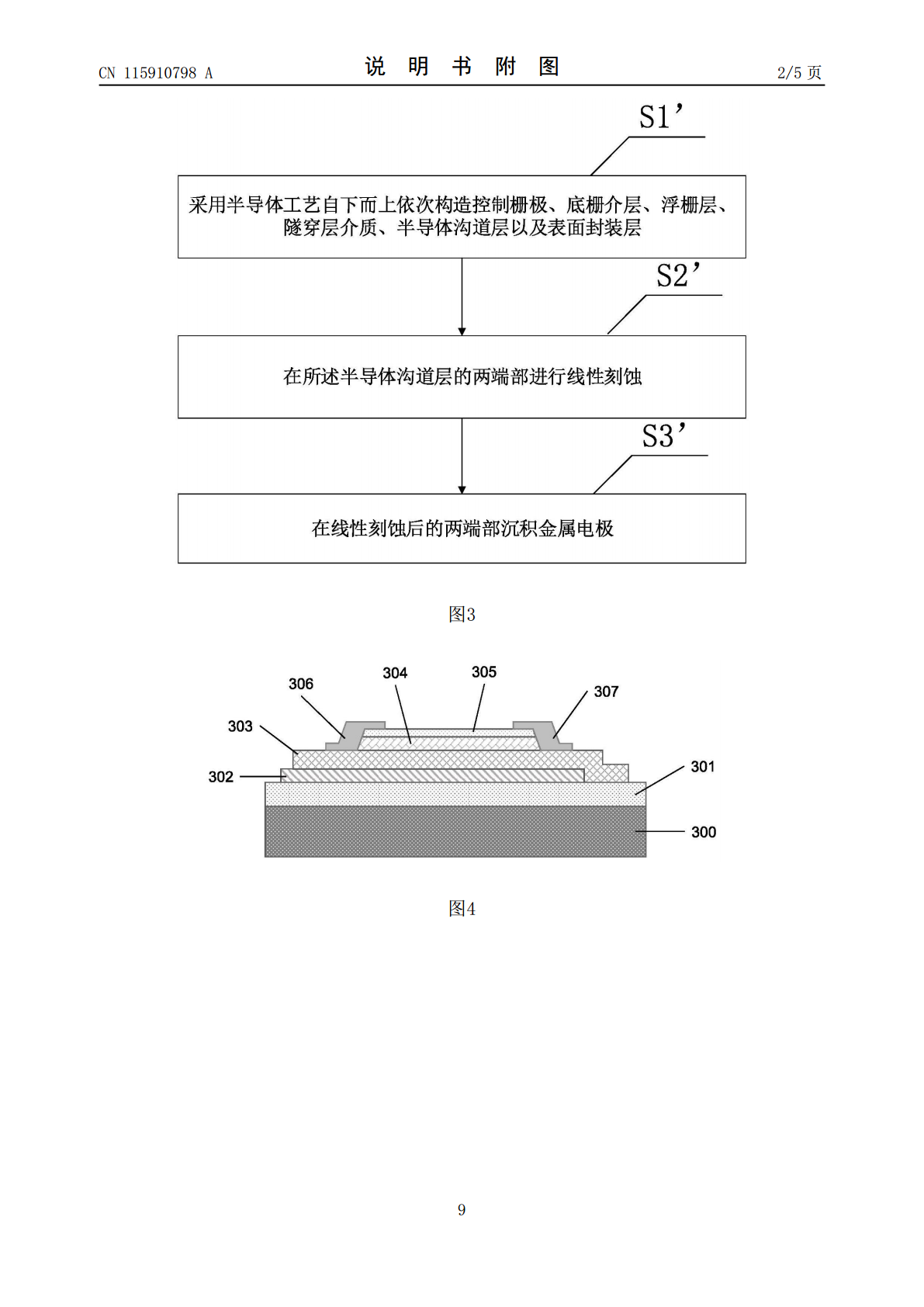

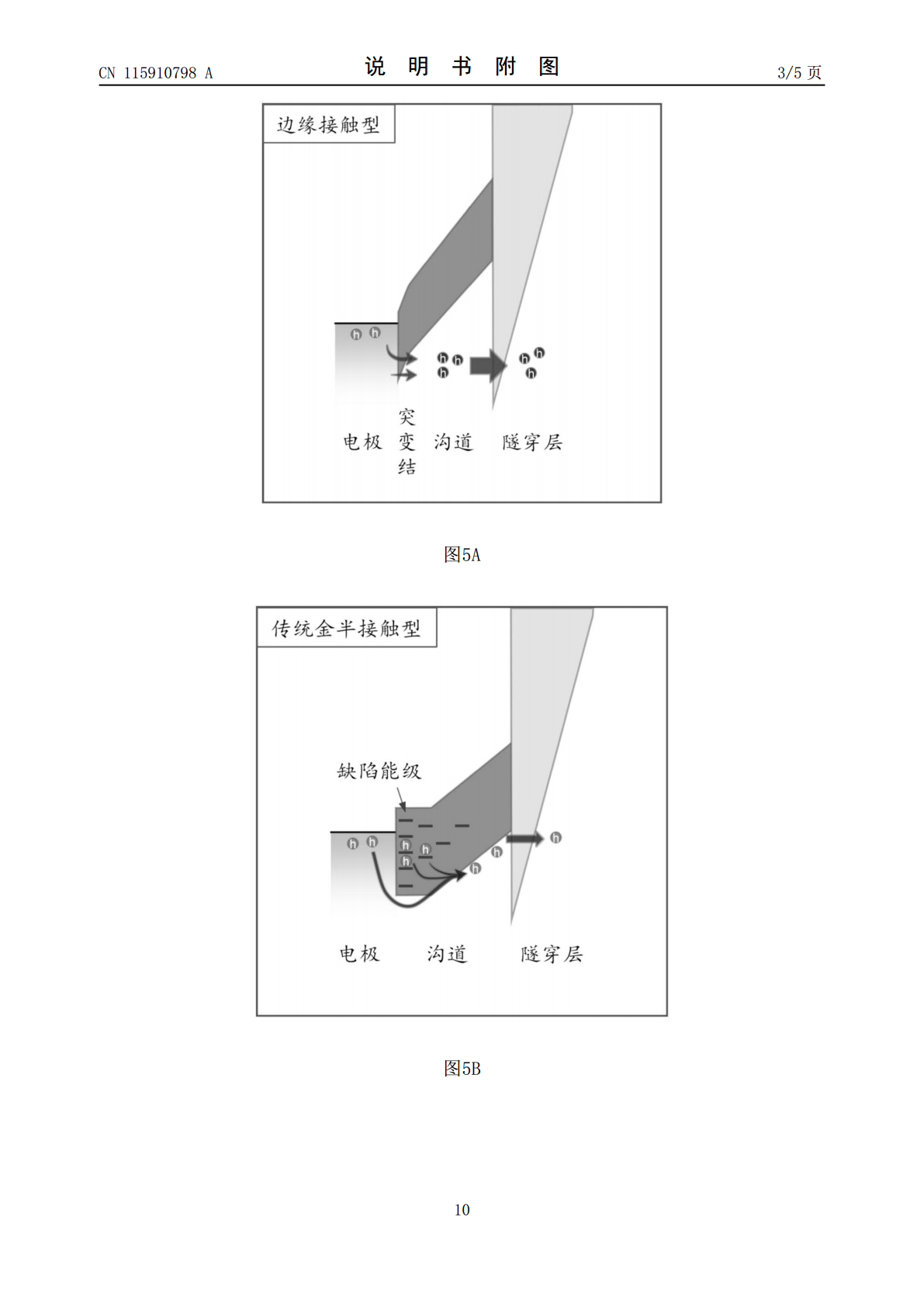

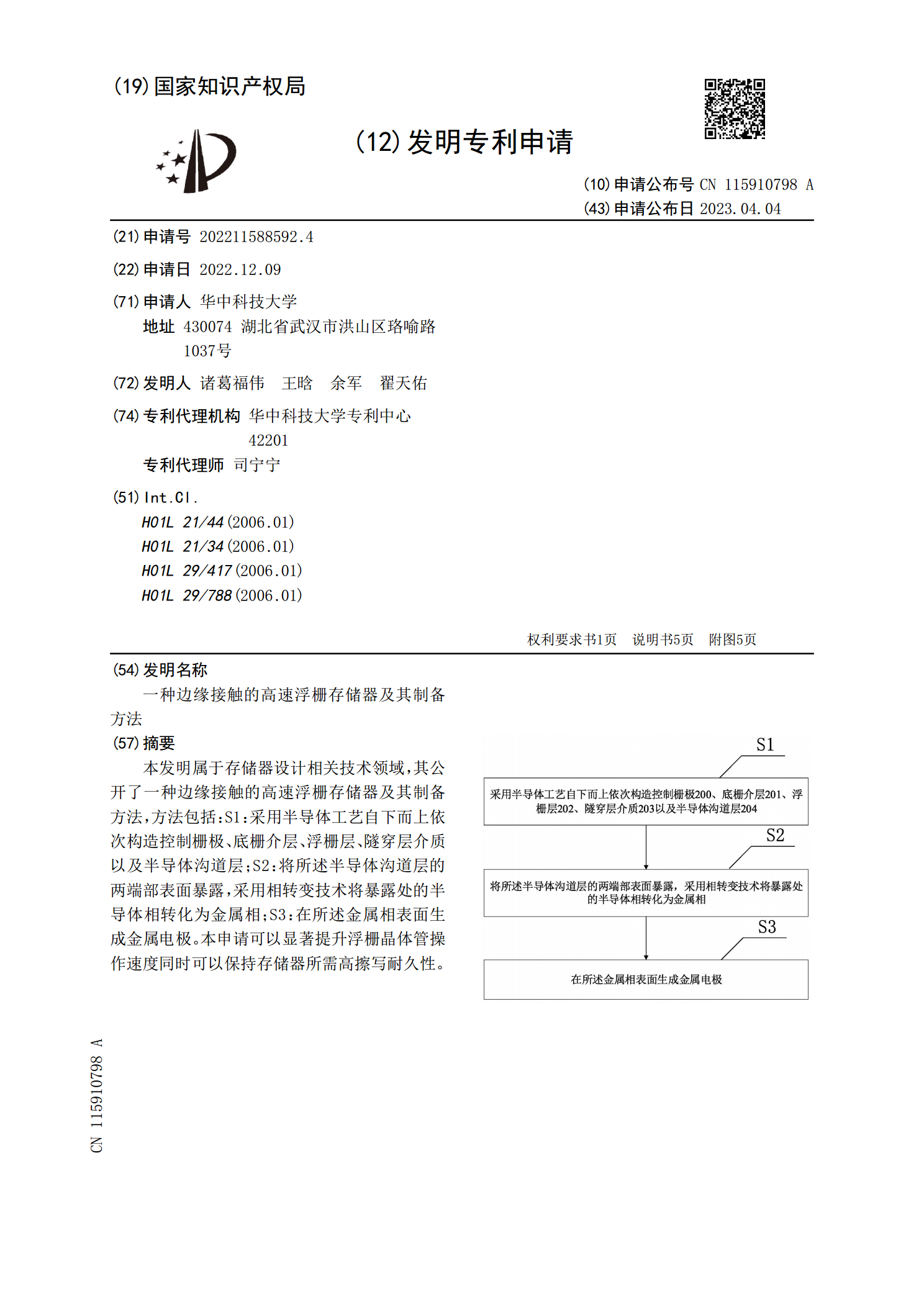

本发明属于存储器设计相关技术领域,其公开了一种边缘接触的高速浮栅存储器及其制备方法,方法包括:S1:采用半导体工艺自下而上依次构造控制栅极、底栅介层、浮栅层、隧穿层介质以及半导体沟道层;S2:将所述半导体沟道层的两端部表面暴露,采用相转变技术将暴露处的半导体相转化为金属相;S3:在所述金属相表面生成金属电极。本申请可以显著提升浮栅晶体管操作速度同时可以保持存储器所需高擦写耐久性。

一种浮栅及其制备方法.pdf

本发明公开了一种浮栅及其制备方法。所述制备方法包括:在衬底上依次形成衬垫氧化层和保护介质层,对所述保护介质层、所述衬垫氧化层和所述衬底进行图像化处理,形成有源区和浅沟槽隔离区,并对所述浅沟槽隔离区进行氧化层填充;剥离剩余保护介质层形成第一凹槽;在所述第一凹槽内壁上形成侧墙;去除剩余衬垫氧化层,以保留靠近所述侧墙的浅沟槽氧化层;依次去除所述侧墙和多余的浅沟槽氧化层,形成第二凹槽;在所述第二凹槽内露出的有源区上形成隧穿氧化层;在所述隧穿氧化层上形成栅极。本发明实施例提供的技术方案,在保证衬垫氧化层去除干净的前

一种浮栅的制备方法.pdf

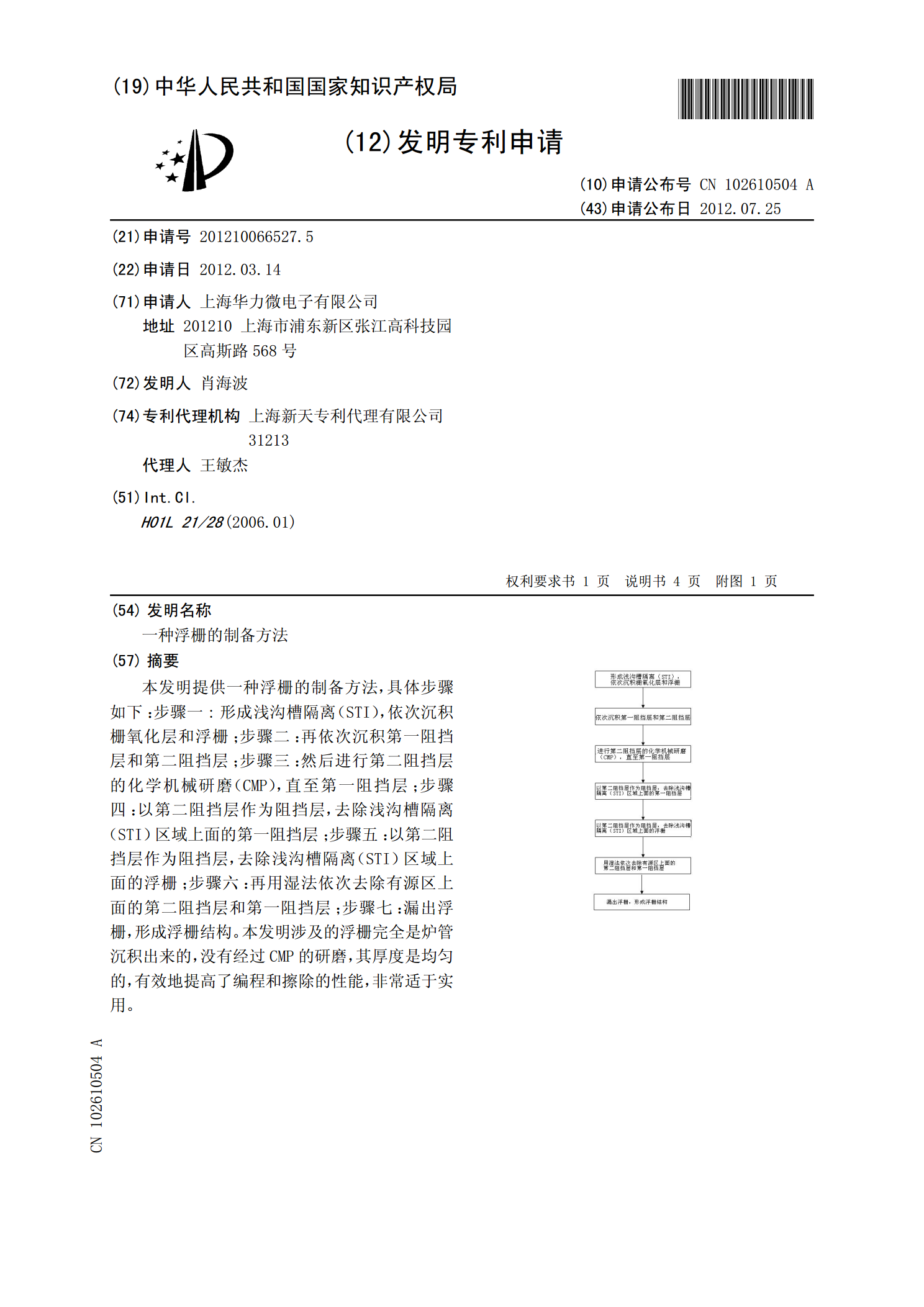

本发明提供一种浮栅的制备方法,具体步骤如下:步骤一:形成浅沟槽隔离(STI),依次沉积栅氧化层和浮栅;步骤二:再依次沉积第一阻挡层和第二阻挡层;步骤三:然后进行第二阻挡层的化学机械研磨(CMP),直至第一阻挡层;步骤四:以第二阻挡层作为阻挡层,去除浅沟槽隔离(STI)区域上面的第一阻挡层;步骤五:以第二阻挡层作为阻挡层,去除浅沟槽隔离(STI)区域上面的浮栅;步骤六:再用湿法依次去除有源区上面的第二阻挡层和第一阻挡层;步骤七:漏出浮栅,形成浮栅结构。本发明涉及的浮栅完全是炉管沉积出来的,没有经过CMP的研

一种浮栅控制型近红外波段双向记忆的光电存储器及其制备方法.pdf

本发明属于光电存储器领域,具体公开了一种浮栅控制型近红外波段双向记忆的光电存储器及其制备方法,光电存储器包括从下至上依次设置的衬底层、浮栅层、介质层、导电沟道层和金属电极,所述浮栅层材料为富勒烯,用于存储载流子;所述导电沟道层吸收近红外光和提供导电沟道;所述介质层为大带隙绝缘材料,所述介质层与所述浮栅层之间形成势垒,所述介质层(3)与所述导电沟道层(4)之间形成势垒。在所述衬底层(1)和所述源电极(5)之间施加正向的电压时,所述浮栅层(2)中注入电子;在所述衬底层(1)和所述源电极(5)之间施加负向的电压

分栅快闪存储器及其制备方法.pdf

本发明提供的一种分栅快闪存储器及其制备方法,该制备方法包括:提供一半导体衬底,半导体衬底包括相邻的存储区和逻辑区,存储区形成有字线栅极,逻辑区形成有多晶硅层,且暴露出了所述字线栅极的端点,字线栅极包括覆盖共享字线的氧化物层;刻蚀所述端点处的氧化物层;形成图形化的掩模层,图形化的掩模层在字线栅极的端点处暴露出部分长度的字线栅极,还覆盖了逻辑区用于形成逻辑栅极的区域;以图形化的掩模层为掩模,刻蚀多晶硅层,并去除剩余图形化的掩模层,以形成逻辑栅极。本发明通过刻蚀端点处的氧化物层,有利于减少在后续工艺中会在存储区