一种沟槽型半超结功率器件及其制作方法.pdf

白凡****12

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种沟槽型半超结功率器件及其制作方法.pdf

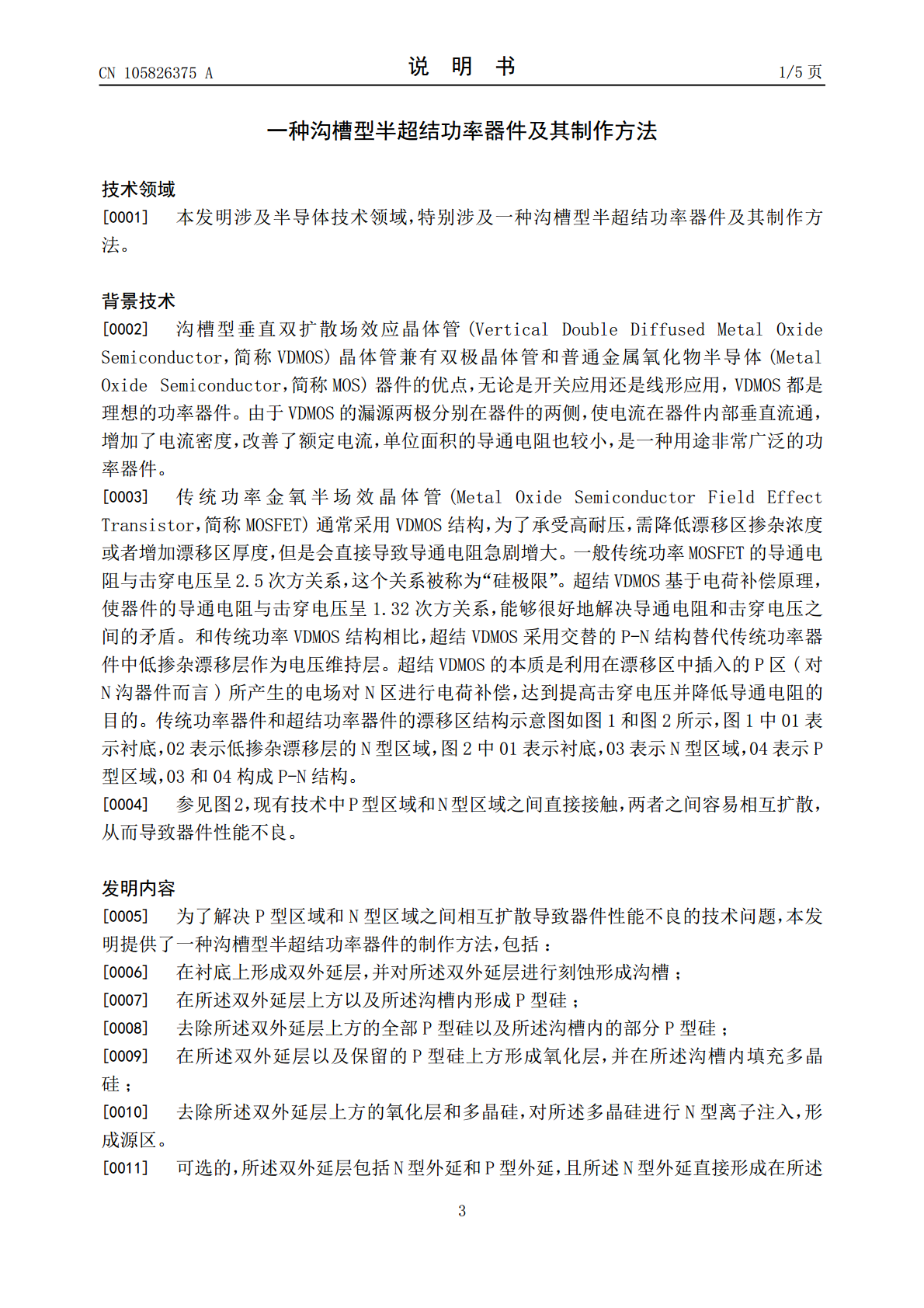

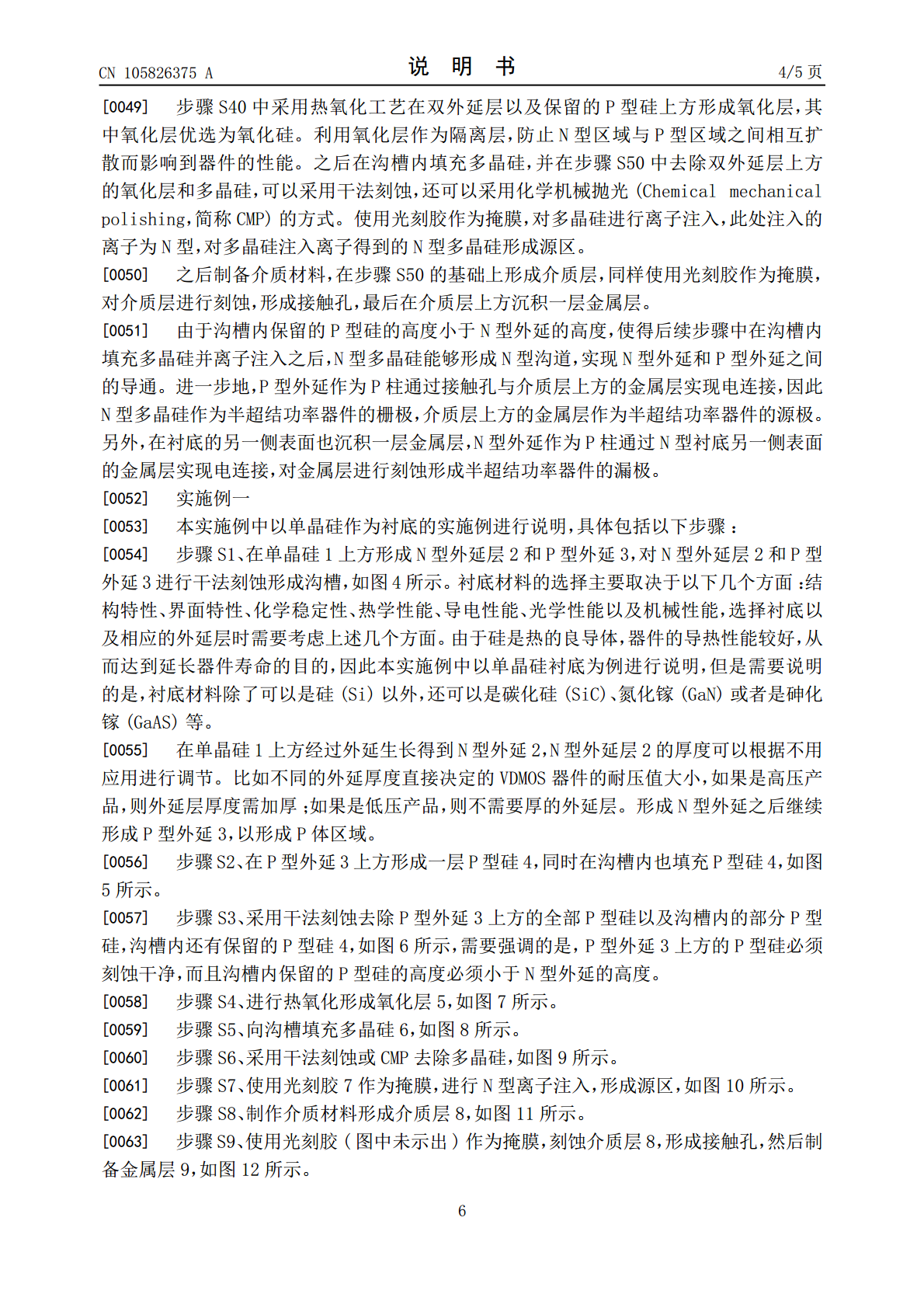

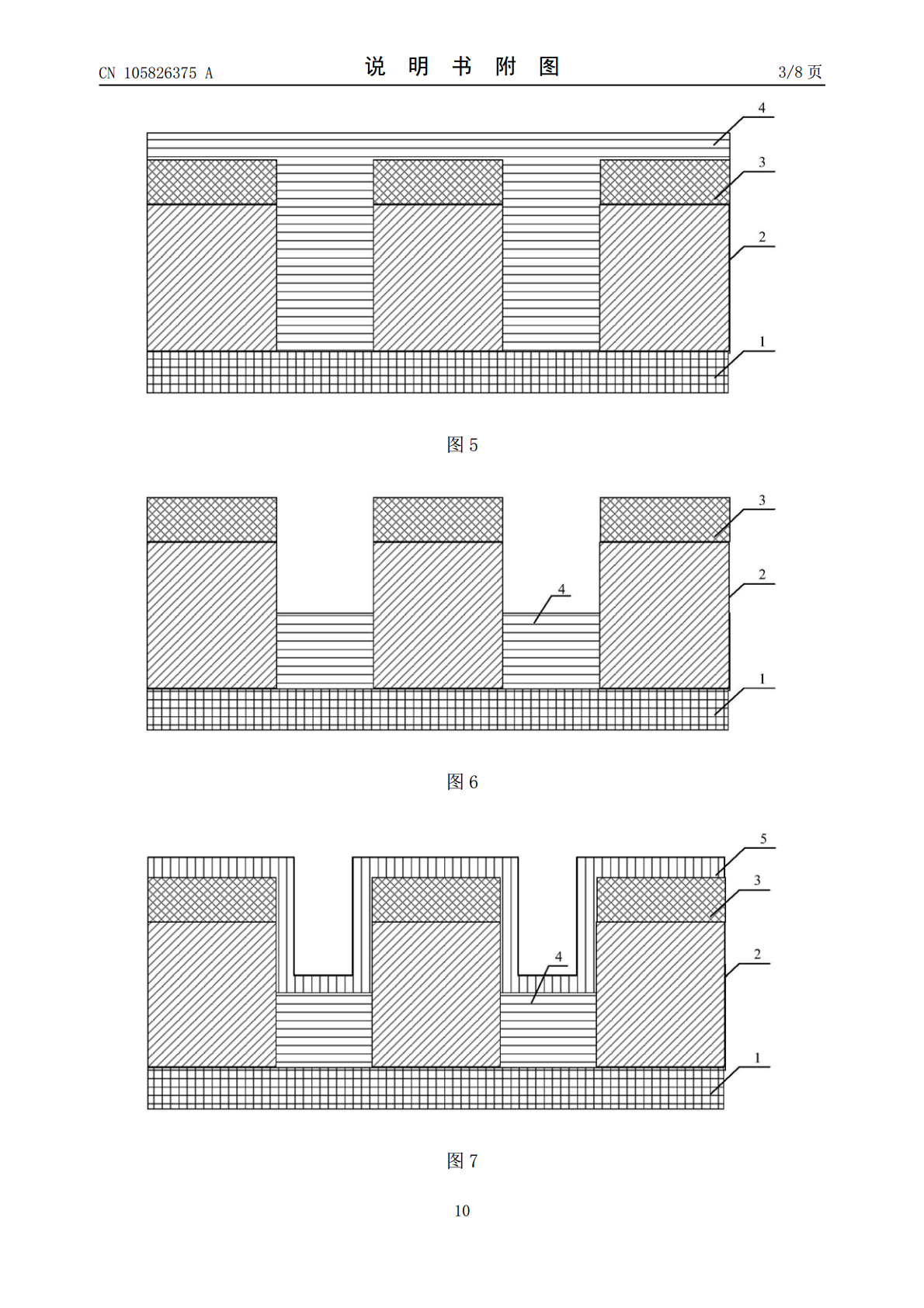

本发明公开了一种沟槽型半超结功率器件及其制作方法,其中制作方法包括:在衬底上形成双外延层,并进行刻蚀形成沟槽;在双外延层上方以及沟槽内形成P型硅;去除双外延层上方的全部P型硅以及沟槽内的部分P型硅;在双外延层以及沟槽内保留的P型硅上方形成氧化层,并在沟槽内填充多晶硅;去除双外延层上方的氧化层和多晶硅,对多晶硅进行N型离子注入,形成源区。采用双层外延片,一次沟槽刻蚀在沟槽下部形成P柱区域,利用氧化层作为隔离,在沟槽上部填充多晶硅形成沟道,工艺简单,降低了器件制造成本。双外延层以及保留的P型硅上方形成的氧化层

一种超结功率器件及其制作方法.pdf

本发明公开了一种超结功率器件及其制作方法,其中制作方法包括:在衬底上形成外延层,并对所述外延层进行刻蚀形成沟槽;在所述外延层上方及所述沟槽内形成氧化层和多晶硅;在所述沟槽内填充介质材料形成介质层,去除所述外延层上方的氧化层、多晶硅以及沟槽内的介质层,保留所述沟槽内的氧化层、多晶硅和介质层,使得沟槽内保留的介质层与氧化层和多晶硅高度相同。采用对外延层进行刻蚀形成沟槽的方式,并在沟槽内形成氧化层和多晶硅,然后在沟槽中填充介质材料,形成P型区域,与现有制作方法相比,本发明不需要重复进行外延生长工艺来制作外延层,

一种沟槽型功率器件结构及其制作方法.pdf

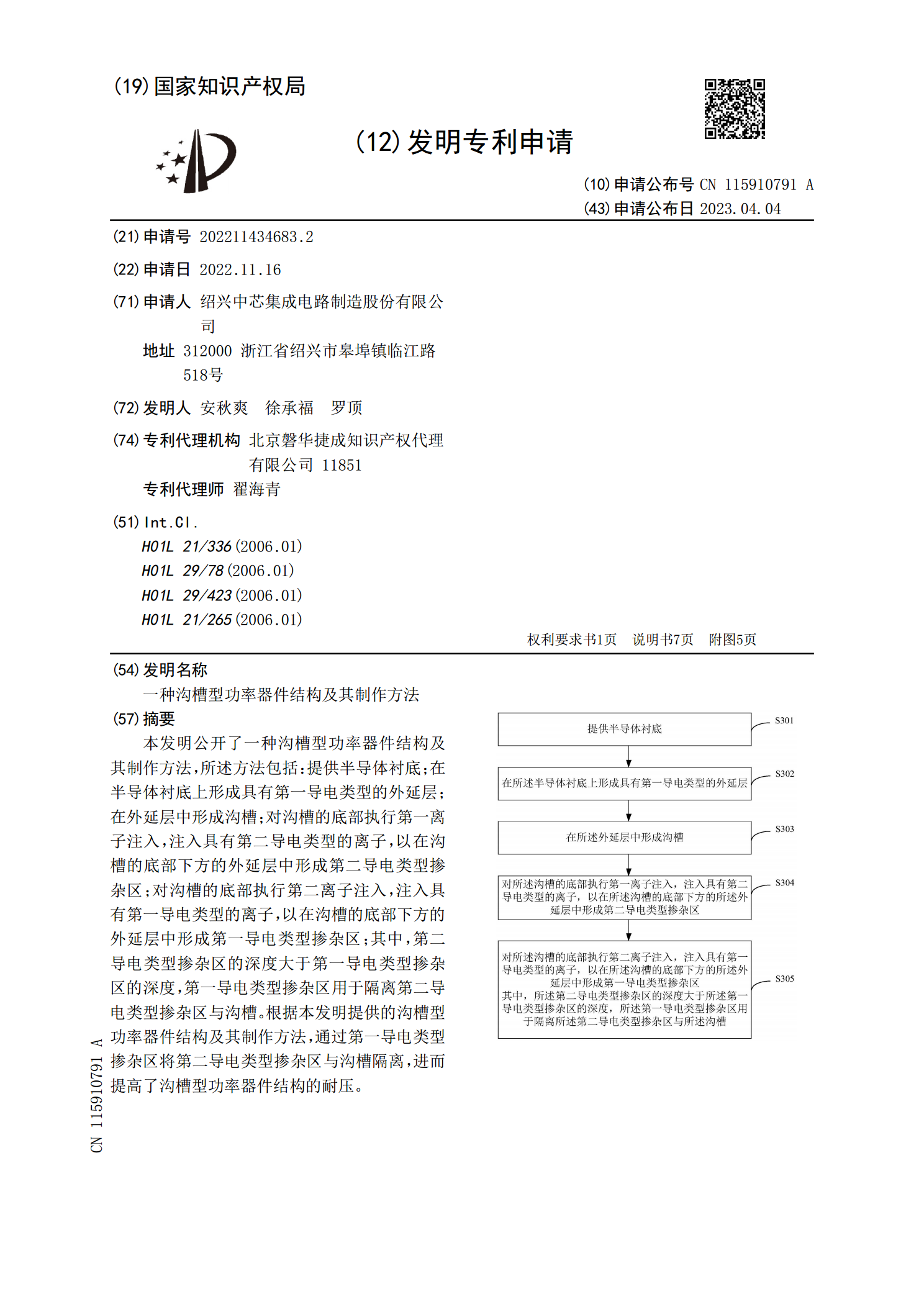

本发明公开了一种沟槽型功率器件结构及其制作方法,所述方法包括:提供半导体衬底;在半导体衬底上形成具有第一导电类型的外延层;在外延层中形成沟槽;对沟槽的底部执行第一离子注入,注入具有第二导电类型的离子,以在沟槽的底部下方的外延层中形成第二导电类型掺杂区;对沟槽的底部执行第二离子注入,注入具有第一导电类型的离子,以在沟槽的底部下方的外延层中形成第一导电类型掺杂区;其中,第二导电类型掺杂区的深度大于第一导电类型掺杂区的深度,第一导电类型掺杂区用于隔离第二导电类型掺杂区与沟槽。根据本发明提供的沟槽型功率器件结构及

沟槽型功率器件及其制造方法.pdf

本申请公开了沟槽型功率器件及其制造方法。所述沟槽型功率器件包括:半导体衬底;位于所述半导体衬底上的漂移区;位于所述漂移区中的第一沟槽和第二沟槽;位于所述第一沟槽中的栅叠层;以及位于所述第二沟槽侧壁上的肖特基金属,其中,所述肖特基金属与所述漂移区形成肖特基势垒二极管。该沟槽型功率器件采用双沟槽结构,将沟槽型MOSFET和肖特基势垒二极管相结合且将肖特基金属形成在沟槽侧壁上,不仅可以提高功率器件的性能,而且可以减小功率器件的单元面积。

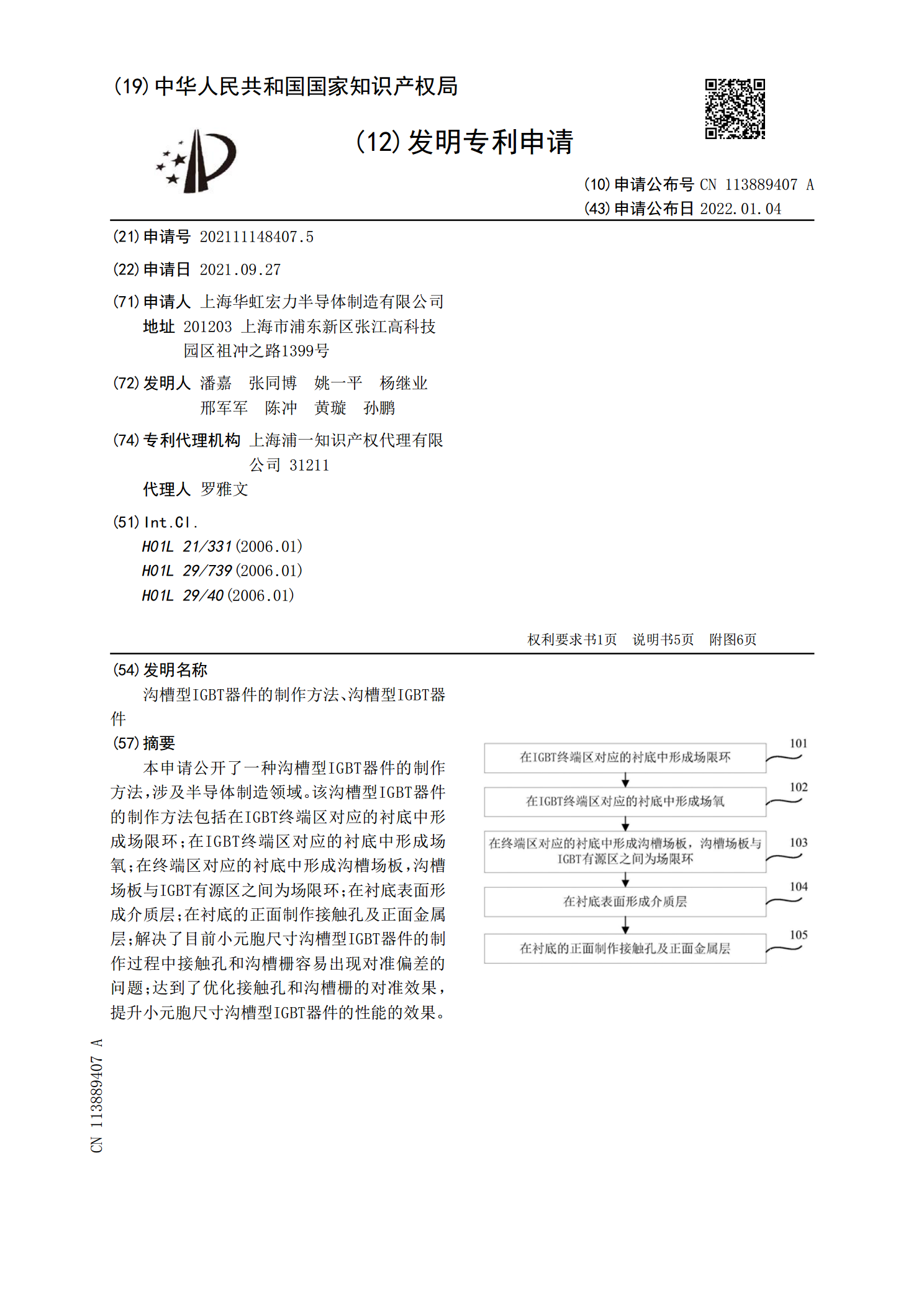

沟槽型IGBT器件的制作方法、沟槽型IGBT器件.pdf

本申请公开了一种沟槽型IGBT器件的制作方法,涉及半导体制造领域。该沟槽型IGBT器件的制作方法包括在IGBT终端区对应的衬底中形成场限环;在IGBT终端区对应的衬底中形成场氧;在终端区对应的衬底中形成沟槽场板,沟槽场板与IGBT有源区之间为场限环;在衬底表面形成介质层;在衬底的正面制作接触孔及正面金属层;解决了目前小元胞尺寸沟槽型IGBT器件的制作过程中接触孔和沟槽栅容易出现对准偏差的问题;达到了优化接触孔和沟槽栅的对准效果,提升小元胞尺寸沟槽型IGBT器件的性能的效果。