一种半导体器件及其制备方法、电子装置.pdf

涵蓄****09

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种半导体器件及其制备方法、电子装置.pdf

本发明涉及一种半导体器件及其制备方法、电子装置。所述方法包括步骤S1:选用NMP对半导体器件进行清洗,以去除所述半导体器件在蚀刻过程中形成的残留物;步骤S2:选用含有O

一种半导体器件及其制备方法、电子装置.pdf

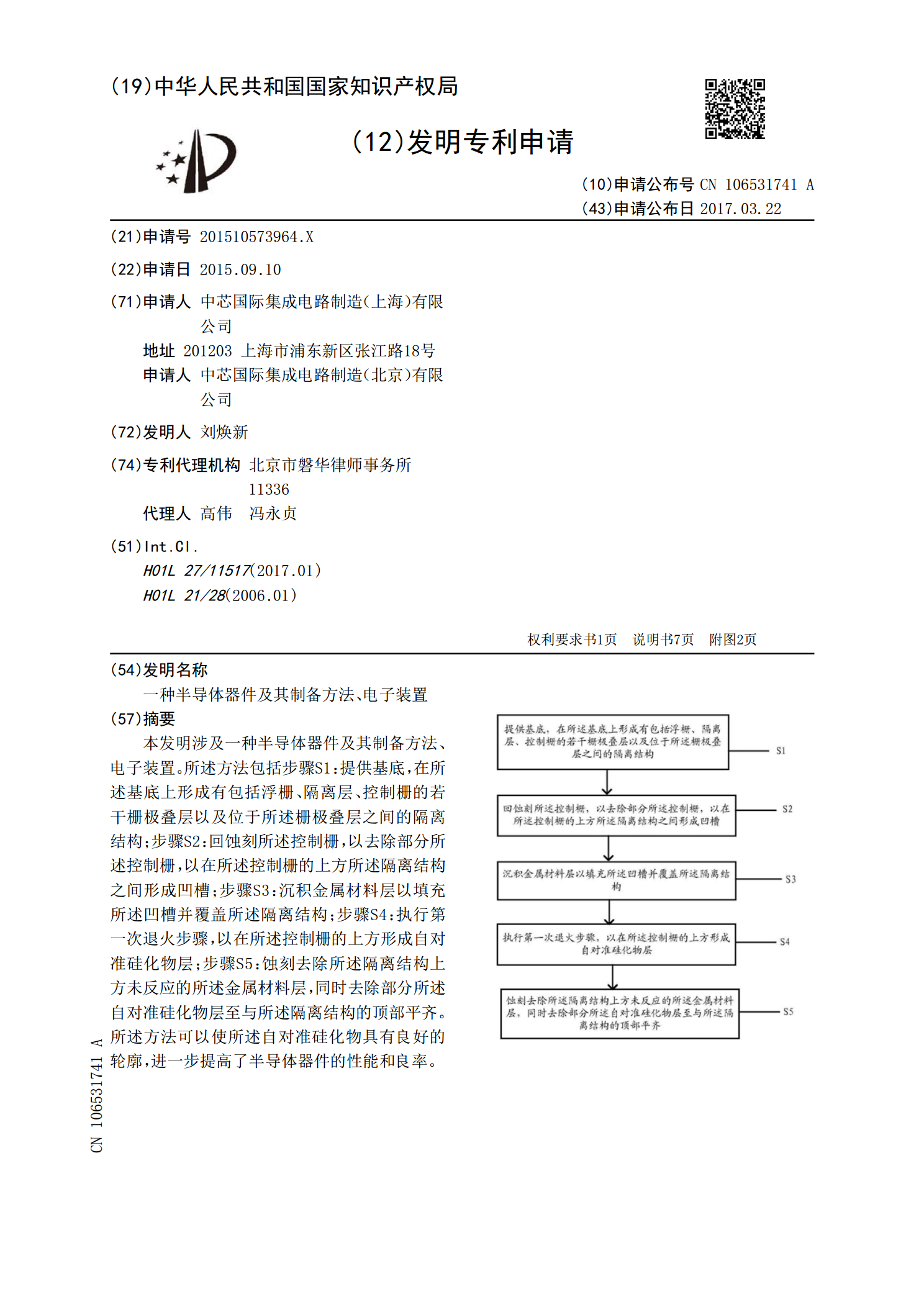

本发明涉及一种半导体器件及其制备方法、电子装置。所述方法包括步骤S1:提供基底,在所述基底上形成有包括浮栅、隔离层、控制栅的若干栅极叠层以及位于所述栅极叠层之间的隔离结构;步骤S2:回蚀刻所述控制栅,以去除部分所述控制栅,以在所述控制栅的上方所述隔离结构之间形成凹槽;步骤S3:沉积金属材料层以填充所述凹槽并覆盖所述隔离结构;步骤S4:执行第一次退火步骤,以在所述控制栅的上方形成自对准硅化物层;步骤S5:蚀刻去除所述隔离结构上方未反应的所述金属材料层,同时去除部分所述自对准硅化物层至与所述隔离结构的顶部平齐

一种半导体器件及其制备方法、电子装置.pdf

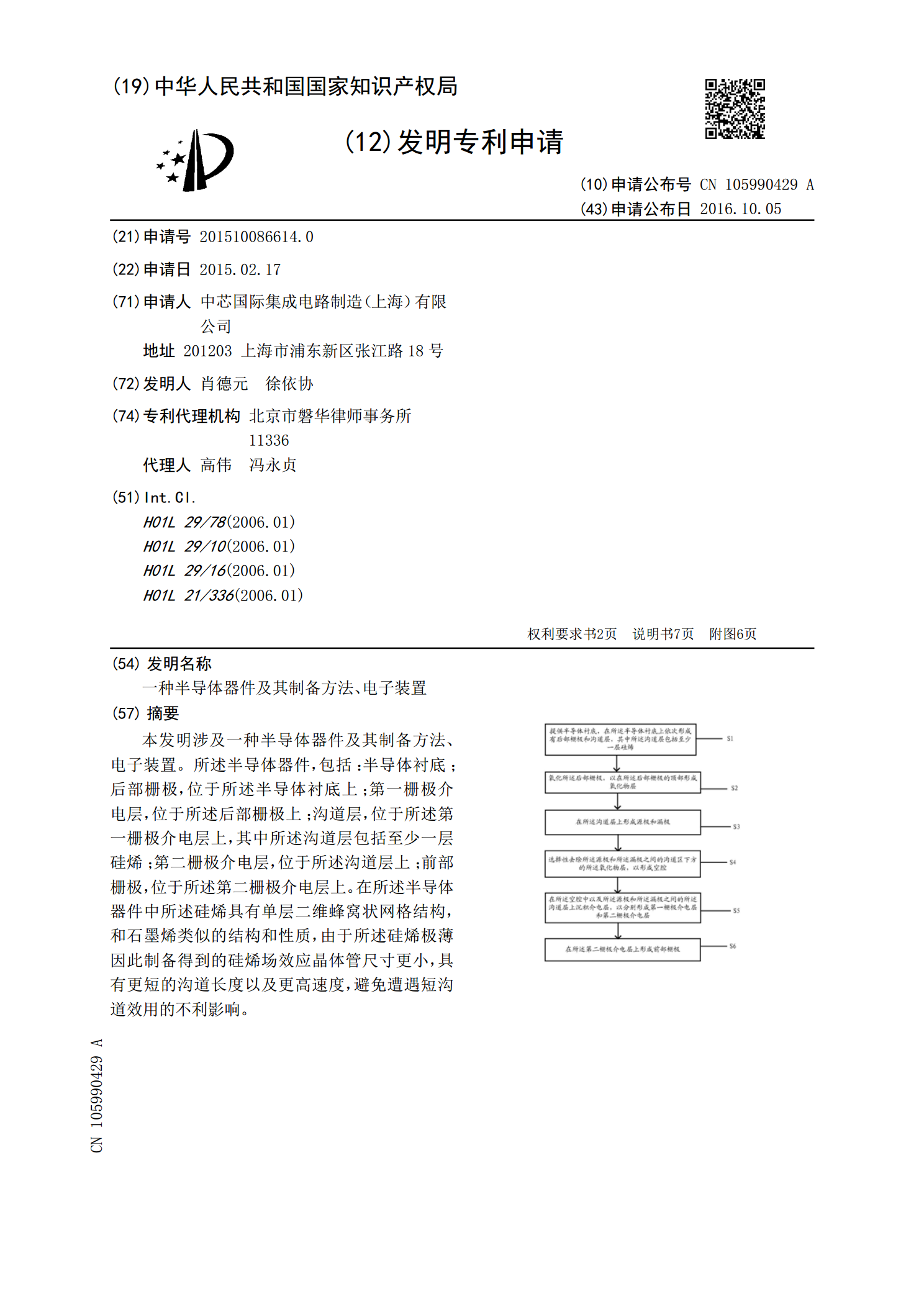

本发明涉及一种半导体器件及其制备方法、电子装置。所述半导体器件,包括:半导体衬底;后部栅极,位于所述半导体衬底上;第一栅极介电层,位于所述后部栅极上;沟道层,位于所述第一栅极介电层上,其中所述沟道层包括至少一层硅烯;第二栅极介电层,位于所述沟道层上;前部栅极,位于所述第二栅极介电层上。在所述半导体器件中所述硅烯具有单层二维蜂窝状网格结构,和石墨烯类似的结构和性质,由于所述硅烯极薄因此制备得到的硅烯场效应晶体管尺寸更小,具有更短的沟道长度以及更高速度,避免遭遇短沟道效用的不利影响。

一种半导体器件及其制备方法、电子装置.pdf

本发明涉及一种半导体器件及其制备方法、电子装置。所述方法包括提供半导体衬底,所述半导体衬底上形成有介电层,所述介电层中形成有接触孔;形成填充所述接触孔的导电材料;执行氧化步骤,以氧化在形成所述导电材料的过程中所述介电层表面残留的导电材料颗粒和/或副产物,形成容易去除的氧化物,其中,所述氧化步骤选用氧化剂和催化剂对所述介电层表面残留的导电材料颗粒和/或副产物进行氧化,同时添加抑制剂,以防止所述接触孔开口中的所述导电材料的氧化;对形成的所述容易去除的氧化物进行平坦化并清洗,以去除所述容易去除的氧化物。通过所述

一种半导体器件及其制备方法、电子装置.pdf

本发明涉及一种半导体器件及其制备方法、电子装置。所述方法包括步骤S1:提供半导体衬底,在所述半导体衬底上形成有若干鳍片以及环绕所述鳍片的虚拟栅极氧化物层和虚拟栅极,在所述半导体衬底上还形成有填充相邻所述虚拟栅极之间间隙的层间介电层;步骤S2:去除所述虚拟栅极,以露出所述虚拟栅极氧化物层;步骤S3:选用SiCoNi的方法去除所述虚拟栅极氧化物层,以露出所述鳍片;步骤S4:选用氮和氢等离子体去除所述鳍片表面上残留的含F副产物。通过所述方法不仅可以完全去除所述虚拟栅极氧化物层,降低对接触孔蚀刻停止层和层间介电层