一种功率器件栅极侧墙制备方法.pdf

冷霜****魔王

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种功率器件栅极侧墙制备方法.pdf

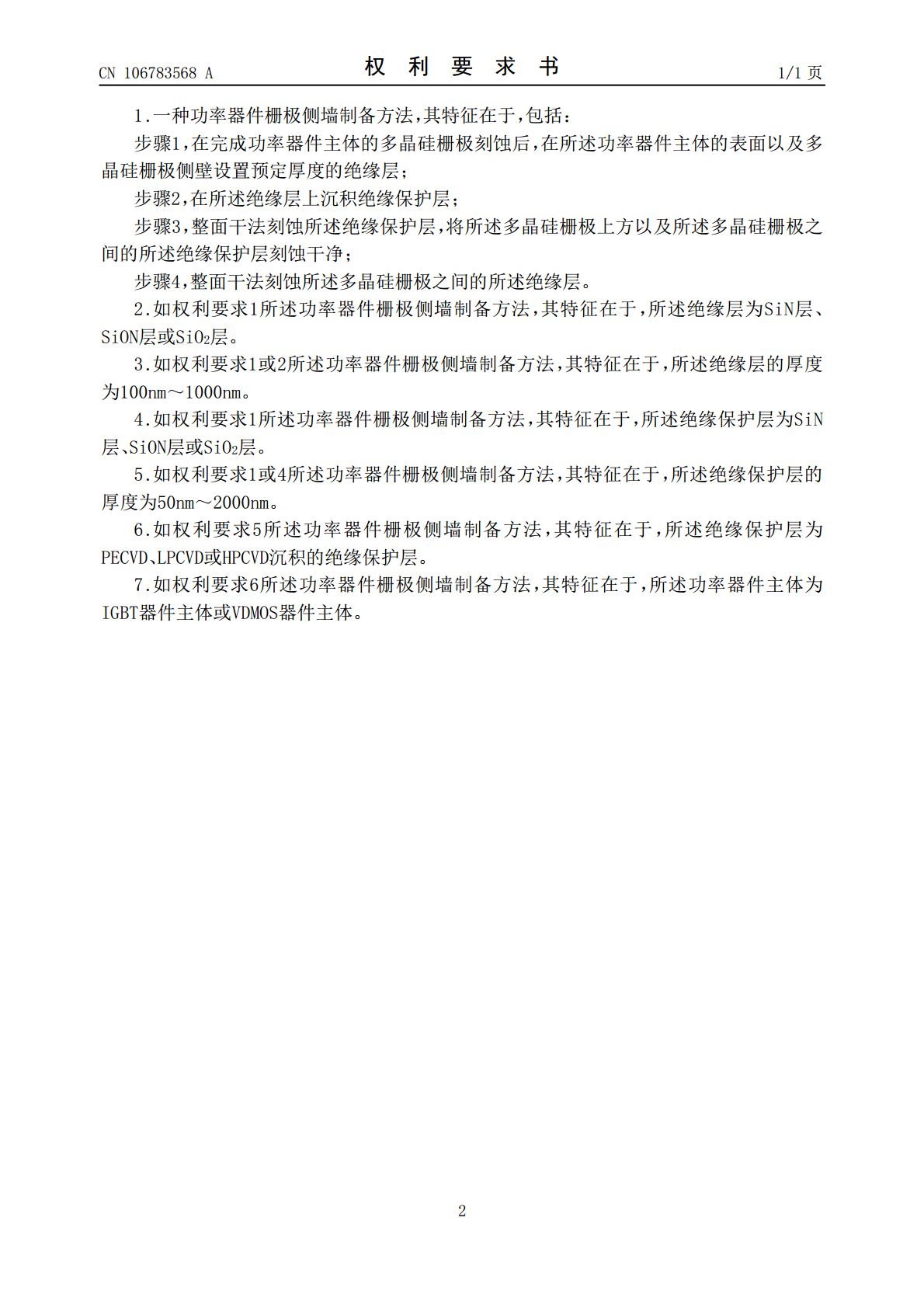

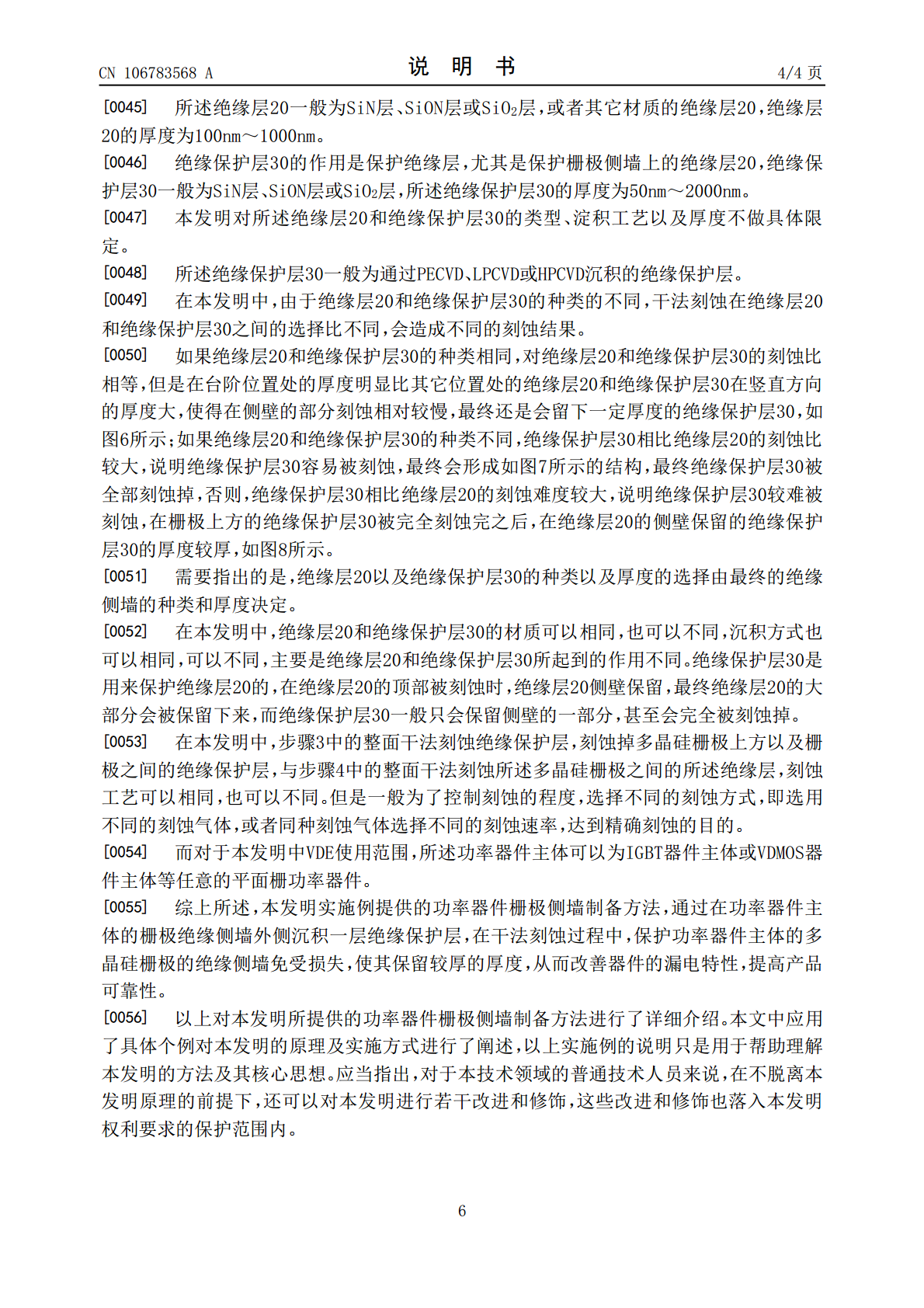

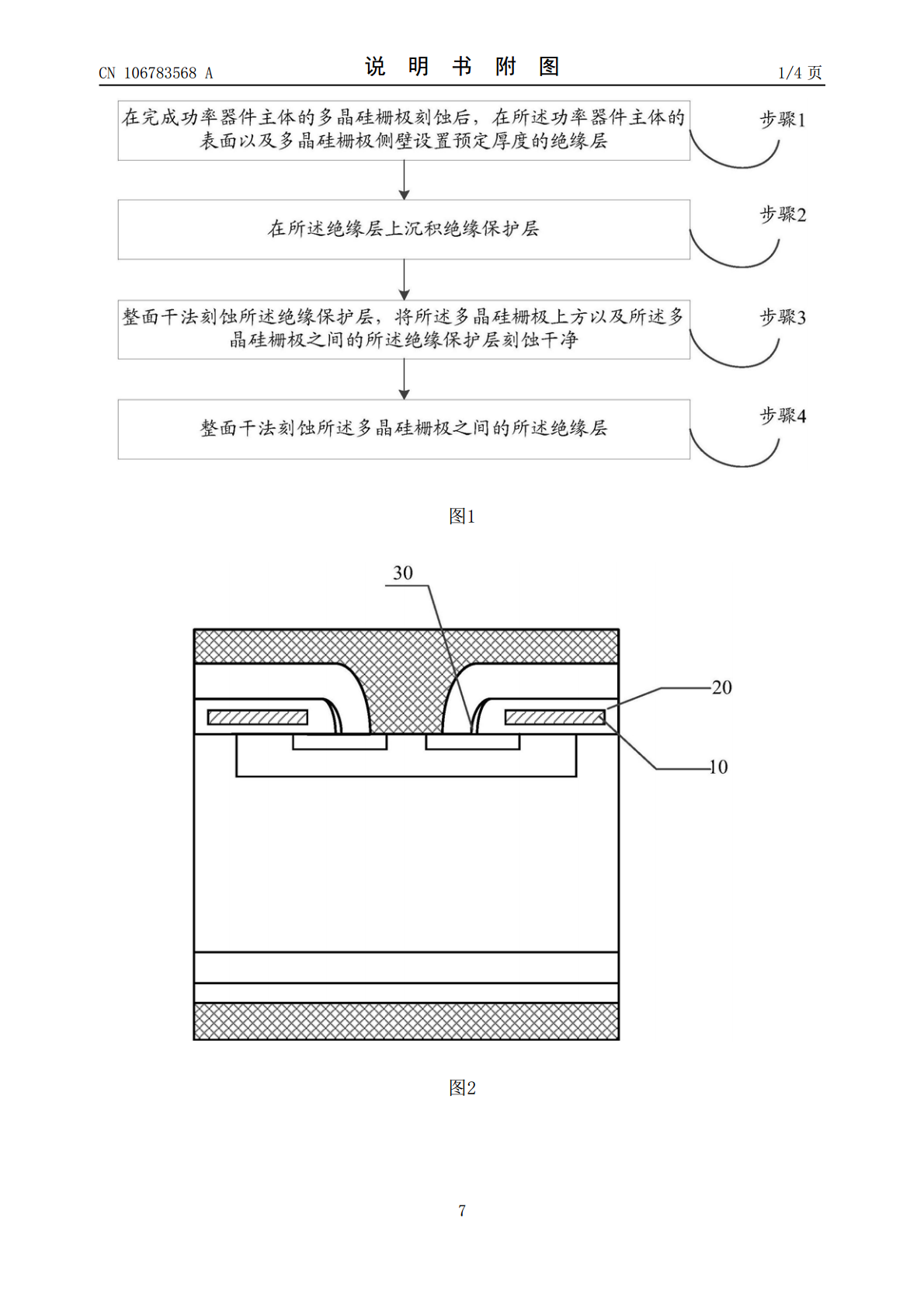

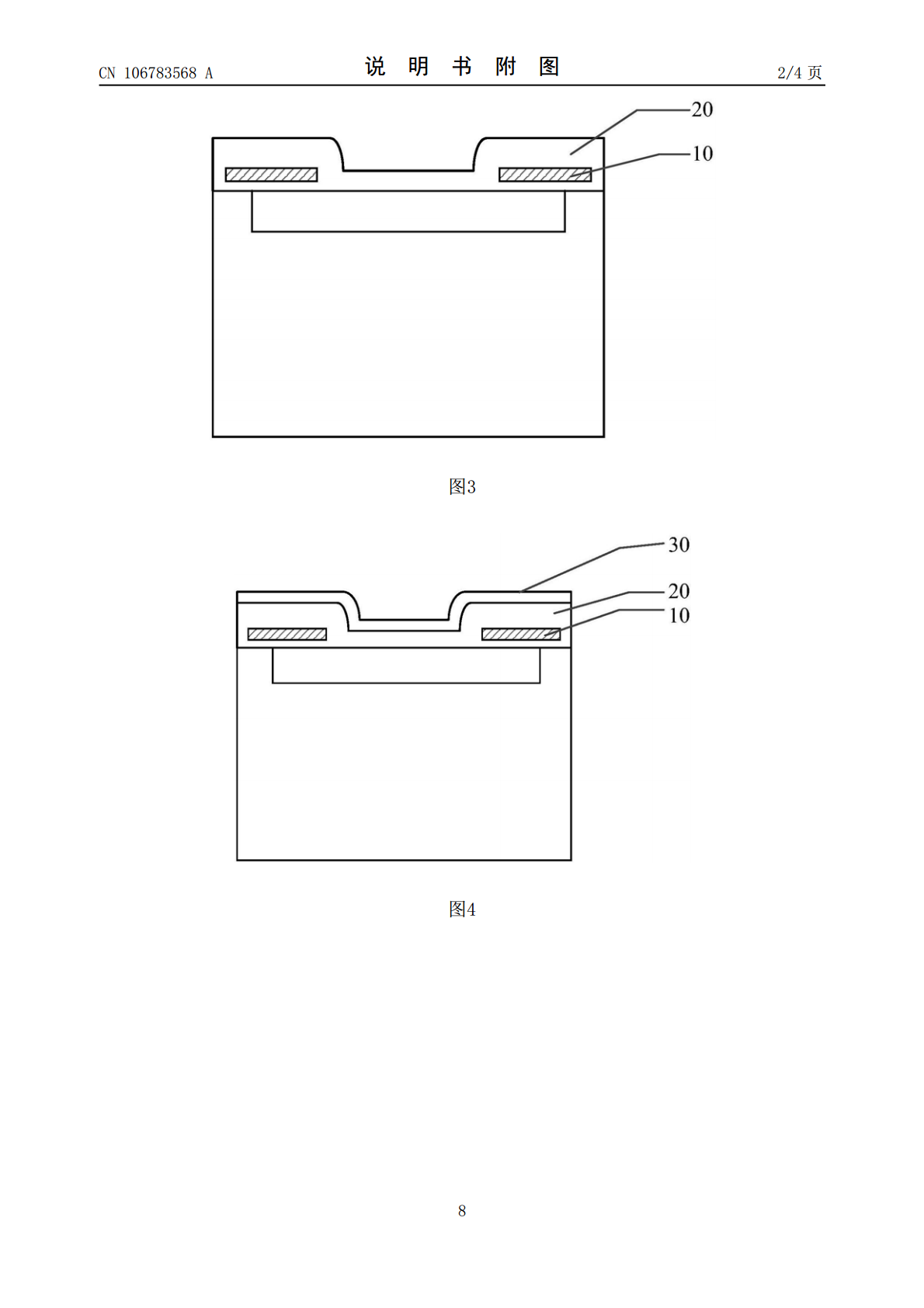

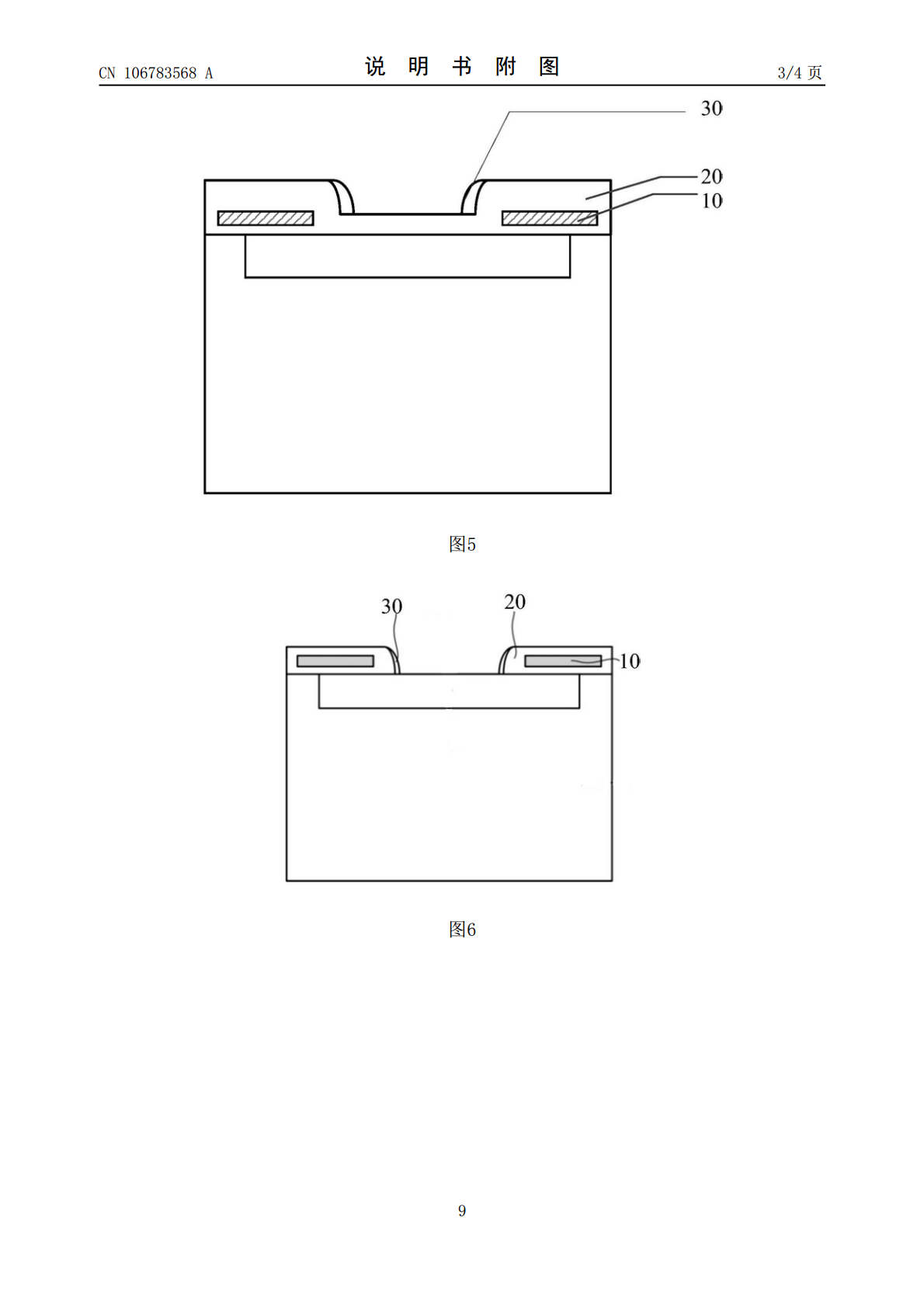

本发明公开了一种功率器件栅极侧墙制备方法,包括:步骤1,在完成功率器件主体的多晶硅栅极刻蚀后,在所述功率器件主体的表面以及多晶硅栅极侧壁设置预定厚度的绝缘层;步骤2,在所述绝缘层上沉积绝缘保护层;步骤3,整面干法刻蚀所述绝缘保护层,将所述多晶硅栅极上方以及所述多晶硅栅极之间的所述绝缘保护层刻蚀干净;步骤4,整面干法刻蚀所述多晶硅栅极之间的所述绝缘层。通过在功率器件主体的栅极绝缘侧墙外侧沉积一层绝缘保护层,在干法刻蚀过程中,保护功率器件主体的多晶硅栅极的绝缘侧墙免受损失,使其保留较厚的厚度,从而改善器件的漏

栅极侧墙的制造方法.pdf

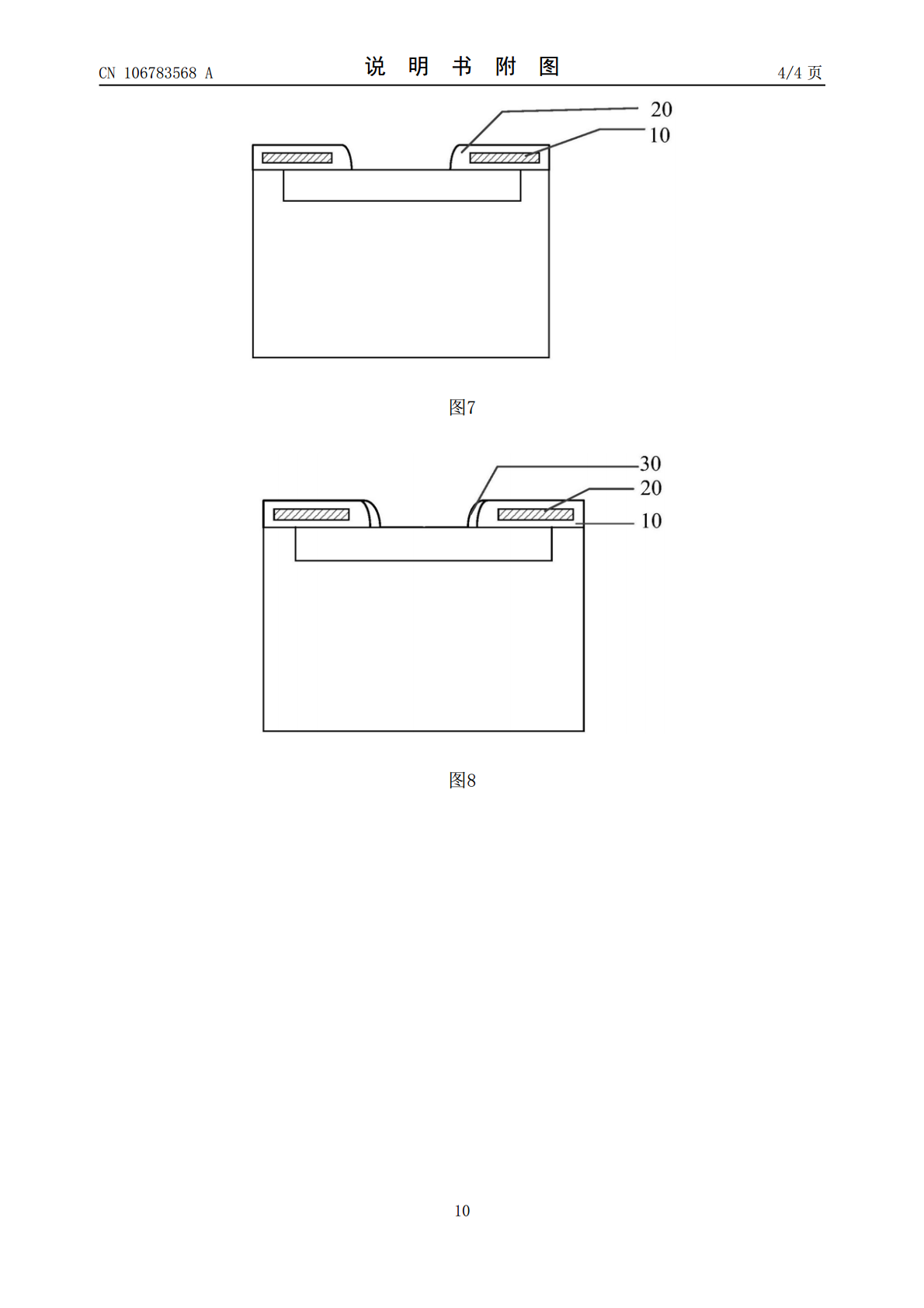

本发明公开了一种栅极侧墙的制造方法,包括步骤:步骤一、在半导体衬底表面形成由栅介质层、多晶硅栅和硬质掩膜层叠加而成的栅极结构;步骤二、形成侧墙介质层;步骤三、在侧墙介质层的表面形成侧墙保护介质层;步骤四、对侧墙保护介质层进行第一次全面刻蚀并使侧墙保护介质层仅位于栅极结构侧面;步骤五、对侧墙介质层进行第二次全面刻蚀形成侧墙,所保留的侧墙保护介质层对侧墙的侧面进行保护,侧墙保护介质层和硬质掩膜层自对准暴露出侧墙的顶部表面从而能调节侧墙的高度;步骤六、去除所保留的侧墙保护介质层。本发明能防止侧墙的厚度减薄,使侧

改善栅极侧墙形貌的方法及半导体器件制造方法.pdf

本发明提供一种改善栅极侧墙形貌的方法以及半导体器件制造方法,在形成的侧墙层表面上覆盖一层保护层,该保护层包裹住侧墙层,这样使半导体衬底表面趋于平坦;然后,采用侧墙层和保护层具有高刻蚀选择比的穿通刻蚀工艺垂直刻蚀保护层,以去除保护层位于栅极结构顶部等平面上的部分,而保留位于所述栅极结构的侧壁及斜肩上的部分;之后在部分刻蚀侧墙层形成侧墙的过程中,斜肩上的保护层可以对其下的侧墙层进行保护,降低斜肩处侧墙材料的刻蚀损耗,从而可以最终获得宽度均匀性的侧墙,该侧墙可以增大后续在源/漏区上形成的接触孔与栅极结构之间的有

一种栅极侧墙的制作方法.pdf

一种栅极侧墙的制作方法,包括:在腔室内通入2Nte前驱体;通过抽气,仅保留一个原子层厚度前驱体在晶圆的表面;通入氮源工艺气体,在等离子体的作用下与2Nte发应,生成氮化硅薄膜;对残余气体后清理;在腔室内通入2Nte前驱体;通过抽气,仅保留一个原子层厚度前驱体在晶圆的表面;通入氧气,在等离子体的作用下与2Nte发应,生成氧化硅薄膜;对残余气体后清理,完成栅极侧墙制作。通过本发明获得的栅极侧墙与栅极之间具有氮化硅薄膜,进而有效避免在ALD工艺中等离子体增强的氧气直接与栅极表面接触,对栅极进行氧化,导致栅极尺寸

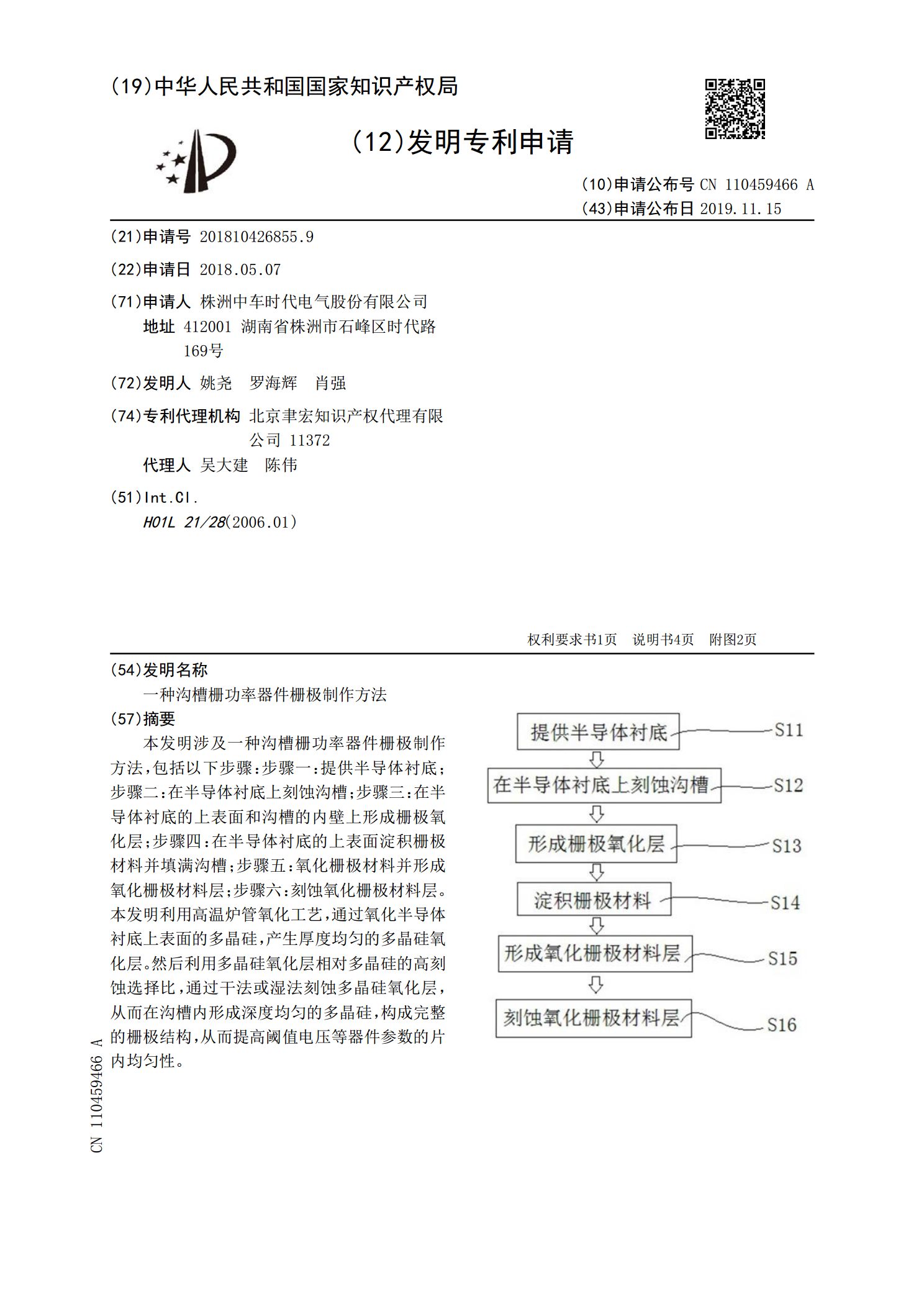

一种沟槽栅功率器件栅极制作方法.pdf

本发明涉及一种沟槽栅功率器件栅极制作方法,包括以下步骤:步骤一:提供半导体衬底;步骤二:在半导体衬底上刻蚀沟槽;步骤三:在半导体衬底的上表面和沟槽的内壁上形成栅极氧化层;步骤四:在半导体衬底的上表面淀积栅极材料并填满沟槽;步骤五:氧化栅极材料并形成氧化栅极材料层;步骤六:刻蚀氧化栅极材料层。本发明利用高温炉管氧化工艺,通过氧化半导体衬底上表面的多晶硅,产生厚度均匀的多晶硅氧化层。然后利用多晶硅氧化层相对多晶硅的高刻蚀选择比,通过干法或湿法刻蚀多晶硅氧化层,从而在沟槽内形成深度均匀的多晶硅,构成完整的栅极结