一种沟槽栅功率器件栅极制作方法.pdf

飞飙****ng

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种沟槽栅功率器件栅极制作方法.pdf

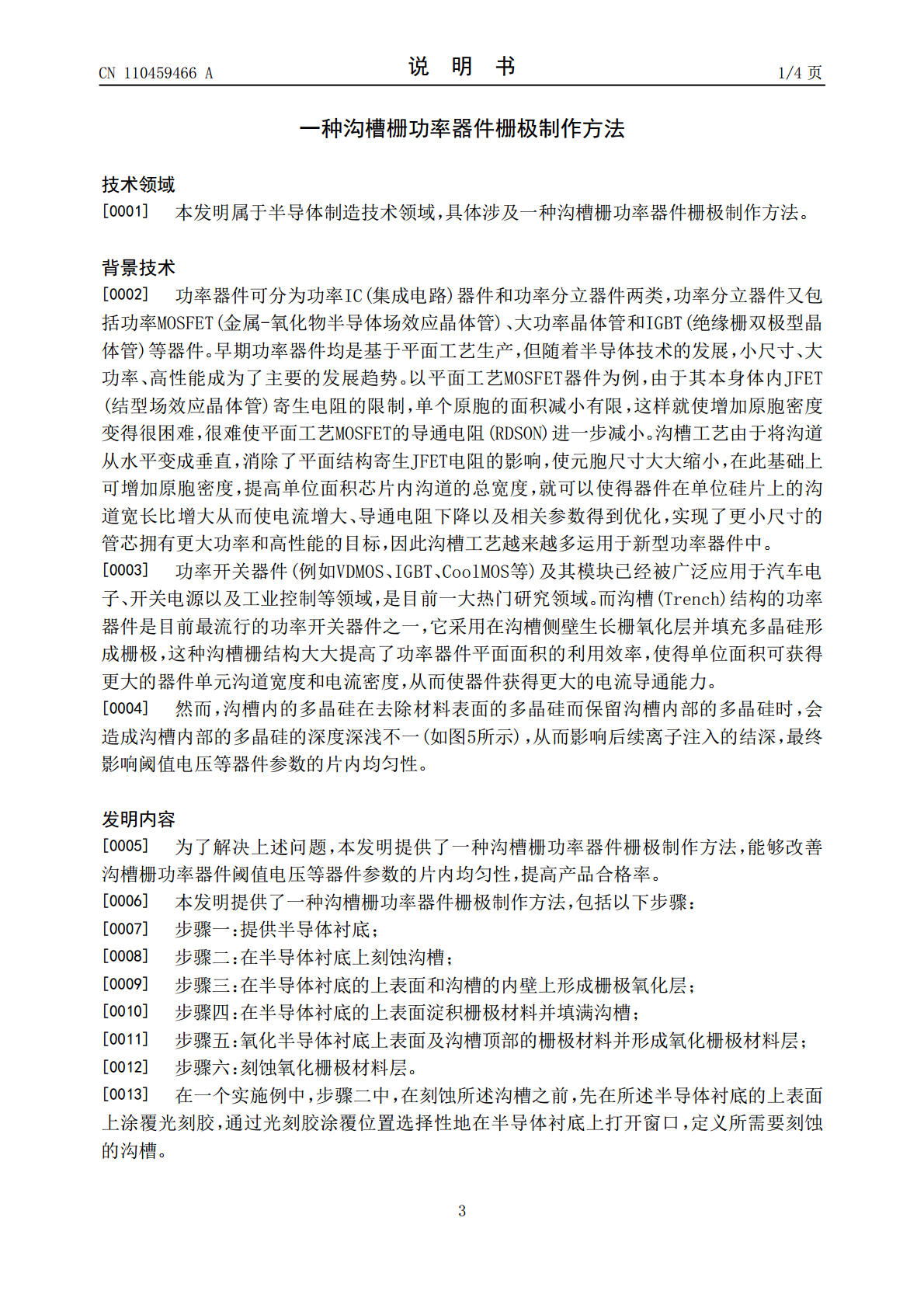

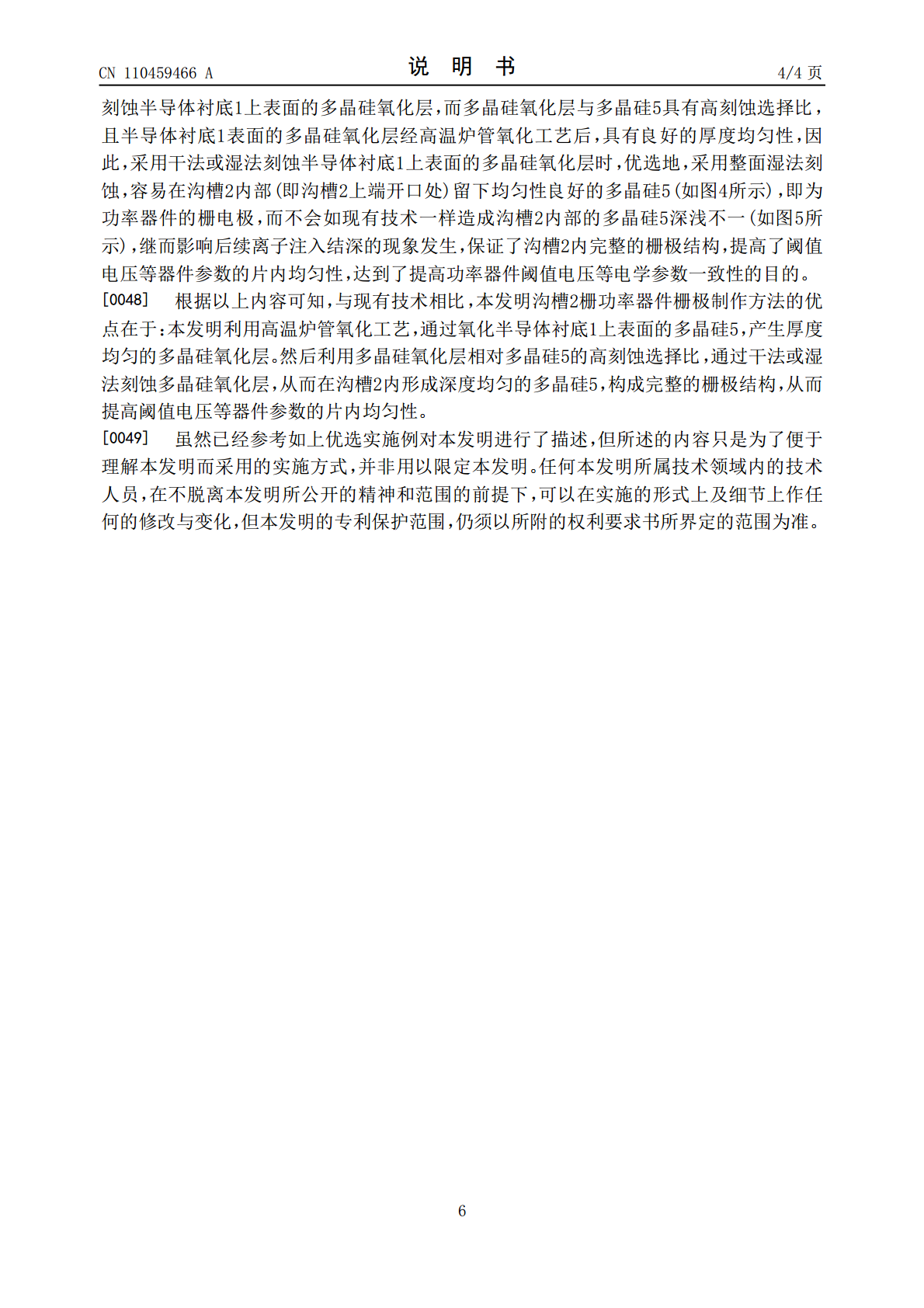

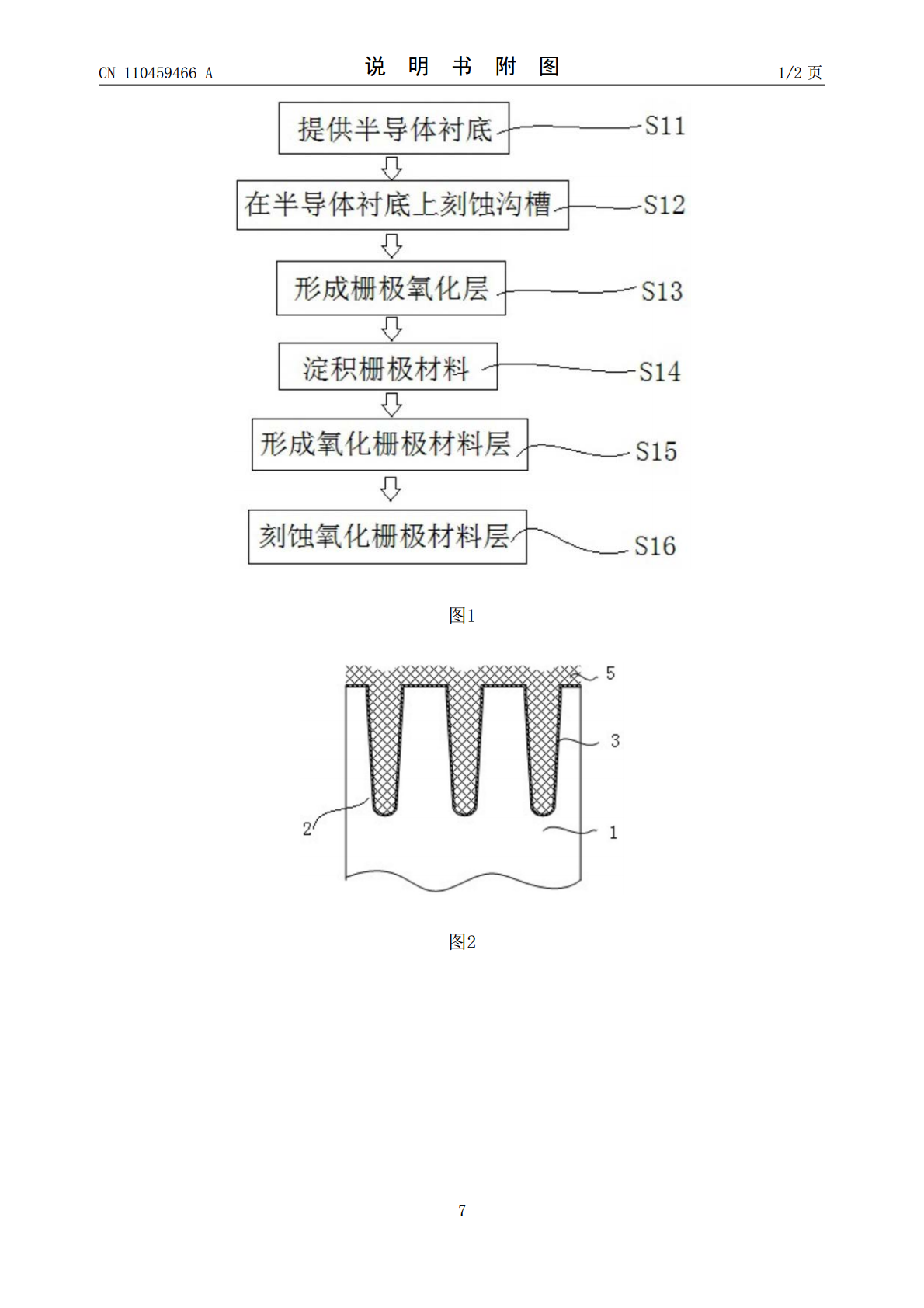

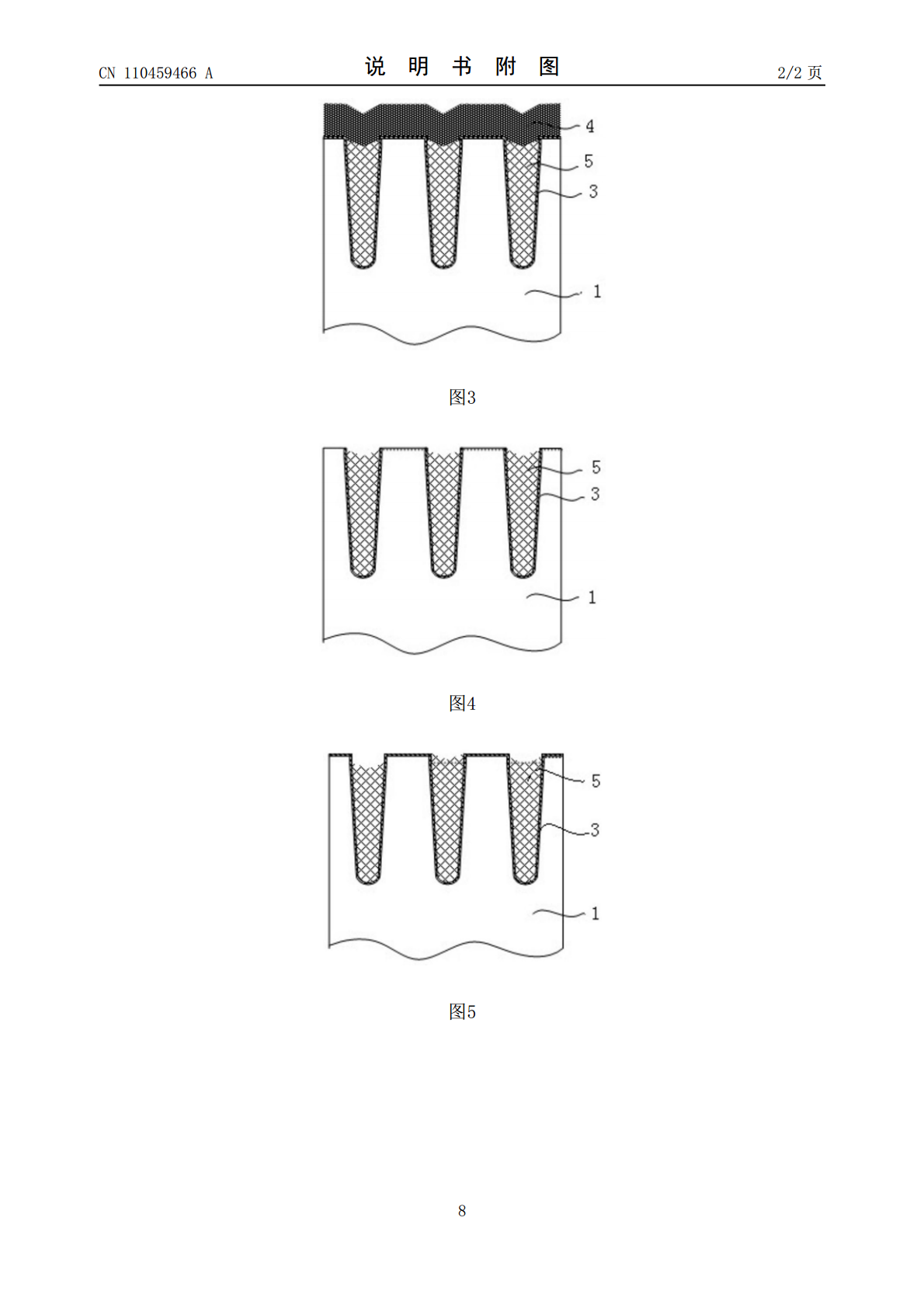

本发明涉及一种沟槽栅功率器件栅极制作方法,包括以下步骤:步骤一:提供半导体衬底;步骤二:在半导体衬底上刻蚀沟槽;步骤三:在半导体衬底的上表面和沟槽的内壁上形成栅极氧化层;步骤四:在半导体衬底的上表面淀积栅极材料并填满沟槽;步骤五:氧化栅极材料并形成氧化栅极材料层;步骤六:刻蚀氧化栅极材料层。本发明利用高温炉管氧化工艺,通过氧化半导体衬底上表面的多晶硅,产生厚度均匀的多晶硅氧化层。然后利用多晶硅氧化层相对多晶硅的高刻蚀选择比,通过干法或湿法刻蚀多晶硅氧化层,从而在沟槽内形成深度均匀的多晶硅,构成完整的栅极结

沟槽栅MOS功率器件及其栅极制作方法.pdf

本发明提供的一种沟槽栅MOS功率器件及其栅极制作方法,通过两次热氧化工艺在不同的位置处形成了厚薄不同的两种栅极氧化层,薄氧化层的设置使得阀值电压能够满足沟槽栅MOS功率器件的正常工作要求,保证MOS功率器件正常的开关动作,厚氧化层能够降低米勒电容,解决了开关行为难以调控的问题并降低了开关损耗,且厚氧化层耐载流子轰击能力较强,提高了整个器件的长程可靠性。本发明在保证MOS功率器件正常的开关动作的同时,降低了米勒电容,解决了开关行为难以调控的问题并降低了开关损耗,且提高了长程可靠性,不受阀值电压限制。

一种沟槽栅器件的制作方法.pdf

本发明公开了一种沟槽栅器件的制作方法,通过采用分步刻蚀工艺,形成相连通的经部分刻蚀的沟槽栅区和经完整刻蚀的隔离区,并填充隔离材料,然后采用原位再次定义沟槽栅区的方式形成沟槽栅,从而彻底消除了原来在沟槽栅与隔离区之间存在的残留硅漏电通路,减小了源漏之间的漏电,并可实现对沟槽栅区与隔离区的同步蚀刻,且与原沟槽栅制造工艺相兼容。

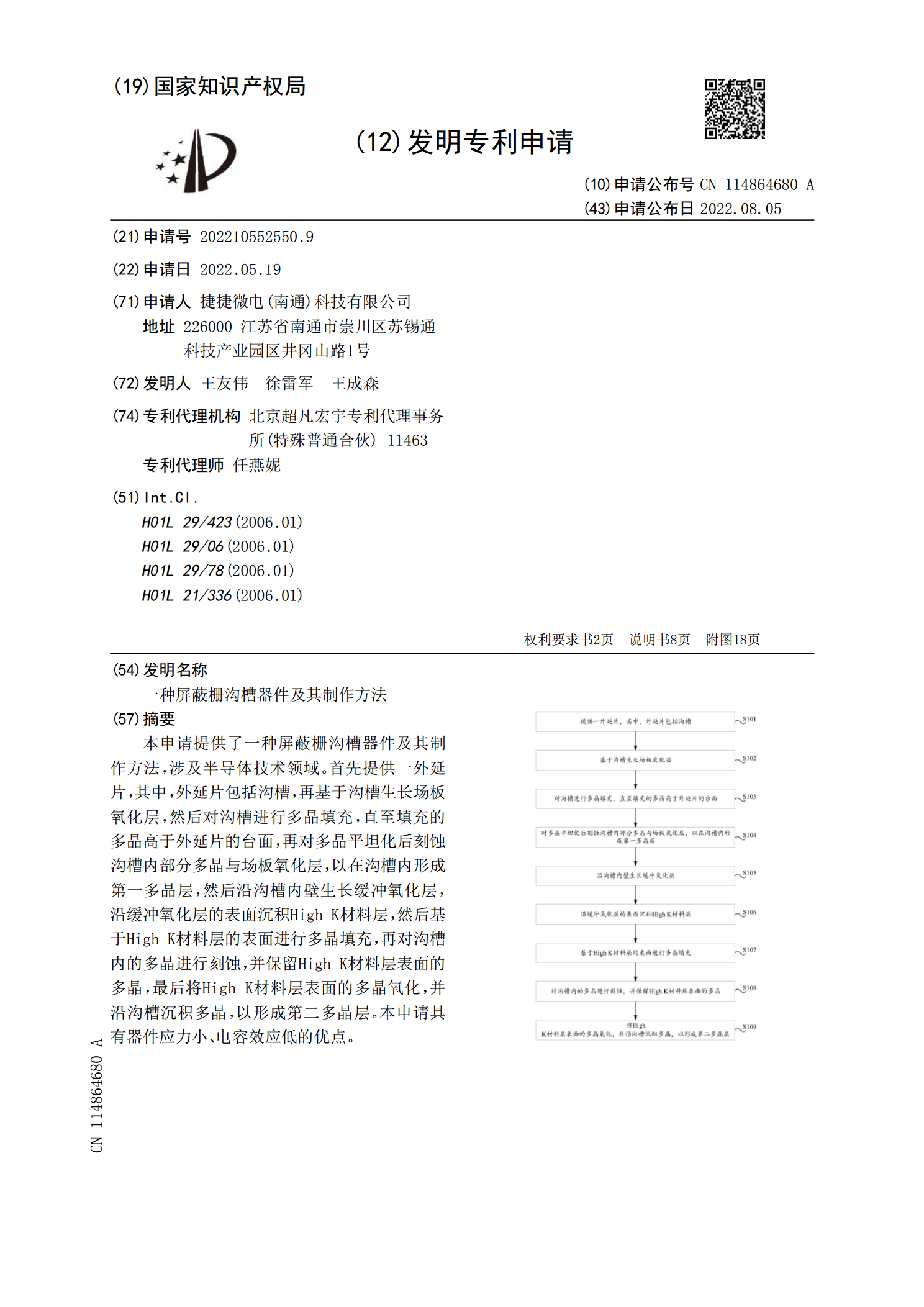

一种屏蔽栅沟槽器件及其制作方法.pdf

本申请提供了一种屏蔽栅沟槽器件及其制作方法,涉及半导体技术领域。首先提供一外延片,其中,外延片包括沟槽,再基于沟槽生长场板氧化层,然后对沟槽进行多晶填充,直至填充的多晶高于外延片的台面,再对多晶平坦化后刻蚀沟槽内部分多晶与场板氧化层,以在沟槽内形成第一多晶层,然后沿沟槽内壁生长缓冲氧化层,沿缓冲氧化层的表面沉积HighK材料层,然后基于HighK材料层的表面进行多晶填充,再对沟槽内的多晶进行刻蚀,并保留HighK材料层表面的多晶,最后将HighK材料层表面的多晶氧化,并沿沟槽沉积多晶,以形成第二多

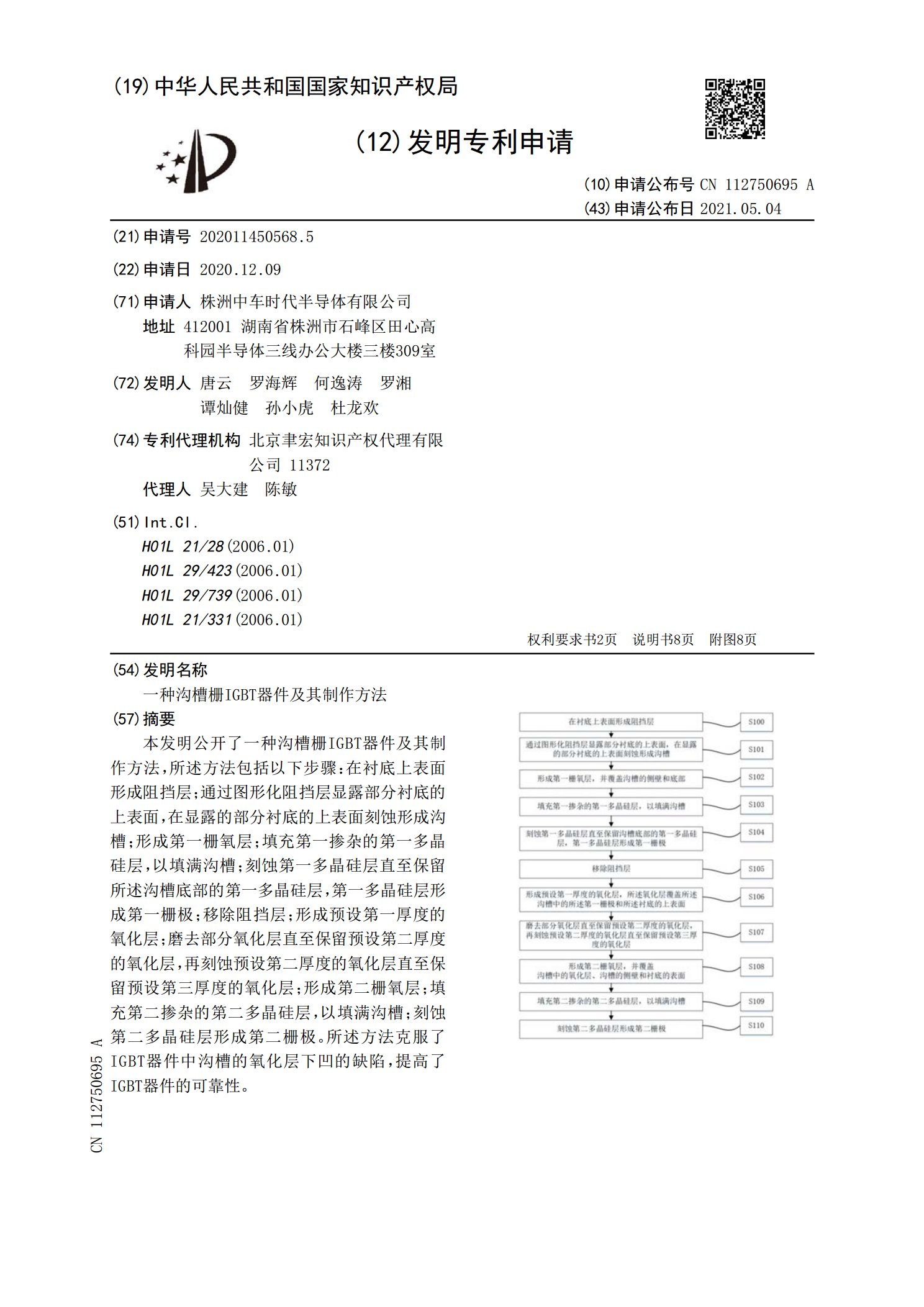

一种沟槽栅IGBT器件及其制作方法.pdf

本发明公开了一种沟槽栅IGBT器件及其制作方法,所述方法包括以下步骤:在衬底上表面形成阻挡层;通过图形化阻挡层显露部分衬底的上表面,在显露的部分衬底的上表面刻蚀形成沟槽;形成第一栅氧层;填充第一掺杂的第一多晶硅层,以填满沟槽;刻蚀第一多晶硅层直至保留所述沟槽底部的第一多晶硅层,第一多晶硅层形成第一栅极;移除阻挡层;形成预设第一厚度的氧化层;磨去部分氧化层直至保留预设第二厚度的氧化层,再刻蚀预设第二厚度的氧化层直至保留预设第三厚度的氧化层;形成第二栅氧层;填充第二掺杂的第二多晶硅层,以填满沟槽;刻蚀第二多晶