用于多核芯片的集成电路布局配线.pdf

一条****88

亲,该文档总共33页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

用于多核芯片的集成电路布局配线.pdf

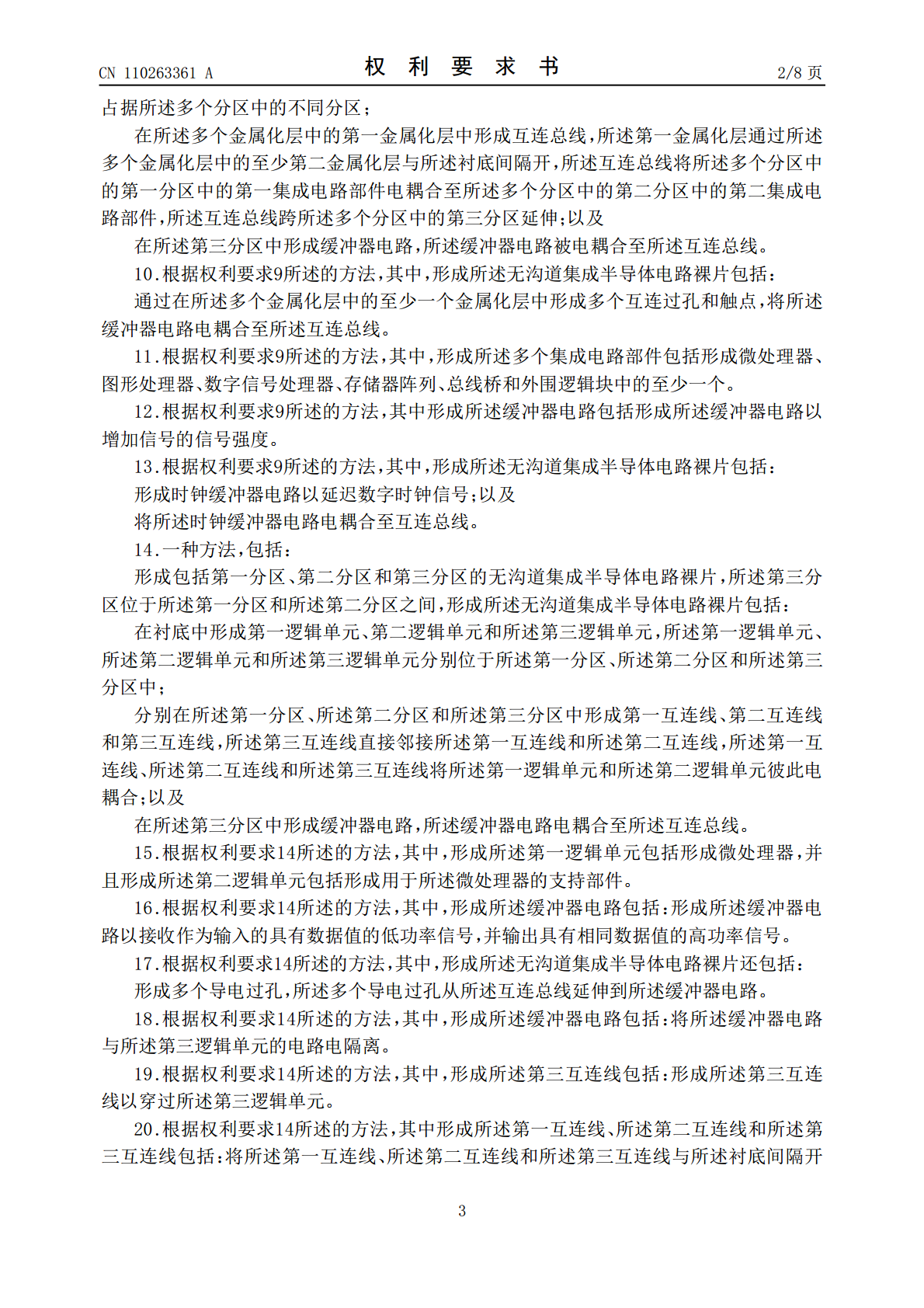

一种集成电路片上系统(SOC)包括半导体衬底、由形成于该衬底中的多个晶体管构成的多个部件以及在这些部件之间提供电连接的多条互连线路。无沟道设计的使用消除了在芯片的顶部表面上的互连沟道。反而,互连线路在顶部金属化层内互相抵靠,从而保留了5‑10%的芯片资产。通常沿着在部件之间的互连沟道定位的时钟缓冲器反而位于衬底的包含这些部件的区域内。无沟道集成电路的设计规则准许馈通互连并排除多扇出互连。

用于多核芯片的集成电路布局配线.pdf

一种集成电路片上系统(SOC)包括半导体衬底、由形成于该衬底中的多个晶体管构成的多个部件以及在这些部件之间提供电连接的多条互连线路。无沟道设计的使用消除了在芯片的顶部表面上的互连沟道。反而,互连线路在顶部金属化层内互相抵靠,从而保留了5-10%的芯片资产。通常沿着在部件之间的互连沟道定位的时钟缓冲器反而位于衬底的包含这些部件的区域内。无沟道集成电路的设计规则准许馈通互连并排除多扇出互连。

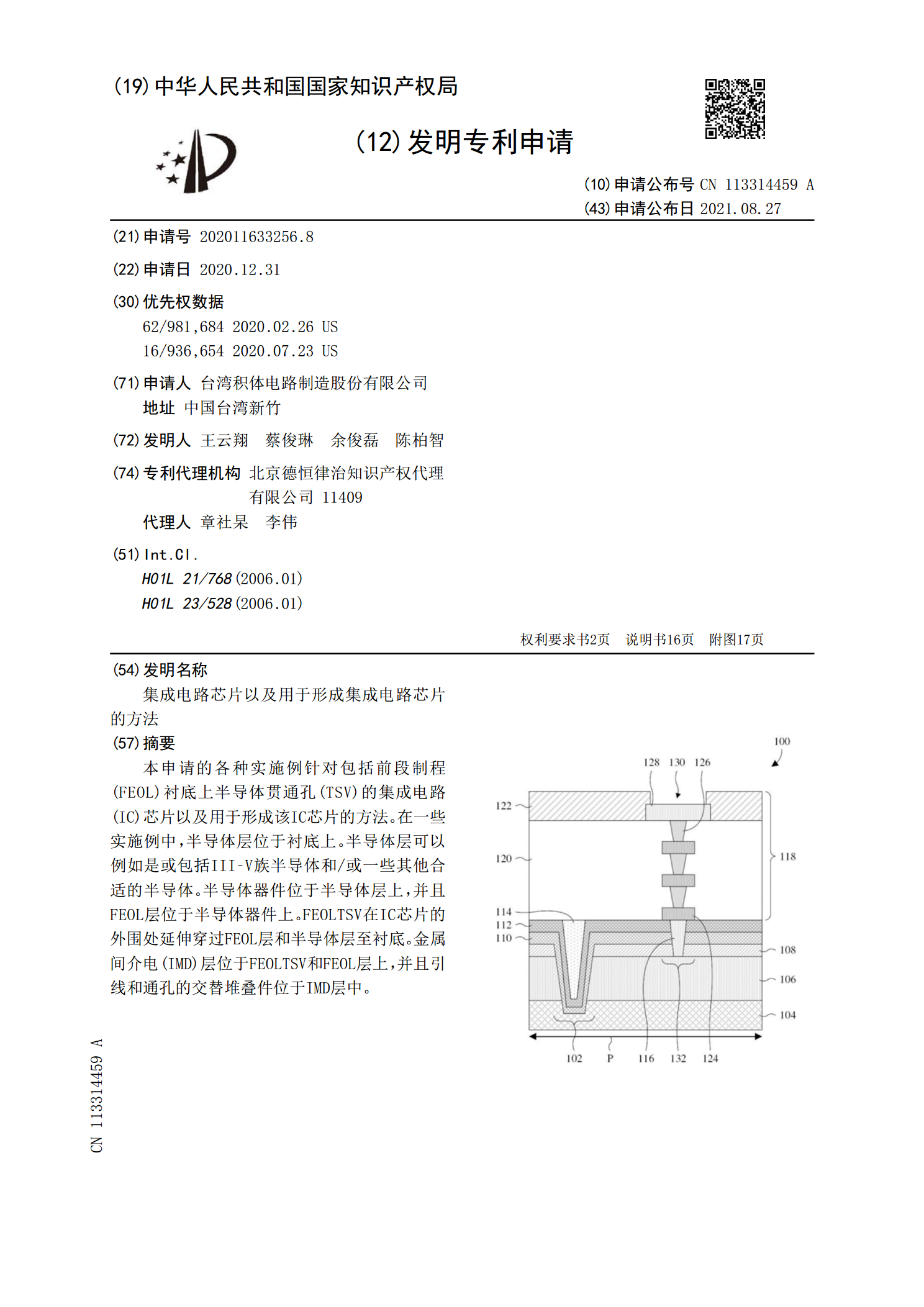

集成电路芯片以及用于形成集成电路芯片的方法.pdf

本申请的各种实施例针对包括前段制程(FEOL)衬底上半导体贯通孔(TSV)的集成电路(IC)芯片以及用于形成该IC芯片的方法。在一些实施例中,半导体层位于衬底上。半导体层可以例如是或包括III‑V族半导体和/或一些其他合适的半导体。半导体器件位于半导体层上,并且FEOL层位于半导体器件上。FEOLTSV在IC芯片的外围处延伸穿过FEOL层和半导体层至衬底。金属间介电(IMD)层位于FEOLTSV和FEOL层上,并且引线和通孔的交替堆叠件位于IMD层中。

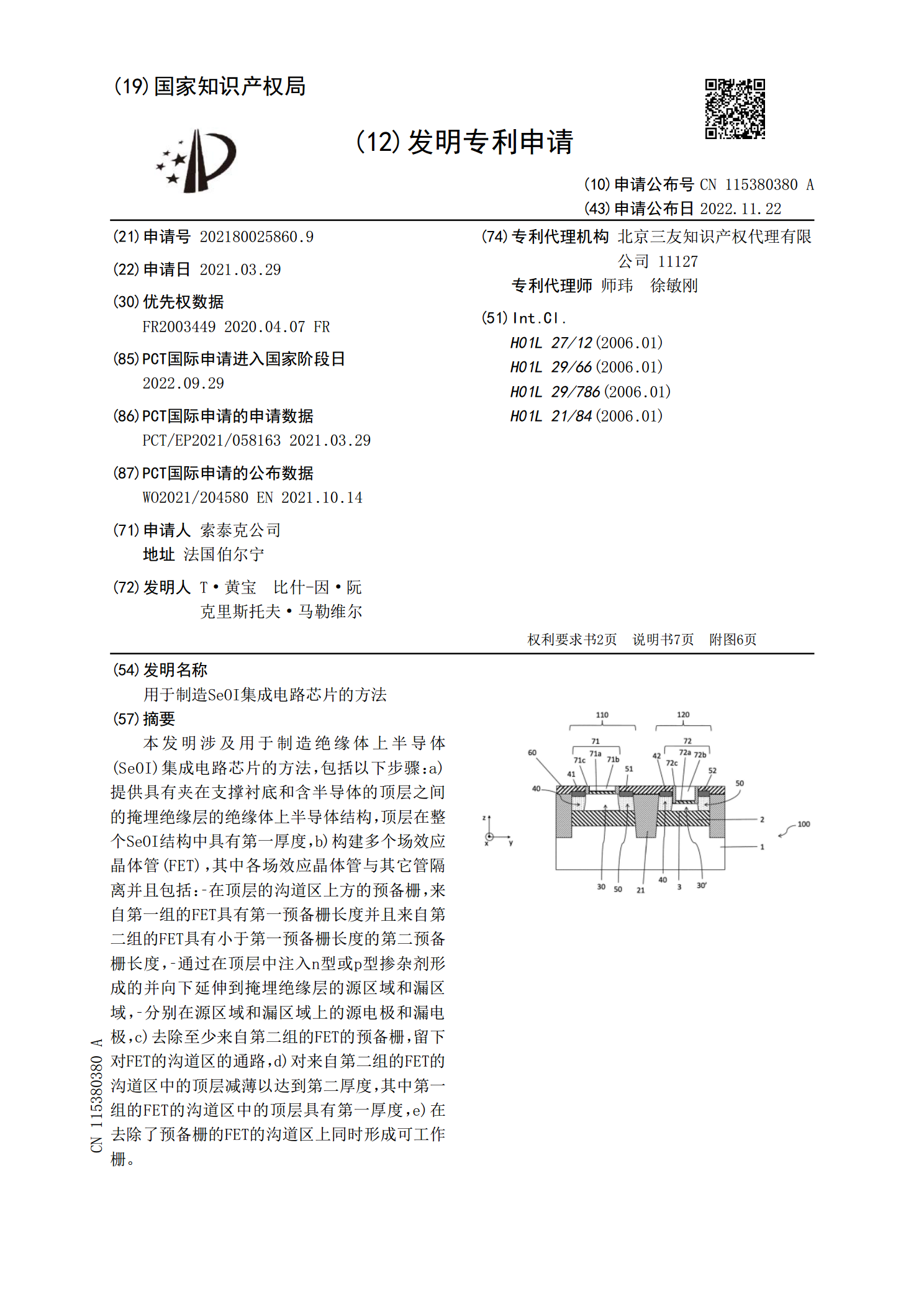

用于制造SeOI集成电路芯片的方法.pdf

本发明涉及用于制造绝缘体上半导体(SeOI)集成电路芯片的方法,包括以下步骤:a)提供具有夹在支撑衬底和含半导体的顶层之间的掩埋绝缘层的绝缘体上半导体结构,顶层在整个SeOI结构中具有第一厚度,b)构建多个场效应晶体管(FET),其中各场效应晶体管与其它管隔离并且包括:‑在顶层的沟道区上方的预备栅,来自第一组的FET具有第一预备栅长度并且来自第二组的FET具有小于第一预备栅长度的第二预备栅长度,‑通过在顶层中注入n型或p型掺杂剂形成的并向下延伸到掩埋绝缘层的源区域和漏区域,‑分别在源区域和漏区域上的源电极

专用集成电路芯片的布局结构及方法.pdf

一种专用集成电路芯片的布局结构及方法,其在运算核心中布置保留区域,将芯片的一角位置处的支撑区域由该角位置处的运算核心的保留区域形成,能够在芯片裸片仅需要单侧的输入输出区域时有效减少芯片裸片面积的浪费,并且可以增加芯片的运算核心的数量,从而提高芯片整体的运算性能。