一种阵列基板及其制备方法.pdf

盼易****君a

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种阵列基板及其制备方法.pdf

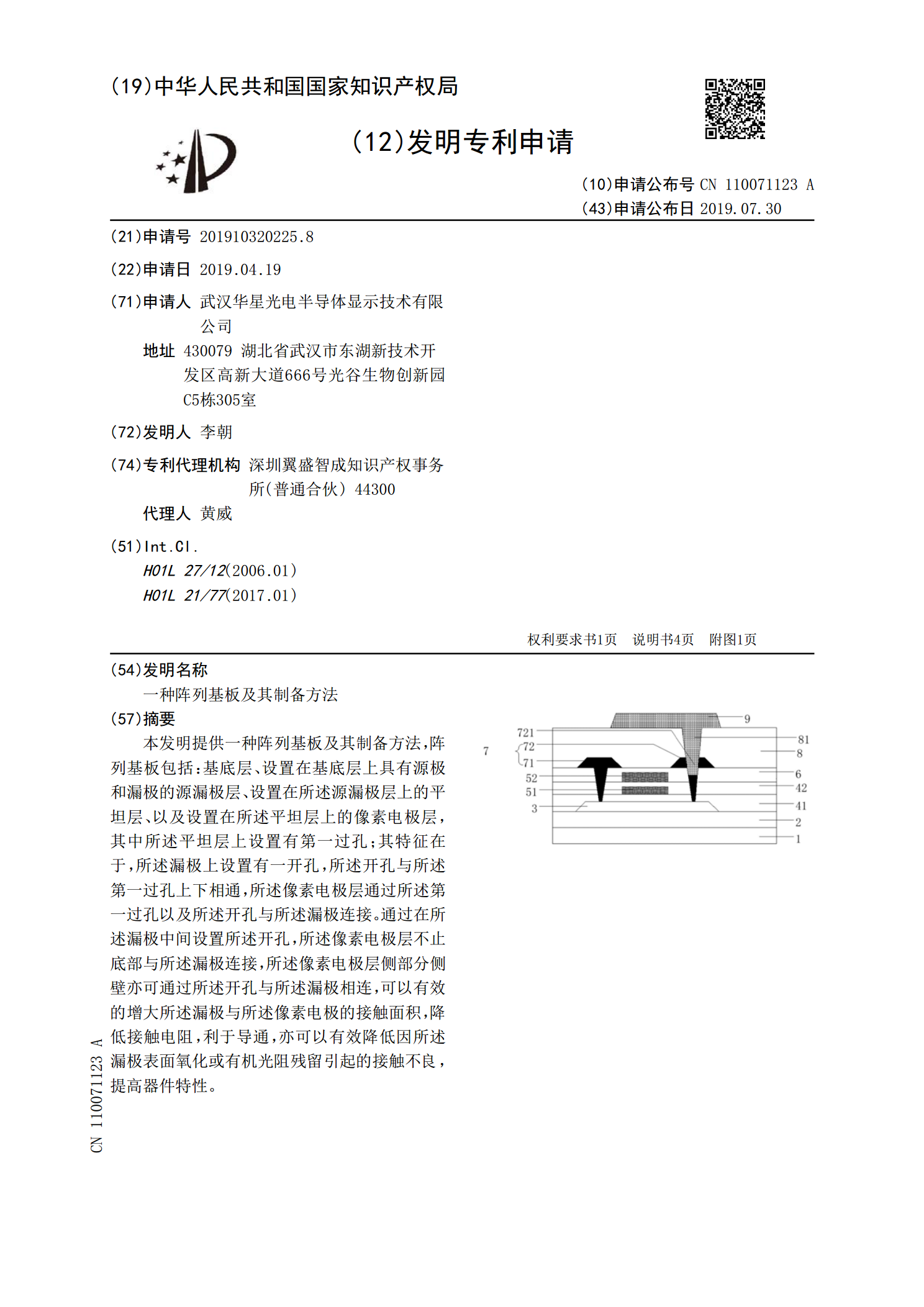

本发明提供一种阵列基板及其制备方法,阵列基板包括:基底层、设置在基底层上具有源极和漏极的源漏极层、设置在所述源漏极层上的平坦层、以及设置在所述平坦层上的像素电极层,其中所述平坦层上设置有第一过孔;其特征在于,所述漏极上设置有一开孔,所述开孔与所述第一过孔上下相通,所述像素电极层通过所述第一过孔以及所述开孔与所述漏极连接。通过在所述漏极中间设置所述开孔,所述像素电极层不止底部与所述漏极连接,所述像素电极层侧部分侧壁亦可通过所述开孔与所述漏极相连,可以有效的增大所述漏极与所述像素电极的接触面积,降低接触电阻,

一种阵列基板及其制备方法.pdf

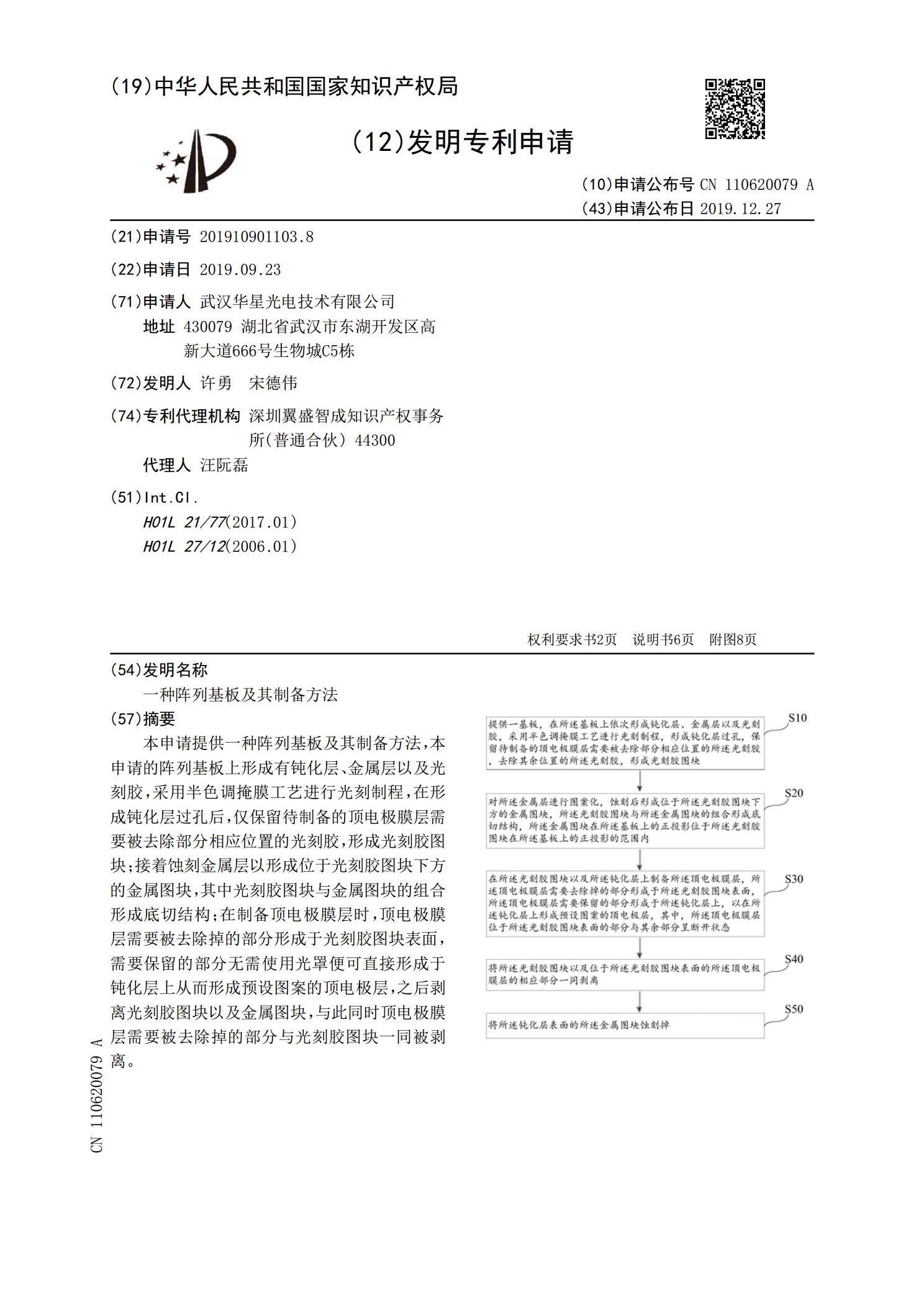

本申请提供一种阵列基板及其制备方法,本申请的阵列基板上形成有钝化层、金属层以及光刻胶,采用半色调掩膜工艺进行光刻制程,在形成钝化层过孔后,仅保留待制备的顶电极膜层需要被去除部分相应位置的光刻胶,形成光刻胶图块;接着蚀刻金属层以形成位于光刻胶图块下方的金属图块,其中光刻胶图块与金属图块的组合形成底切结构;在制备顶电极膜层时,顶电极膜层需要被去除掉的部分形成于光刻胶图块表面,需要保留的部分无需使用光罩便可直接形成于钝化层上从而形成预设图案的顶电极层,之后剥离光刻胶图块以及金属图块,与此同时顶电极膜层需要被去除

一种阵列基板及其制备方法.pdf

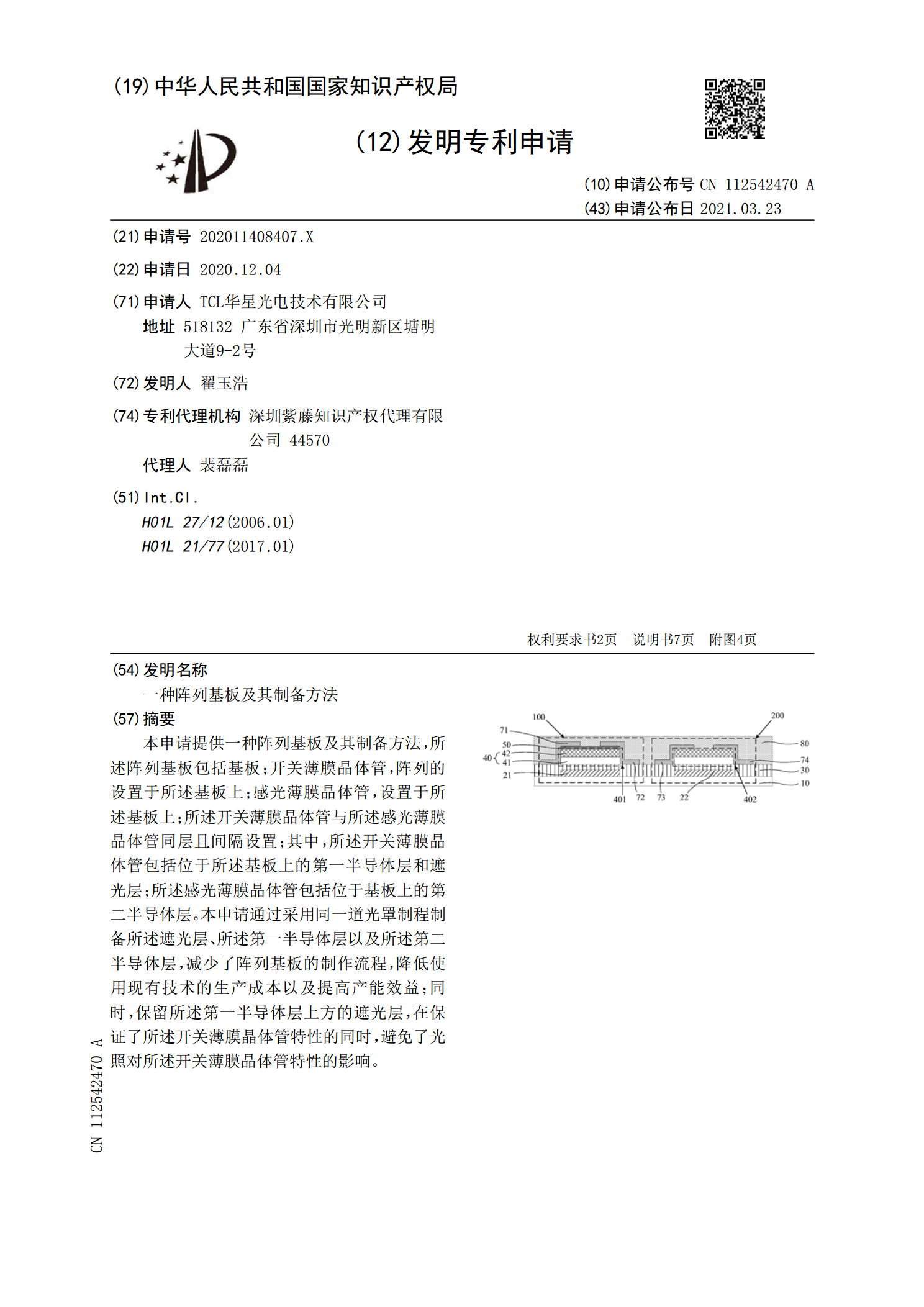

本申请提供一种阵列基板及其制备方法,所述阵列基板包括基板;开关薄膜晶体管,阵列的设置于所述基板上;感光薄膜晶体管,设置于所述基板上;所述开关薄膜晶体管与所述感光薄膜晶体管同层且间隔设置;其中,所述开关薄膜晶体管包括位于所述基板上的第一半导体层和遮光层;所述感光薄膜晶体管包括位于基板上的第二半导体层。本申请通过采用同一道光罩制程制备所述遮光层、所述第一半导体层以及所述第二半导体层,减少了阵列基板的制作流程,降低使用现有技术的生产成本以及提高产能效益;同时,保留所述第一半导体层上方的遮光层,在保证了所述开关薄

阵列基板及其制备方法.pdf

本发明提供一种阵列基板及其制备方法,该阵列基板包括同层设置的第一电极和第二电极、位于第一电极和第二电极的上方的第一介质层、位于第一介质层的上方的第一金属层、位于第一金属层上方的第二介质层以及位于第二介质层上方的第二金属层,其中,第二介质层延伸至第二电极表面,并设置有通孔,第二金属层通过通孔与第二电极电性连接,通孔未与第一介质层接触,第二电极上方无第一介质层,可彻底解决第一金属层在第一介质层的通孔内残留问题,可降低阵列基板制作时的困难,确保第一金属层不会与第二金属层发生电性连接的现象,避免第一金属层与第二金

阵列基板及其制备方法.pdf

本发明提供一种阵列基板及其制备方法,其制备方法包括:提供衬底基板,在衬底基板上制备对应于第一型薄膜晶体管的第一多晶硅层和对应于第二型薄膜晶体管的第二多晶硅层;在多晶硅层上制备光阻层,光阻层对应于第二型薄膜晶体管栅极区域的厚度大于其余区域光阻层的厚度;对多晶硅层进行第一离子掺杂;对光阻层进行处理,减薄并保留第一型薄膜晶体管栅极对应区域的光阻层,剥离其余区域的光阻层;对多晶硅层进行第二离子掺杂;剥离剩余光阻层。本发明通过制备出针对不同离子植入区域不同厚度的光阻层,可各采用一道离子植入制程完成第一离子和第二离子