刻蚀方法以及半导体器件的制造方法.pdf

思洁****爱吗

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

刻蚀方法以及半导体器件的制造方法.pdf

本发明提供了一种刻蚀方法,将先进图形膜层分成两步刻蚀,并在两步先进图形膜层刻蚀中间增加了去除未曝光区介质抗反射层的步骤,后续利用两步先进图形膜层刻蚀后残留的先进图形膜层作为掩膜,对目标刻蚀层进行刻蚀,通过上述方法解决了刻蚀过程中无法去除未曝光区的所述介质抗反射层的问题,并避免了形成后续制程缺陷的问题。

凹槽刻蚀方法以及半导体器件制造方法.pdf

本发明提供了一种凹槽刻蚀方法以及半导体器件制造方法。根据本发明的凹槽刻蚀方法包括:在硅片上涂覆具有具体厚度的光刻胶;形成所述光刻胶的用于刻蚀出凹槽的图案;以及利用形成有图案的光刻胶,执行等离子刻蚀;其中,对光刻胶的所述具体厚度以及等离子刻蚀过程中的刻蚀能量进行控制,以使等离子体消耗完所述光刻胶而刻蚀到光刻胶的下面的硅片。利用刻蚀光刻胶残留的特点,根据本发明,可以在不执行硼磷硅玻璃回流的情况下形成上部的角轮廓形成为圆弧形状的凹槽,从而简化了工艺步骤,降低了工艺成本,并且缩短了工艺时间。

半导体器件以及制造半导体器件的方法.pdf

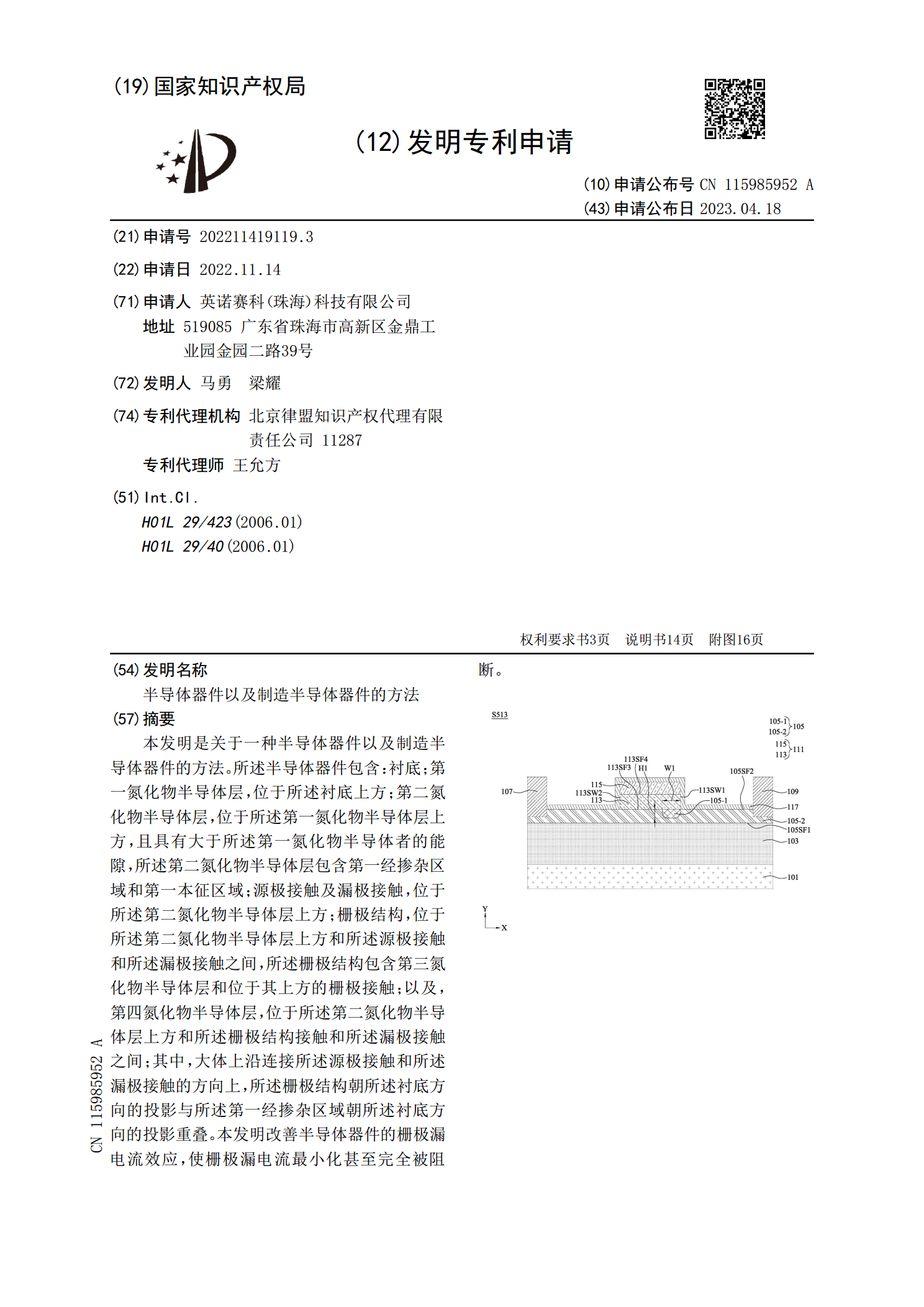

本发明是关于一种半导体器件以及制造半导体器件的方法。所述半导体器件包含:衬底;第一氮化物半导体层,位于所述衬底上方;第二氮化物半导体层,位于所述第一氮化物半导体层上方,且具有大于所述第一氮化物半导体者的能隙,所述第二氮化物半导体层包含第一经掺杂区域和第一本征区域;源极接触及漏极接触,位于所述第二氮化物半导体层上方;栅极结构,位于所述第二氮化物半导体层上方和所述源极接触和所述漏极接触之间,所述栅极结构包含第三氮化物半导体层和位于其上方的栅极接触;以及,第四氮化物半导体层,位于所述第二氮化物半导体层上方和所述

晶边刻蚀方法和半导体器件制造方法.pdf

本发明提供一种晶边刻蚀方法和半导体器件制造方法,所述晶边刻蚀方法,先通过旋转晶圆来对晶圆上的待晶边刻蚀的膜层的晶边区域进行多次干法刻蚀,使所述膜层的晶边的均匀性达到要求,避免晶边非均匀性而导致的晶圆翘曲问题,再对所述膜层的晶边区域进行湿法清洗,可以进一步的去除所述干法刻蚀造成的膜层不对称性以及残留缺陷,从而更好地改善膜层在晶片边缘造成的缺陷、击穿以及应力过剩等问题,提高了最终制造的半导体器件的良率;进一步地,当所述晶圆的正面上有待晶边刻蚀的上膜层且背面上有待晶边刻蚀的下膜层时,所述干法刻蚀和湿法刻蚀的叠加

干法刻蚀机台及半导体器件的制造方法.pdf

本发明提供了一种干法刻蚀机台及半导体器件的制造方法,通过在干法刻蚀机台的冷却台的上方设置通入吹扫气体的供气管道,并在冷却台的下方设置抽气管道,将经过干法刻蚀工艺的晶圆传送至所述冷却台,并对晶圆通入吹扫气体吹扫,将干法刻蚀工艺带出来的反应气体吹扫干净,防止干法刻蚀工艺反应生成的聚合物或副产物会与空气中的水蒸气反应,引发缺陷产生,并防止已经完成干法刻蚀工艺晶圆上的气体残留,与未完成干法刻蚀工艺晶圆上的光刻胶发生反应,进而影响刻蚀形貌;该方法无需使用缓存台运转,避免了因缓存台不足影响机台的WPH,有利于提高生产