干法刻蚀机台及半导体器件的制造方法.pdf

是飞****文章

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

干法刻蚀机台及半导体器件的制造方法.pdf

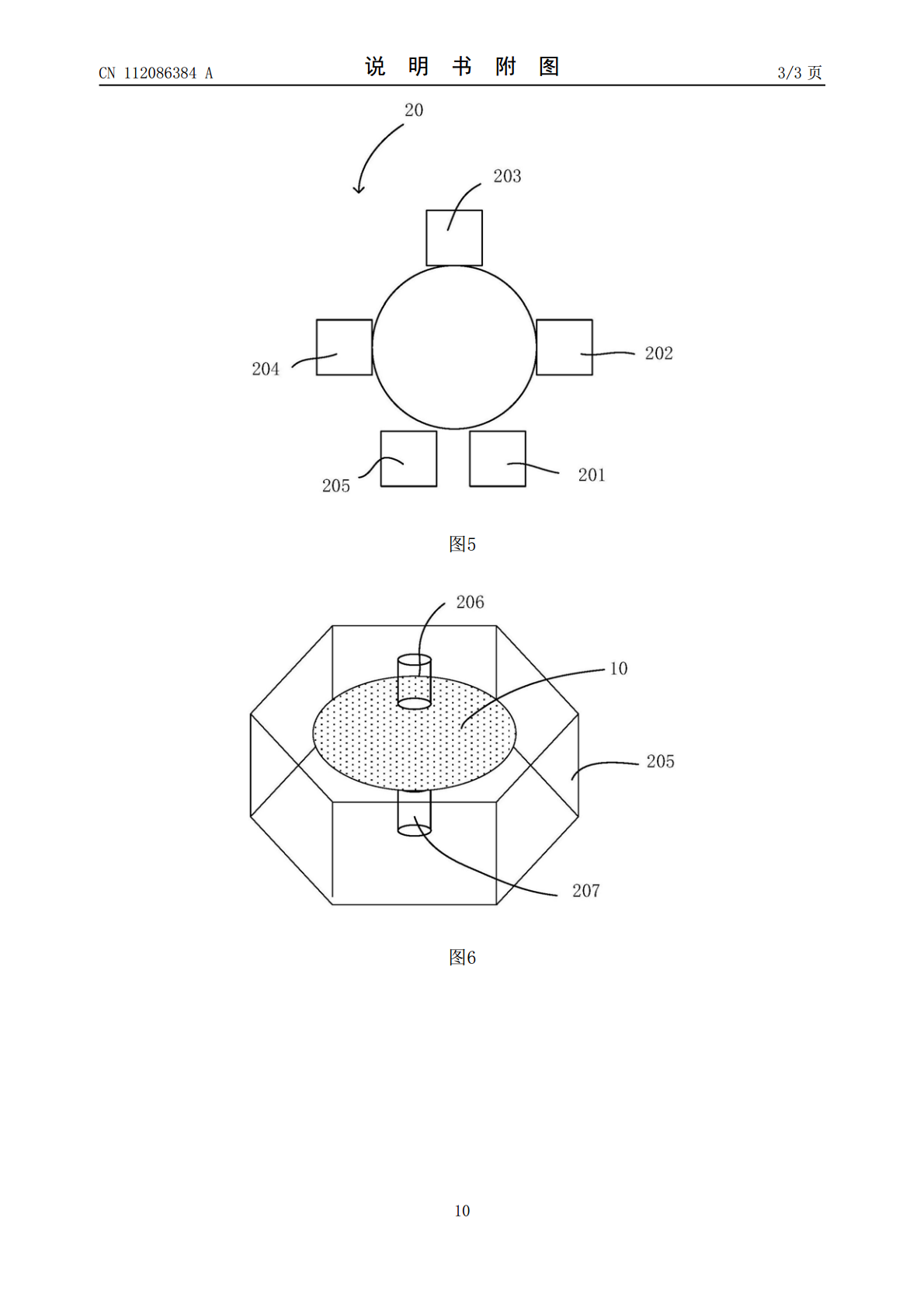

本发明提供了一种干法刻蚀机台及半导体器件的制造方法,通过在干法刻蚀机台的冷却台的上方设置通入吹扫气体的供气管道,并在冷却台的下方设置抽气管道,将经过干法刻蚀工艺的晶圆传送至所述冷却台,并对晶圆通入吹扫气体吹扫,将干法刻蚀工艺带出来的反应气体吹扫干净,防止干法刻蚀工艺反应生成的聚合物或副产物会与空气中的水蒸气反应,引发缺陷产生,并防止已经完成干法刻蚀工艺晶圆上的气体残留,与未完成干法刻蚀工艺晶圆上的光刻胶发生反应,进而影响刻蚀形貌;该方法无需使用缓存台运转,避免了因缓存台不足影响机台的WPH,有利于提高生产

半导体器件的制造方法及半导体器件.pdf

本申请公开了一种半导体器件的制造方法及半导体器件。其中,该半导体器件的制造方法包括提供一半导体衬底;在衬底上形成未掺杂氧化层;对未掺杂氧化层进行元素掺杂,得到具有目标元素的掺杂氧化层;在掺杂氧化层和衬底之间形成未掺杂氧化层;判断栅氧化层的厚度和所述目标元素的浓度是否分别达到第一预设值和第二预设值,栅氧化层包括未掺杂氧化层和掺杂氧化层;若否,则返回执行对未掺杂氧化层进行元素掺杂,得到掺杂氧化层的步骤,直至栅氧化层的厚度和目标元素的浓度分别达到第一预设值和第二预设值。本方案可以提高栅氧化层的可靠性。

半导体器件及半导体器件的制造方法.pdf

一种半导体器件及一用于此半导体器件的栅极堆叠的制造方法。此器件包括一栅极堆叠,其具有一设置于此器件的沟道区上的栅极绝缘层及一借由此栅极绝缘层与沟道区绝缘的金属层。此金属层包含功函数调控杂质,其具有从源极区至漏极区沿着金属层的长度而变化的浓度轮廓。栅极堆叠在此器件的源极区和/或漏极区附近具有一第一有效功函数,及在朝向该沟道区的中央处具有一不同于第一有效功函数的第二有效功函数。

半导体器件制造方法及半导体器件.pdf

本发明公开了一种半导体器件制造方法及半导体器件。该方法在相邻MOS晶体管之间的沟槽底部预留间隔层,通过该间隔层改变沟槽底部的深宽比,不仅有效避免了在沟槽底部容易造成第二层多晶硅残余的问题,防止相邻两个MOS晶体管之间因沟槽底部有第二侧层多晶硅残余而导致半导体器件内部发生短路现象;而且采用本半导体器件制造方法也不会破坏第二层多晶硅的结构。与现有技术相比较,本半导体器件制造方法优化了工艺过程,增加了第二侧层多晶硅蚀刻的工艺窗口,提升了半导体器件的质量。

半导体器件、半导体基板、半导体基板的制造方法及半导体器件的制造方法.pdf

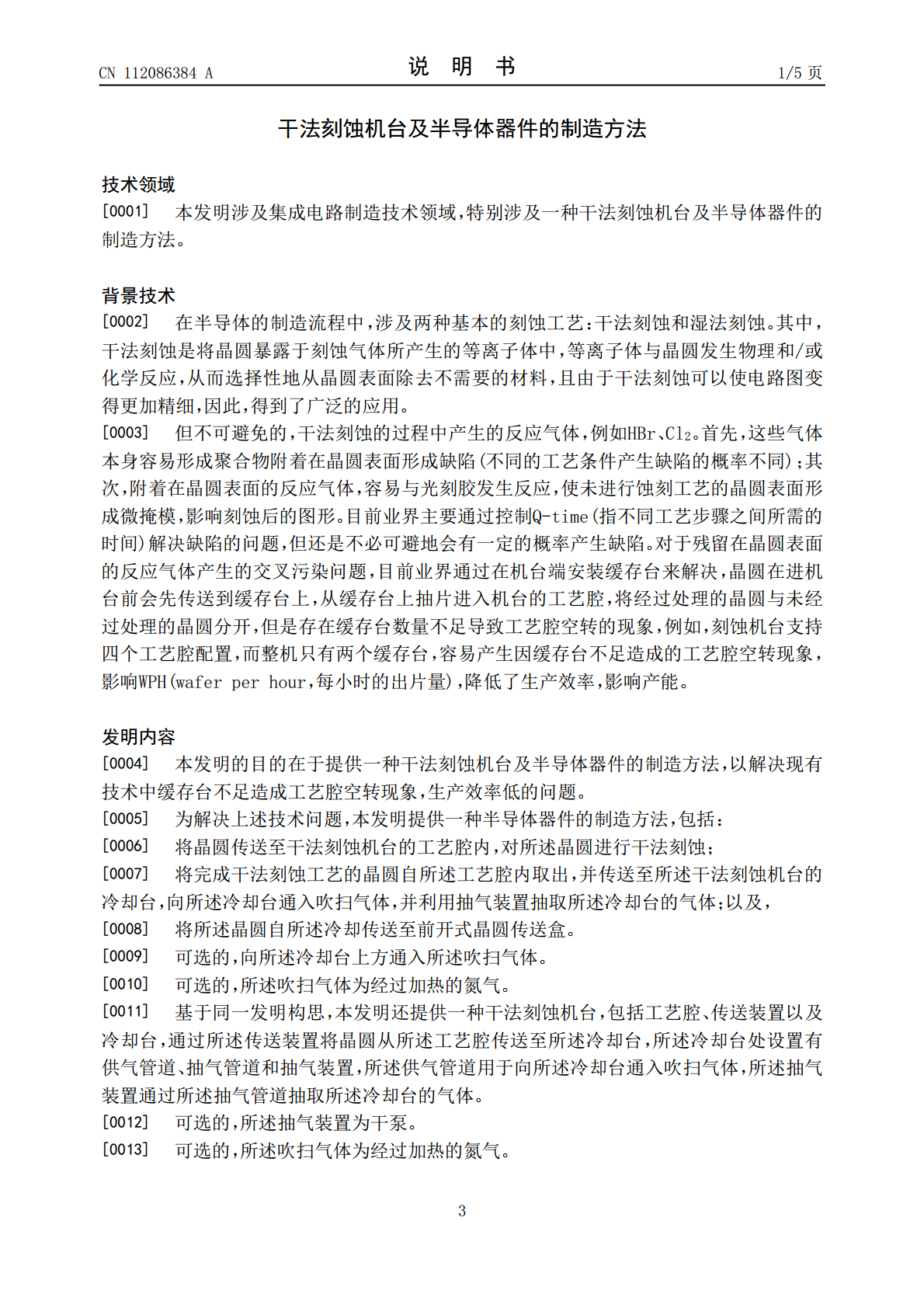

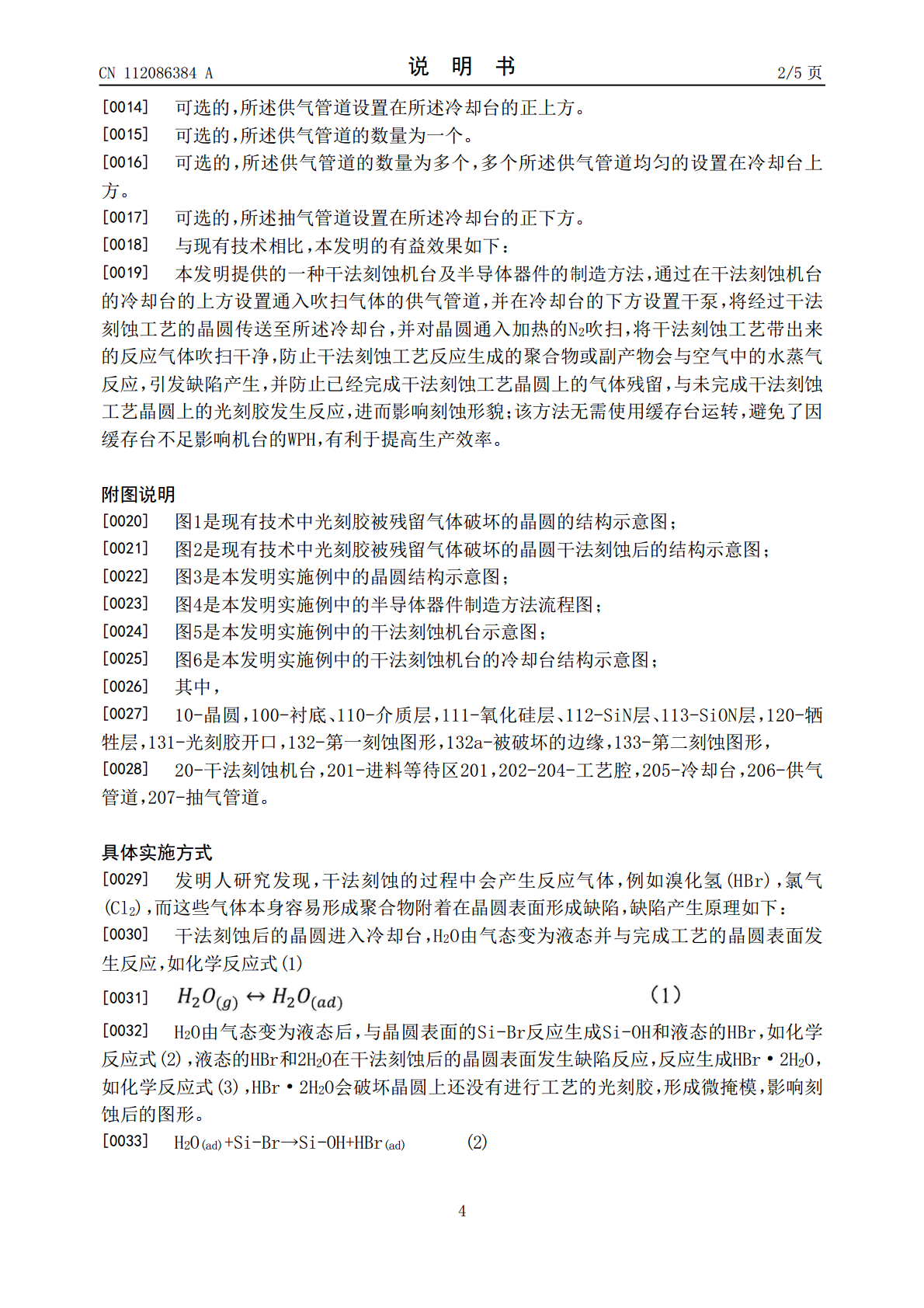

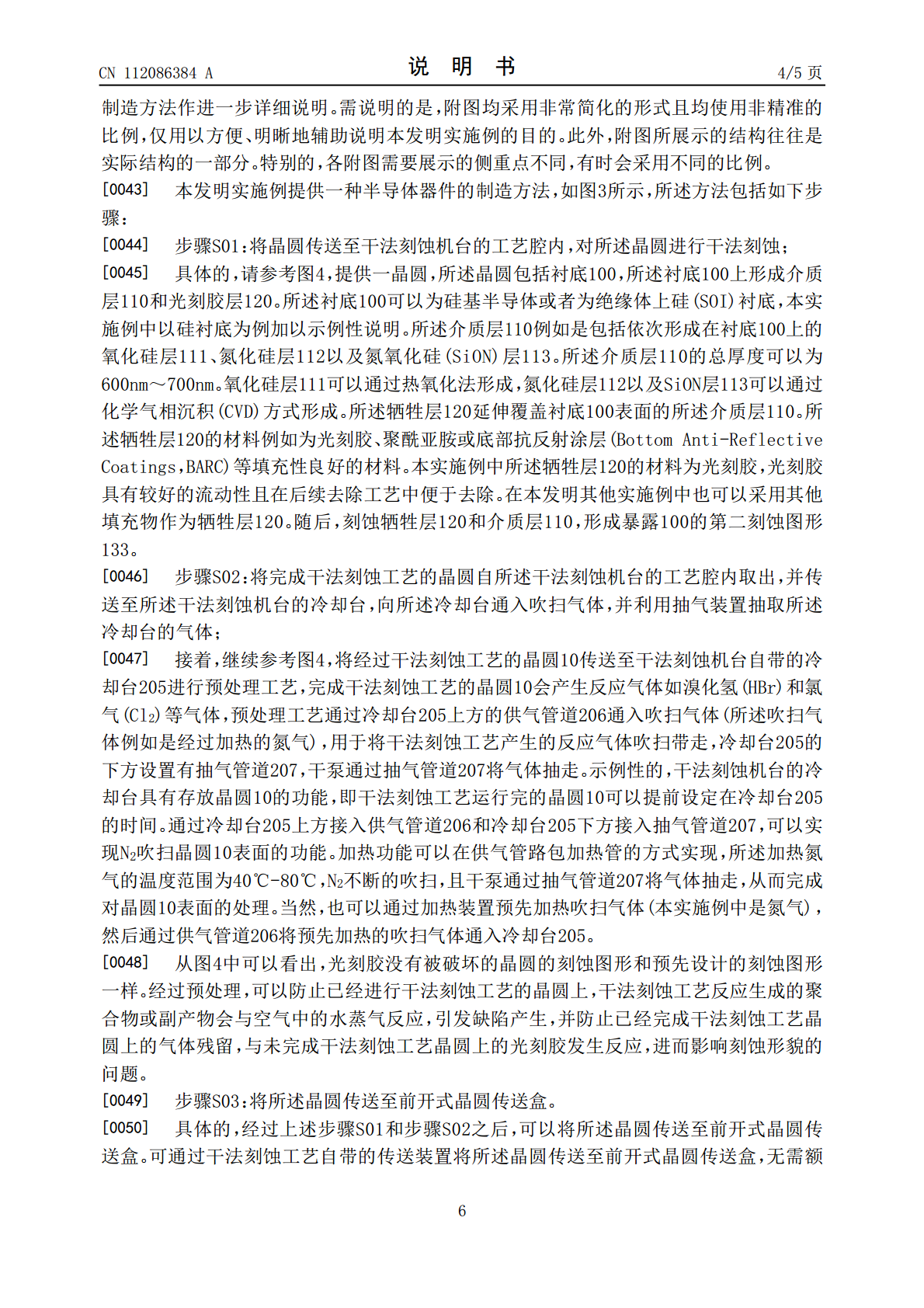

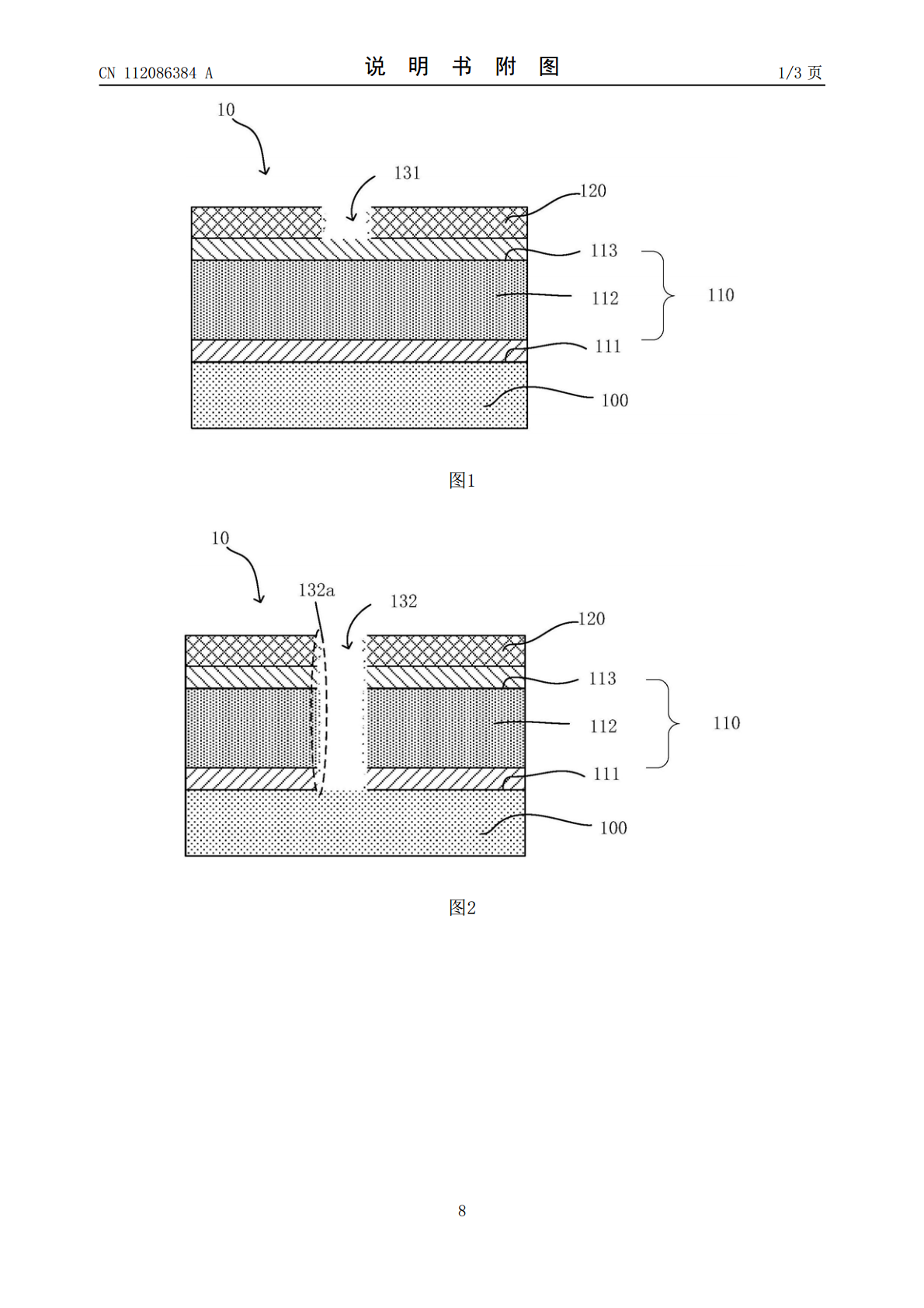

提供一种半导体器件,在Ge基板上形成的P沟道型MISFET的第一源极及第一漏极由以下化合物构成:Ge原子与镍原子的化合物;Ge原子与钴原子的化合物;或Ge原子、与镍原子和钴原子的化合物构成,在由III-V族化合物半导体构成的半导体晶体层上形成的N沟道型MISFET的第二源极及第二漏极由以下化合物构成:III族原子及V族原子、与镍原子的化合物;III族原子及V族原子、与钴原子的化合物;或III族原子及V族原子、与镍原子及钴原子的化合物构成。