一种可组合式的三维多芯片封装结构.pdf

是丹****ni

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种可组合式的三维多芯片封装结构.pdf

本发明公开了一种可组合式的三维多芯片封装结构,涉及新一代信息技术,针对现有技术中封装密度和芯片性能之间的矛盾问题提出本方案。包括层叠设置且留有间隙的上转接板和下转接板;两块转接板合理设置三块以上的芯片,而且垂直错开,再利用Via合理串联电性关系。优点在于,不同层的芯片封装可单独加工后进行组装,且封装形式多样实用,包括埋入式无源器件IPD、异质结构芯片、多层封装以及TSV/TGV等形式,为多样化多需求的射频系统封装提供了可靠的结构。

多芯片封装结构、多芯片封装结构的制造方法.pdf

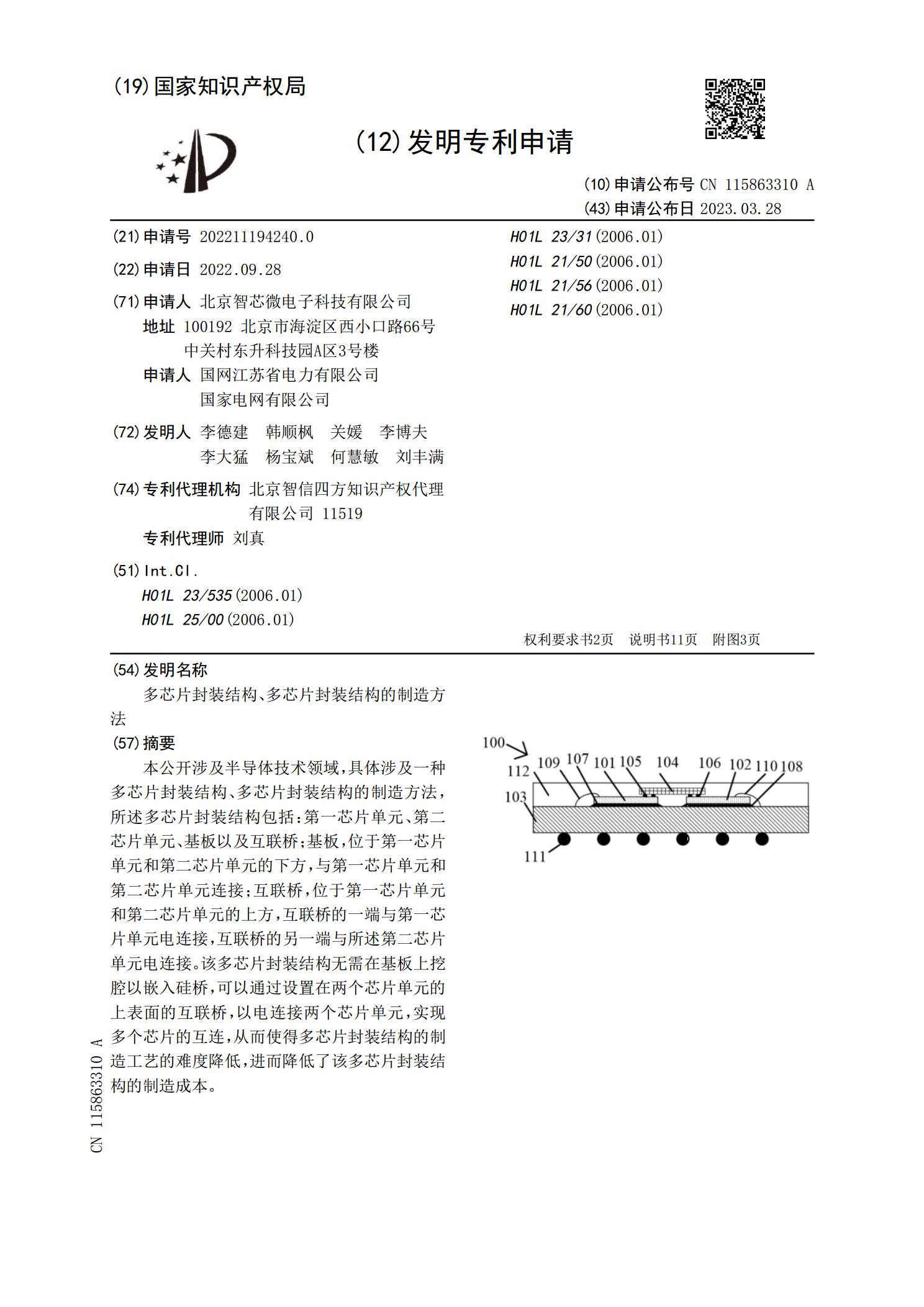

本公开涉及半导体技术领域,具体涉及一种多芯片封装结构、多芯片封装结构的制造方法,所述多芯片封装结构包括:第一芯片单元、第二芯片单元、基板以及互联桥;基板,位于第一芯片单元和第二芯片单元的下方,与第一芯片单元和第二芯片单元连接;互联桥,位于第一芯片单元和第二芯片单元的上方,互联桥的一端与第一芯片单元电连接,互联桥的另一端与所述第二芯片单元电连接。该多芯片封装结构无需在基板上挖腔以嵌入硅桥,可以通过设置在两个芯片单元的上表面的互联桥,以电连接两个芯片单元,实现多个芯片的互连,从而使得多芯片封装结构的制造工艺的

一种多芯片的封装结构及其封装方法.pdf

本发明公开了一种多芯片的封装结构及其封装方法,属于半导体芯片封装技术领域。其扇出型芯片封装单元设置的芯片(1)为两个或两个以上,芯片(1)彼此间仅留毛细间隙(2),所述芯片(1)彼此间于再布线层(6)的上表面设置毛细封堵部件(3),毛细封堵部件(3)完全填充毛细间隙(2)的下部,所述塑封料(4)与毛细封堵部件(3)密接。本发明提供了解决芯片开裂、产品翘曲等问题的多芯片的封装结构及其封装方法,提高了产品的良率。

多芯片封装结构.pdf

本发明为有关一种多芯片封装结构,于封装载板于固晶区四侧边分别设有外接引脚、可供电性连接至外部预设电子电路,并于固晶区处固设第一芯片,且第一芯片分别设有内部电路及隔离封圈结构,则于内部电路外部四侧边分别由内往外依序电性连接有多个输入及输出单元、多个第一焊垫,而各第一焊垫分别利用第一导线电性连接至相对应的外接引脚,再于至少一侧的内部电路与多个输入及输出单元之间设有多个虚设焊垫,另于第一芯片的内部电路上堆叠固设第二芯片,该第二芯片表面设有至少一组第二焊垫,可分别利用第二导线经由各虚设焊垫电性连接至相对应外部引脚

多芯片封装结构及封装方法.pdf

本发明提供一种多芯片封装结构及封装方法,封装结构包括基板、第一芯片组及第二芯片组,基板包括相对设置的顶面、底面以及贯穿顶面及底面的开孔,第一芯片组与基板电性连接,且第一芯片组面向顶面的第一表面上具有第一连接部,第二芯片组包括相对设置的第二表面及第三表面,第二表面面向第一表面且具有第二连接部,其中,第一连接部直接电性连接第二连接部,且至少部分第二芯片组位于开孔内或者位于开孔沿着基板的厚度方向的延伸空间内。本发明的第一芯片组与第二芯片组直接串接在一起,可省去额外的布线,进而提高传输效率,另外,开孔的设置不仅便