掩膜版、阵列基板的制作方法及显示面板.pdf

书生****aa

亲,该文档总共18页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

掩膜版、阵列基板的制作方法及显示面板.pdf

本发明公开了一种掩膜版、阵列基板的制作方法及显示面板。其中,所述掩膜版包括:与所述沟道区域对应的第一曝光区、位于所述第一曝光区一侧的待形成源极的第二曝光区、位于所述第一曝光区相对的另一侧的待形成漏极的第三曝光区,以及位于所述第二曝光区部分边缘的与所述第一曝光区不重叠的第四曝光区,所述第一曝光区与所述第四曝光区均为半透光区域。本发明技术方案的掩膜版在曝光和显影的过程中,能使得部分光阻遗留在与第一曝光区和第四曝光区相对应的区域内,对待形成沟道区域和待形成源极的区域进行保护,从而保证源极的加工尺寸,提高源极与栅

掩膜版、阵列基板的制作方法及显示面板.pdf

本发明公开了一种掩膜版、阵列基板的制作方法及显示面板。其中,所述掩膜版包括:与沟道区域对应的第一曝光区、位于所述第一曝光区一侧的待形成源极的第二曝光区、位于第一曝光区相对的另一侧的待形成漏极的第三曝光区,以及位于第三曝光区背离所述第一曝光区一侧的第四曝光区,所述第一曝光区与第四曝光区均为半透光区域。本发明技术方案的掩膜版在曝光和显影的过程中,能使得部分光阻遗留在与第一曝光区和第四曝光区相对应的区域内,对待形成沟道区域和待形成漏极的区域进行保护,从而提升画素的开口率。

阵列基板、掩膜板、显示装置及阵列基板的制作方法.pdf

本申请提供的一种阵列基板、掩膜板、显示装置及阵列基板的制作方法,包括:衬底基板,所述衬底基板包括显示区和扇出区,所述扇出区设置有多条栅线,相邻所述栅线的间距为4.2μm至4.7μm。本申请通过将扇出区的栅线间距降低至4.2μm至4.7μm,从而将布线间距从5.5μm降低了1μm左右,相比之下降低了18%左右的间距距离。通过调整基板制作过程中的掩膜板,使扇出区的掩膜板从全透改变为半透,从而在完成光刻时,半透区域对应的金属层上还会有光刻胶保留,从而保护扇出区的金属层不会进行湿法刻蚀,从而降低了栅线的CDBia

一种阵列基板、掩膜板和显示面板.pdf

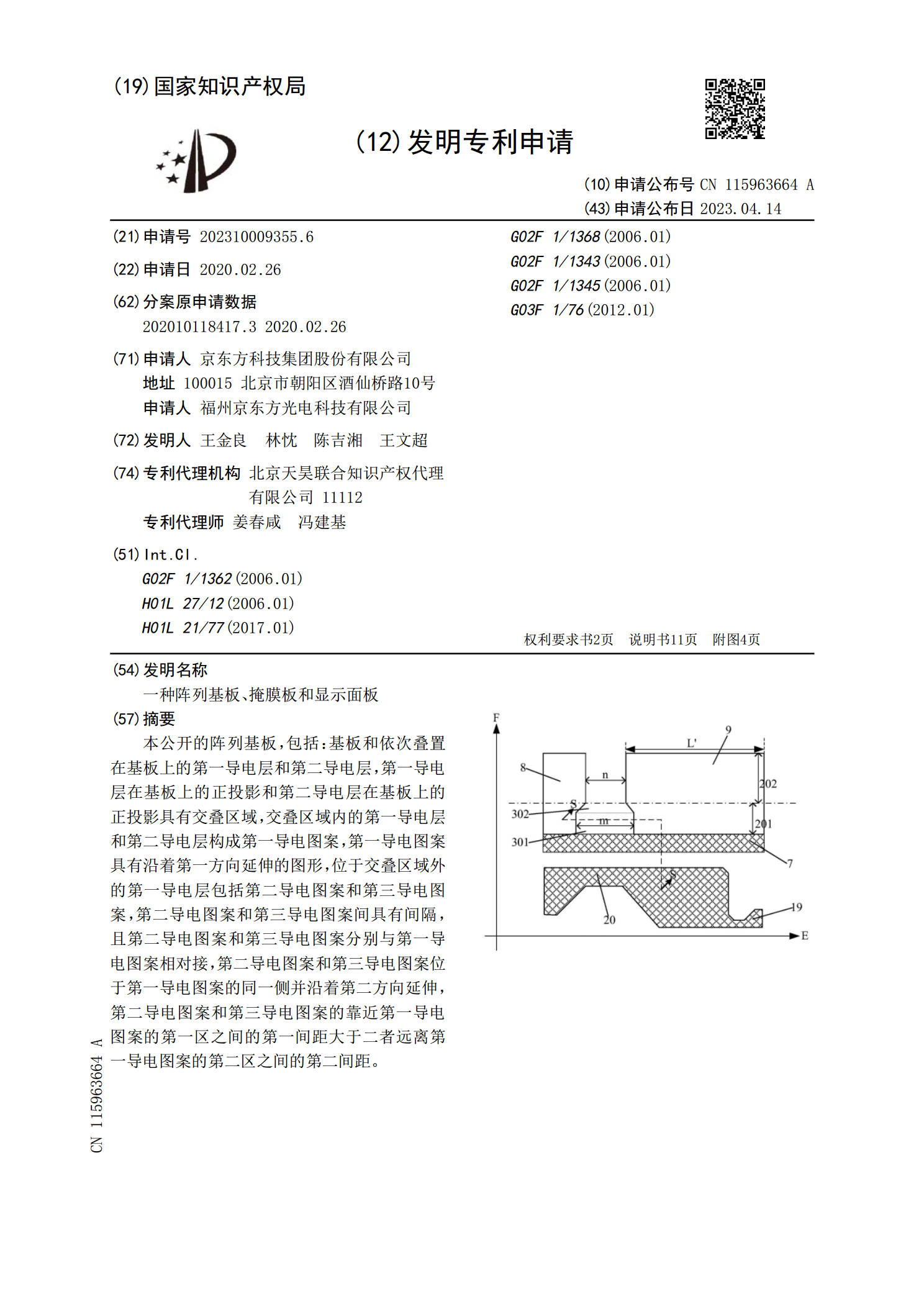

本公开的阵列基板,包括:基板和依次叠置在基板上的第一导电层和第二导电层,第一导电层在基板上的正投影和第二导电层在基板上的正投影具有交叠区域,交叠区域内的第一导电层和第二导电层构成第一导电图案,第一导电图案具有沿着第一方向延伸的图形,位于交叠区域外的第一导电层包括第二导电图案和第三导电图案,第二导电图案和第三导电图案间具有间隔,且第二导电图案和第三导电图案分别与第一导电图案相对接,第二导电图案和第三导电图案位于第一导电图案的同一侧并沿着第二方向延伸,第二导电图案和第三导电图案的靠近第一导电图案的第一区之间的

阵列基板、显示面板及阵列基板的制作方法.pdf

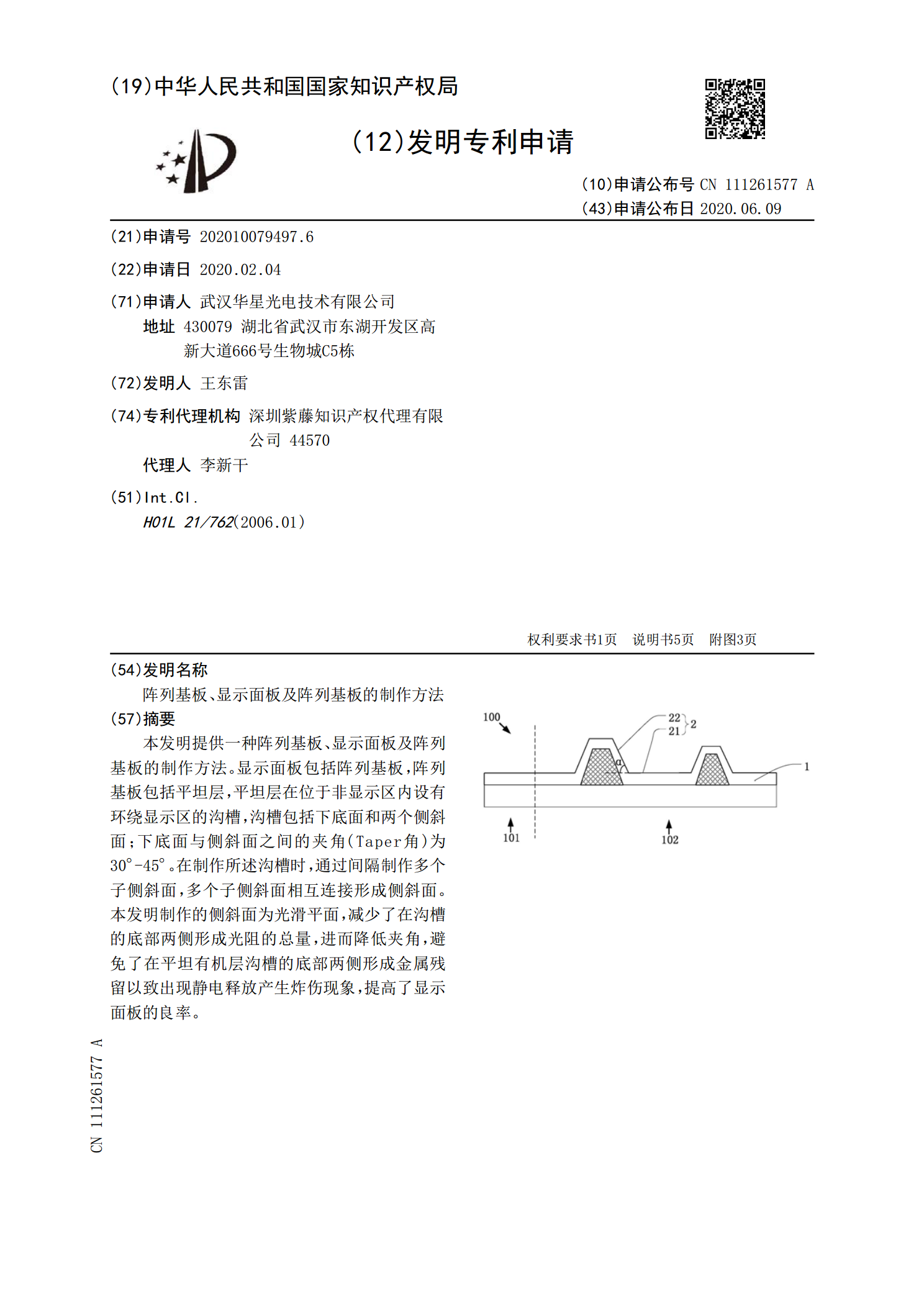

本发明提供一种阵列基板、显示面板及阵列基板的制作方法。显示面板包括阵列基板,阵列基板包括平坦层,平坦层在位于非显示区内设有环绕显示区的沟槽,沟槽包括下底面和两个侧斜面;下底面与侧斜面之间的夹角(Taper角)为30°‑45°。在制作所述沟槽时,通过间隔制作多个子侧斜面,多个子侧斜面相互连接形成侧斜面。本发明制作的侧斜面为光滑平面,减少了在沟槽的底部两侧形成光阻的总量,进而降低夹角,避免了在平坦有机层沟槽的底部两侧形成金属残留以致出现静电释放产生炸伤现象,提高了显示面板的良率。