集成电路系统及其形成方法及用于形成存储器阵列的方法.pdf

一吃****仕龙

亲,该文档总共21页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

集成电路系统及其形成方法及用于形成存储器阵列的方法.pdf

本申请涉及一种集成电路系统及其形成方法及用于形成存储器阵列的方法。一种用于形成集成电路系统的方法包括形成包括竖直交替的第一层和第二层的堆叠。所述第一层包括掺杂二氧化硅,且所述第二层包括未掺杂二氧化硅。将水平拉长的沟槽形成到所述堆叠中。穿过所述沟槽相对于所述第二层中的所述未掺杂二氧化硅选择性地蚀刻所述第一层中的所述掺杂二氧化硅。传导材料形成于所述第一层中通过所述蚀刻而留下的空隙空间中。公开了独立于方法的结构。

集成电路系统、包括存储器单元串的存储器阵列、用于形成集成电路系统的方法和用于形成包括存储器单元串的存储器阵列的方法.pdf

本发明涉及一种用于形成集成电路系统的方法,其包括形成包括竖直交替的第一阶层和第二阶层的堆叠。所述堆叠在其中包括腔,所述腔包括阶梯结构。用绝缘体材料对所述腔的侧壁和所述阶梯结构的梯级进行加衬。在所述腔中从所述绝缘体材料径向地向内形成绝缘性材料。从所述腔移除所述绝缘性材料的上部部分以在所述腔的底部中在所述阶梯结构之上留下所述绝缘性材料。在所述移除之后,在所述腔中在所述绝缘性材料上方形成绝缘材料。公开了其它实施例,包含独立于方法的结构。

集成电路、集成电路系统的构造及形成阵列的方法.pdf

一种形成阵列的方法,其包括使用两种不同成分遮蔽材料形成具有彼此基本上相同的大小且彼此基本上相同的形状的间隔重复第一特征的图案。具有相较于所述第一特征的大小或形状不同的大小或不同的形状中的至少一者的图案中断第二特征在所述第一特征图案内且中断所述第一特征的图案。将所述第一特征的所述图案与所述图案中断第二特征平移到所述第一特征及所述图案中断第二特征下方的下衬底材料中。在所述平移期间或在所述平移之后中的至少一者移除所述下衬底材料上方的所述第一特征及所述图案中断第二特征的材料。在所述移除之后,使用所述下衬底材料中的

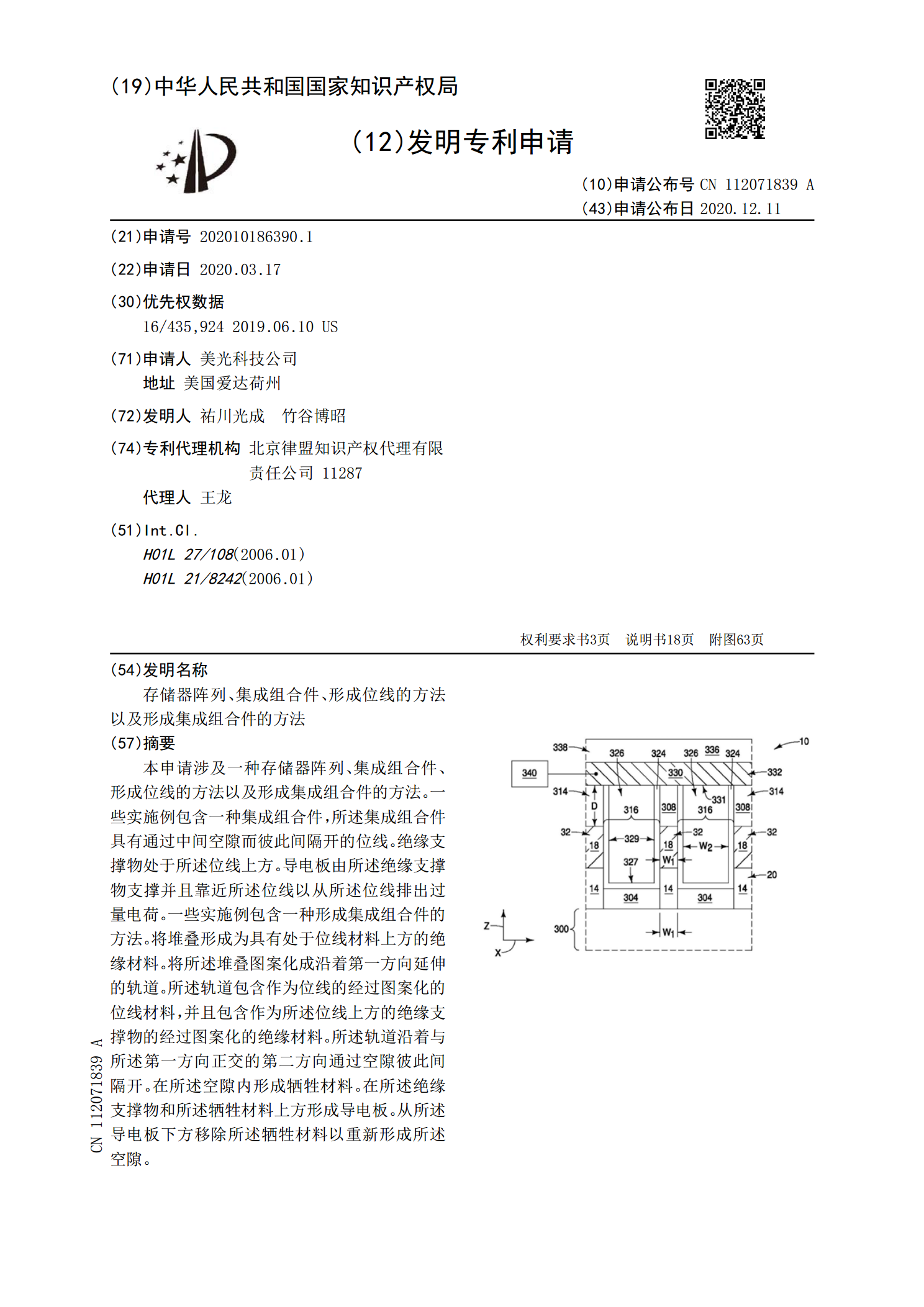

存储器阵列、集成组合件、形成位线的方法以及形成集成组合件的方法.pdf

本申请涉及一种存储器阵列、集成组合件、形成位线的方法以及形成集成组合件的方法。一些实施例包含一种集成组合件,所述集成组合件具有通过中间空隙而彼此间隔开的位线。绝缘支撑物处于所述位线上方。导电板由所述绝缘支撑物支撑并且靠近所述位线以从所述位线排出过量电荷。一些实施例包含一种形成集成组合件的方法。将堆叠形成为具有处于位线材料上方的绝缘材料。将所述堆叠图案化成沿着第一方向延伸的轨道。所述轨道包含作为位线的经过图案化的位线材料,并且包含作为所述位线上方的绝缘支撑物的经过图案化的绝缘材料。所述轨道沿着与所述第一方向

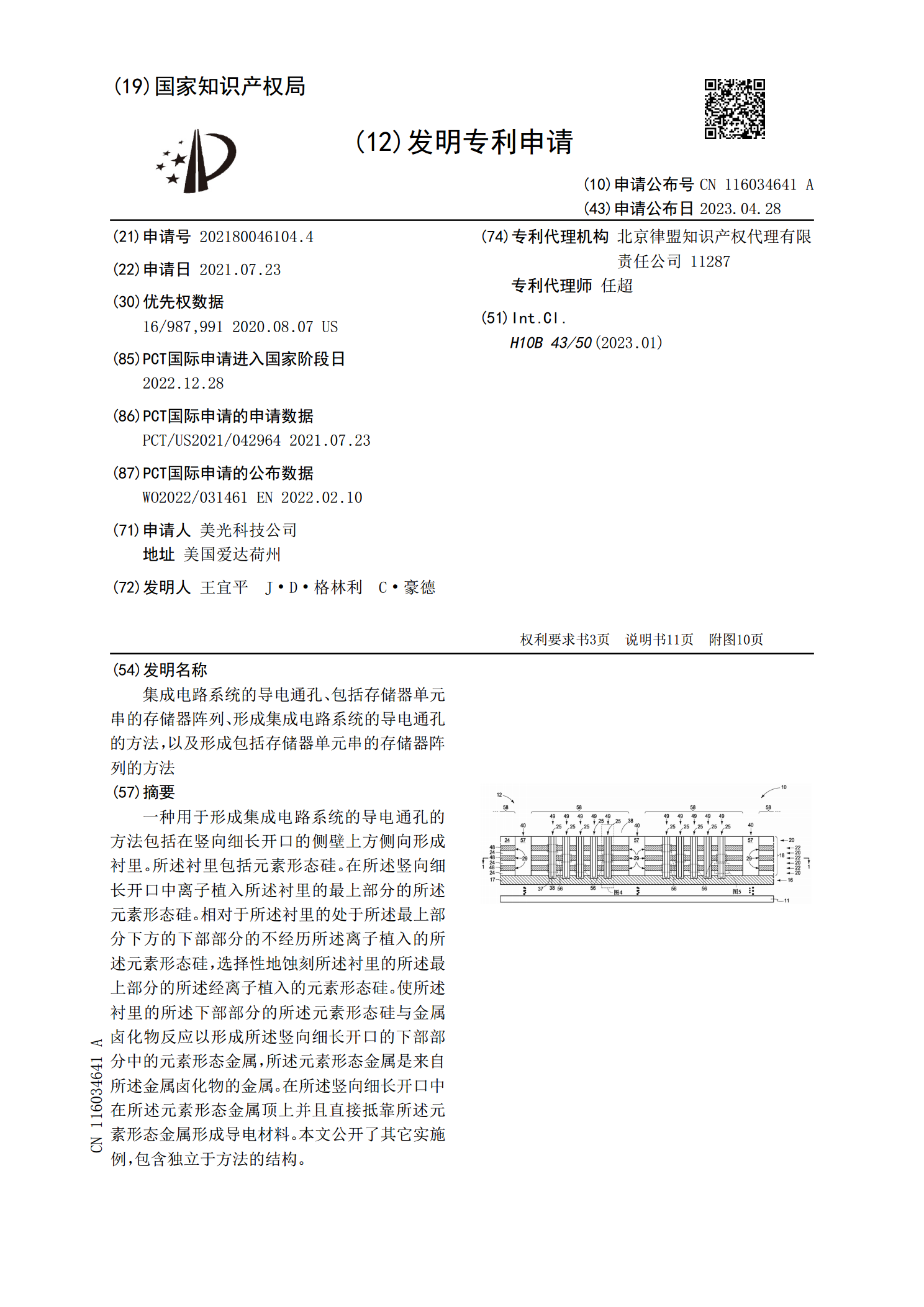

集成电路系统的导电通孔、包括存储器单元串的存储器阵列、形成集成电路系统的导电通孔的方法,以及形成包括存储器单元串的存储器.pdf

一种用于形成集成电路系统的导电通孔的方法包括在竖向细长开口的侧壁上方侧向形成衬里。所述衬里包括元素形态硅。在所述竖向细长开口中离子植入所述衬里的最上部分的所述元素形态硅。相对于所述衬里的处于所述最上部分下方的下部部分的不经历所述离子植入的所述元素形态硅,选择性地蚀刻所述衬里的所述最上部分的所述经离子植入的元素形态硅。使所述衬里的所述下部部分的所述元素形态硅与金属卤化物反应以形成所述竖向细长开口的下部部分中的元素形态金属,所述元素形态金属是来自所述金属卤化物的金属。在所述竖向细长开口中在所述元素形态金属顶上