半导体封装结构.pdf

运升****魔王

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

半导体封装结构及半导体封装结构的封装方法.pdf

本发明公开了一种半导体封装结构及半导体封装结构的封装方法,该封装结构包括导线架、单层基板、金属线路层以及半导体组件。所述导线架包括主体部、多个接垫以及未接触区域的补强区。所述单层基板位于所述导线架上且部分填入所述补强区内,所述单层基板设有第一通孔及第二通孔,所述第一通孔内形成第一导电柱且电连接所述主体部,所述第二通孔内形成第二导电柱且电连接所述接垫。所述金属线路层分布于所述单层基板表面上且与对应的所述第一及第二导电柱电连接。所述半导体组件设有焊接部,所述半导体组件由所述焊接部电连接于所述金属线路层上。

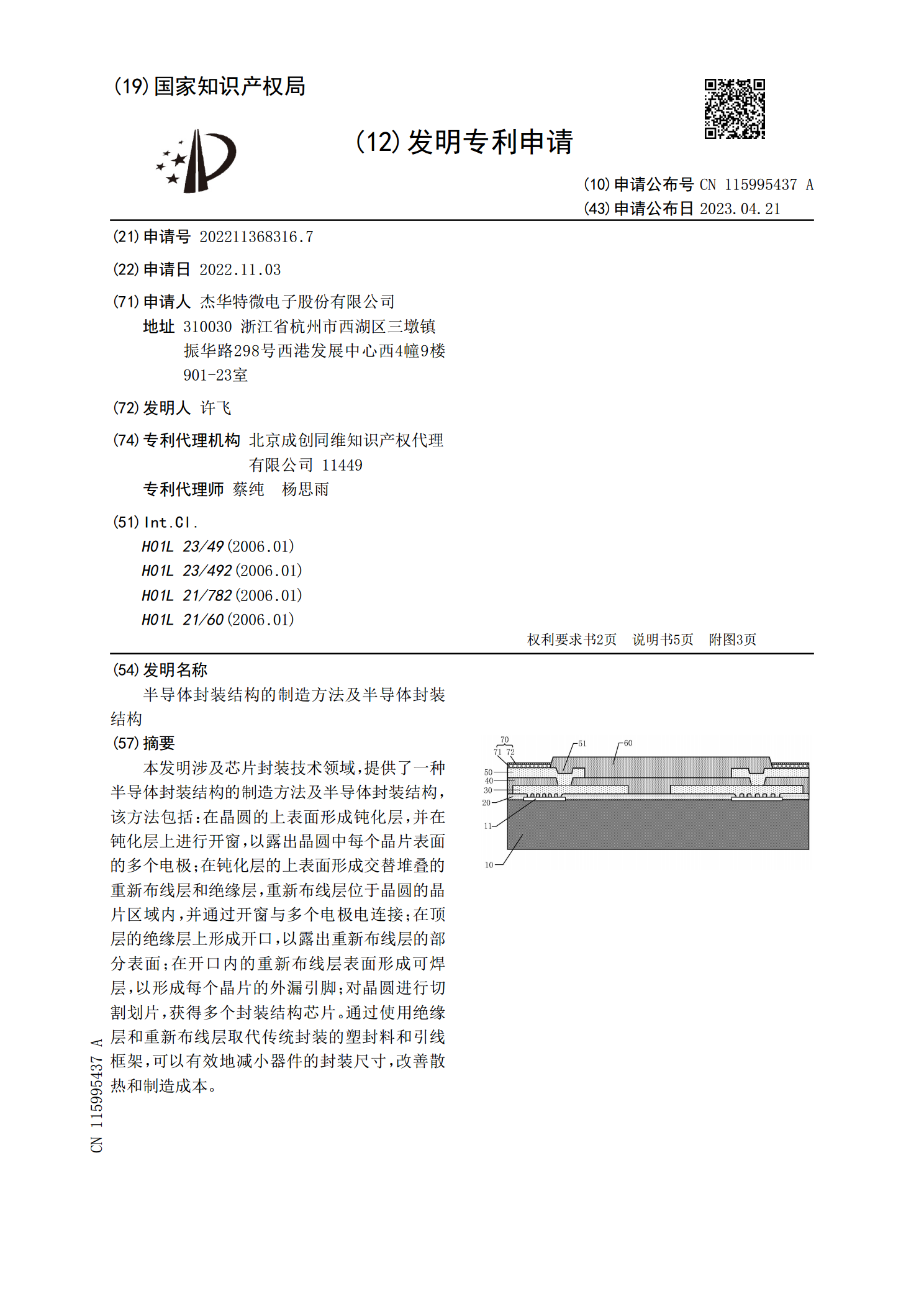

半导体封装结构的制造方法及半导体封装结构.pdf

本发明涉及芯片封装技术领域,提供了一种半导体封装结构的制造方法及半导体封装结构,该方法包括:在晶圆的上表面形成钝化层,并在钝化层上进行开窗,以露出晶圆中每个晶片表面的多个电极;在钝化层的上表面形成交替堆叠的重新布线层和绝缘层,重新布线层位于晶圆的晶片区域内,并通过开窗与多个电极电连接;在顶层的绝缘层上形成开口,以露出重新布线层的部分表面;在开口内的重新布线层表面形成可焊层,以形成每个晶片的外漏引脚;对晶圆进行切割划片,获得多个封装结构芯片。通过使用绝缘层和重新布线层取代传统封装的塑封料和引线框架,可以有效

半导体封装结构.pdf

本公开提供的半导体封装结构,在重布线层(RedistributionLayer,RDL)与基板(Substrate)之间的线路设计中,将信号线路维持保留于基板,而将电源/接地线路设计于重布线层。相较于传统扇出型基板(FOSub)结构中将部分信号线路设计于线宽比基板更小的重布线层,本公开将信号线路维持保留于线宽比重布线层更大的基板以保持高速信号布局,不会有信号传输损耗,因此可以保持信号传输的完整性。

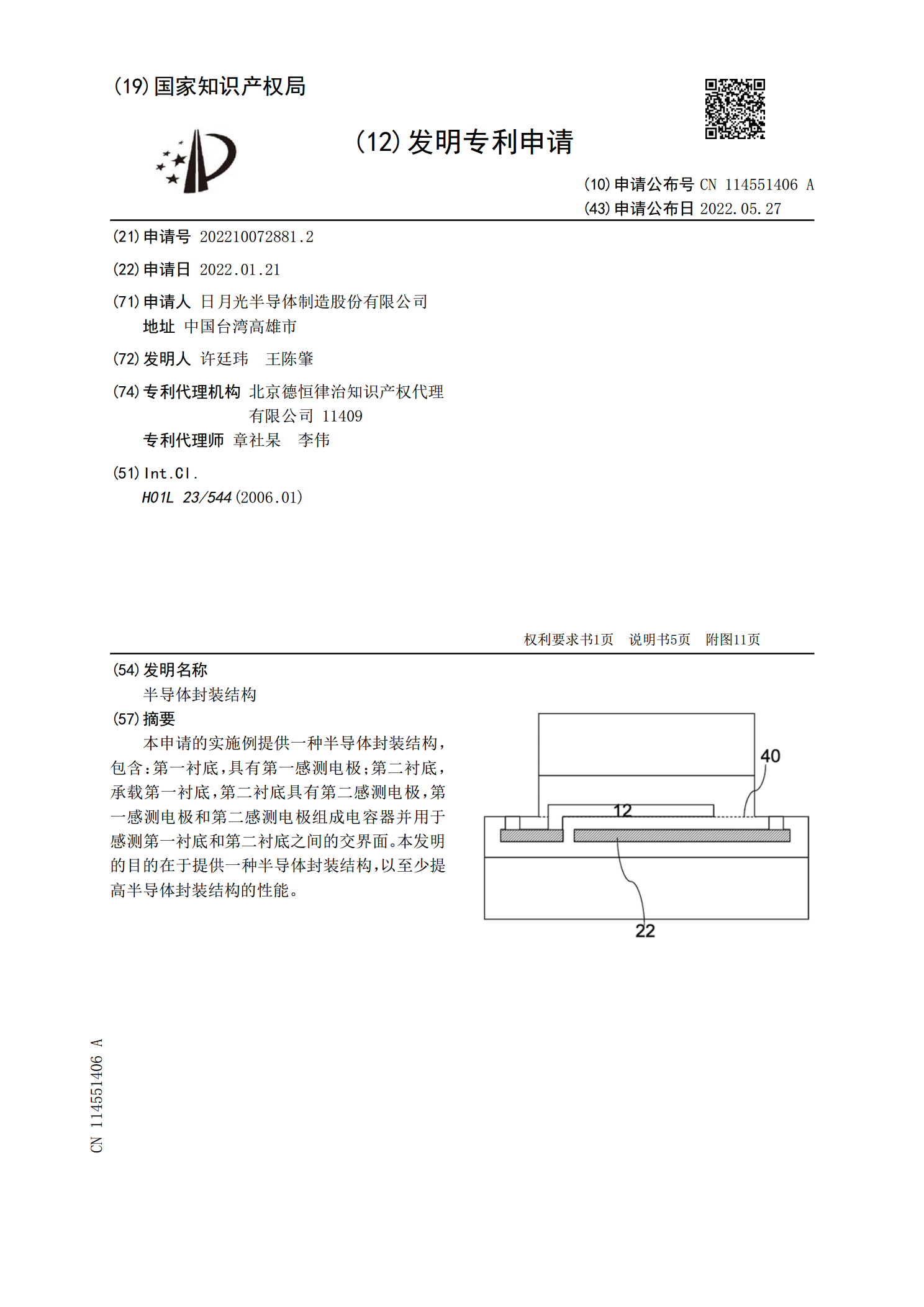

半导体封装结构.pdf

本申请的实施例提供一种半导体封装结构,包含:第一衬底,具有第一感测电极;第二衬底,承载第一衬底,第二衬底具有第二感测电极,第一感测电极和第二感测电极组成电容器并用于感测第一衬底和第二衬底之间的交界面。本发明的目的在于提供一种半导体封装结构,以至少提高半导体封装结构的性能。

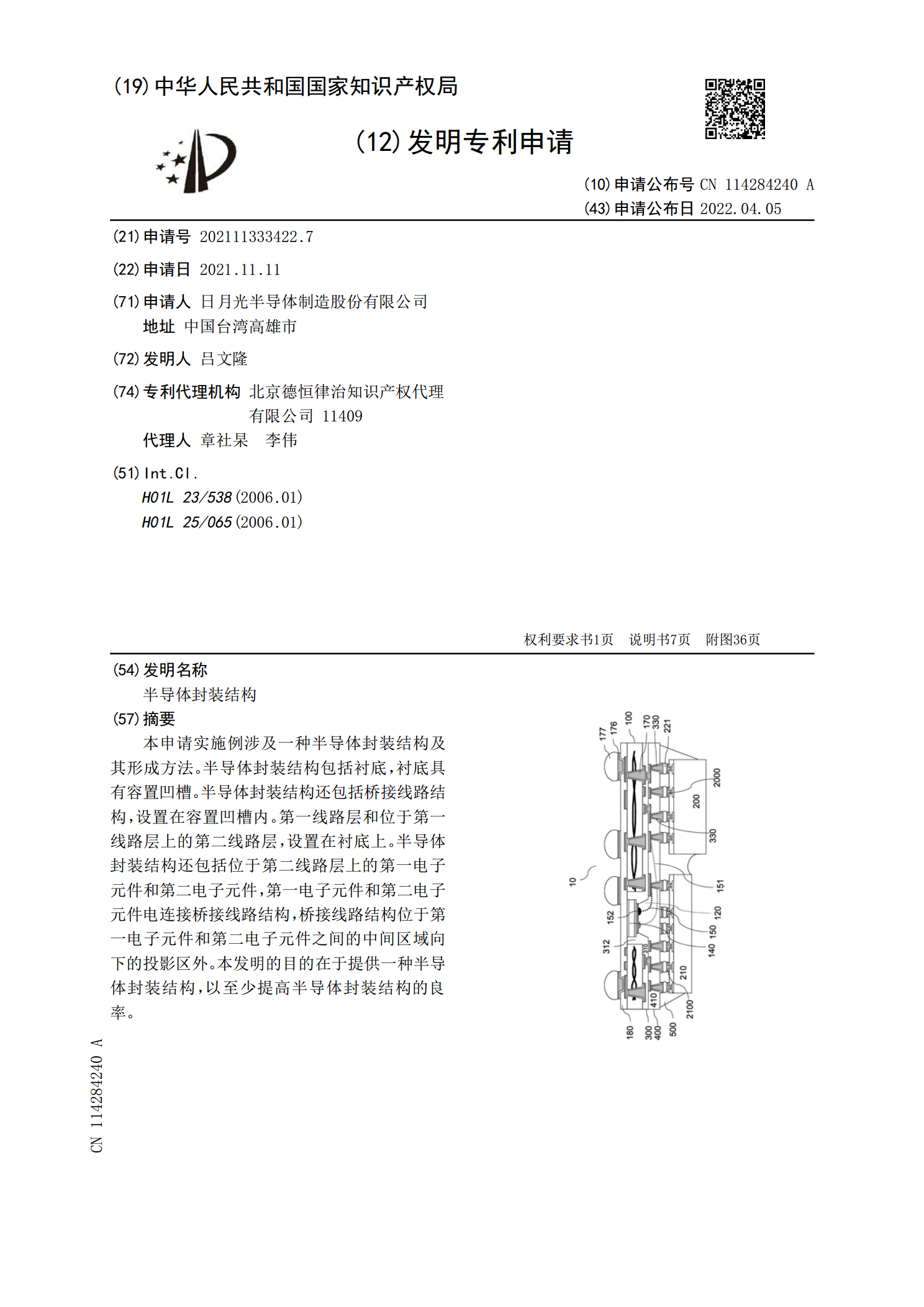

半导体封装结构.pdf

本申请实施例涉及一种半导体封装结构及其形成方法。半导体封装结构包括衬底,衬底具有容置凹槽。半导体封装结构还包括桥接线路结构,设置在容置凹槽内。第一线路层和位于第一线路层上的第二线路层,设置在衬底上。半导体封装结构还包括位于第二线路层上的第一电子元件和第二电子元件,第一电子元件和第二电子元件电连接桥接线路结构,桥接线路结构位于第一电子元件和第二电子元件之间的中间区域向下的投影区外。本发明的目的在于提供一种半导体封装结构,以至少提高半导体封装结构的良率。