半导体器件工艺方法.pdf

元枫****文章

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

半导体器件工艺方法.pdf

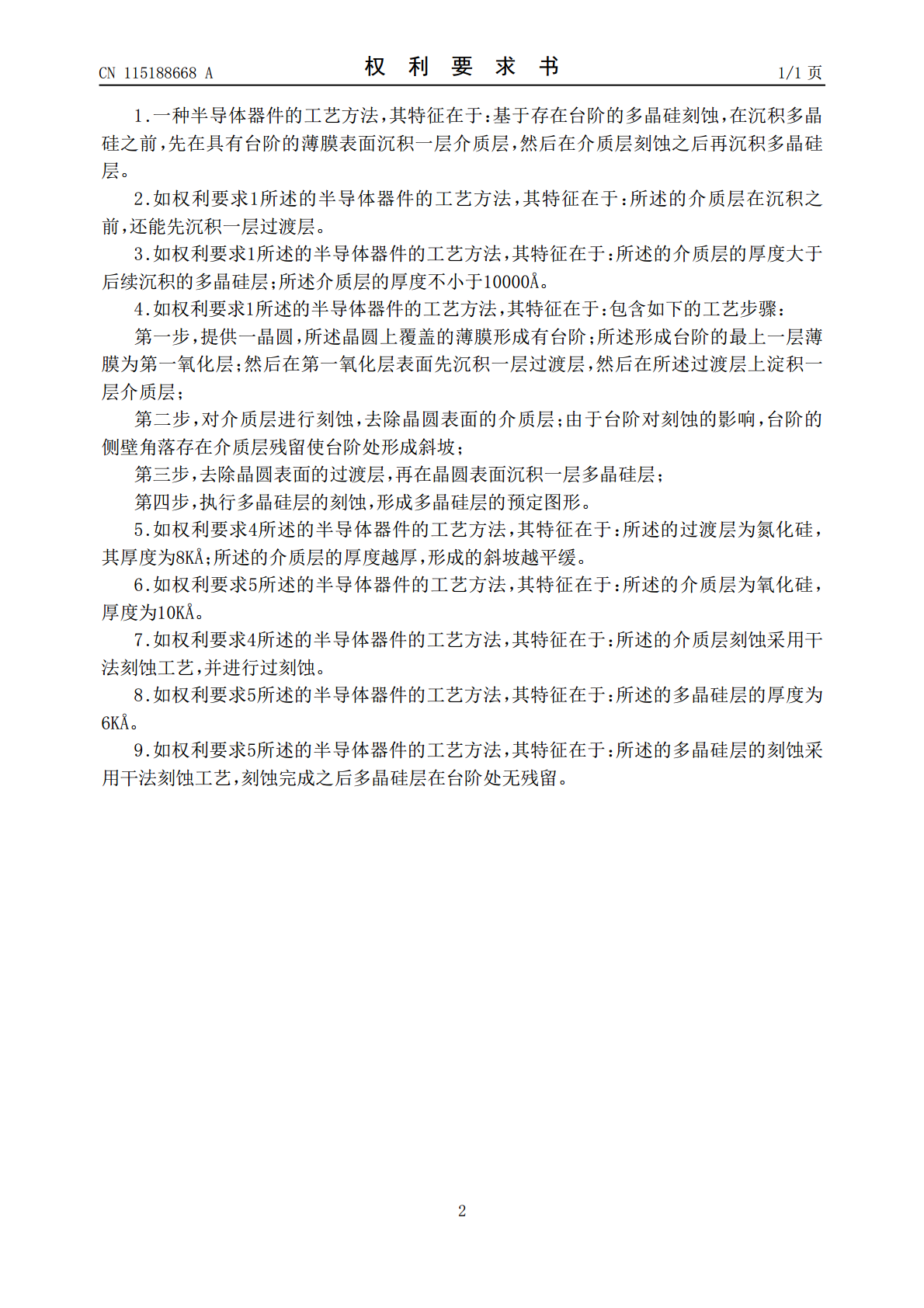

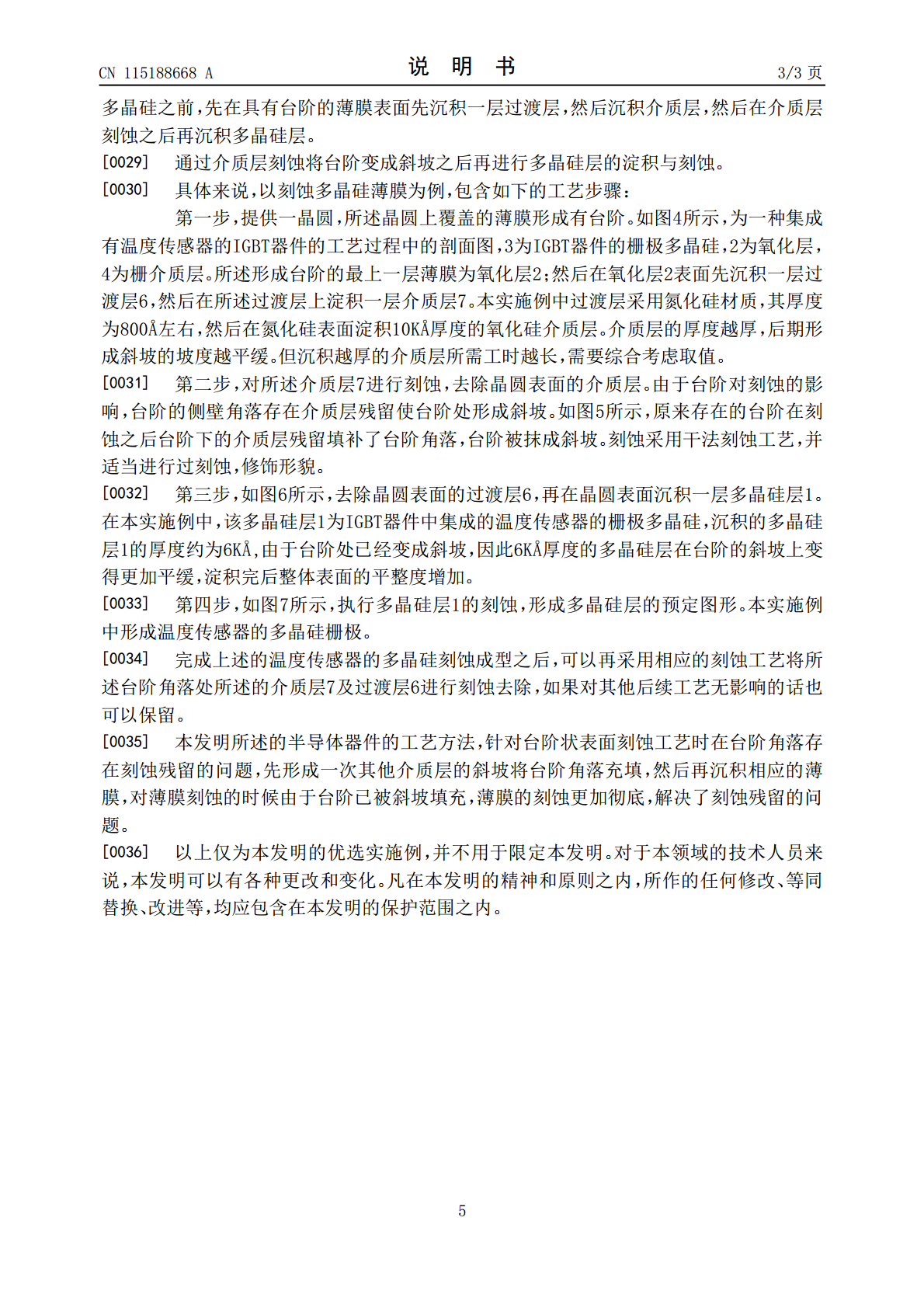

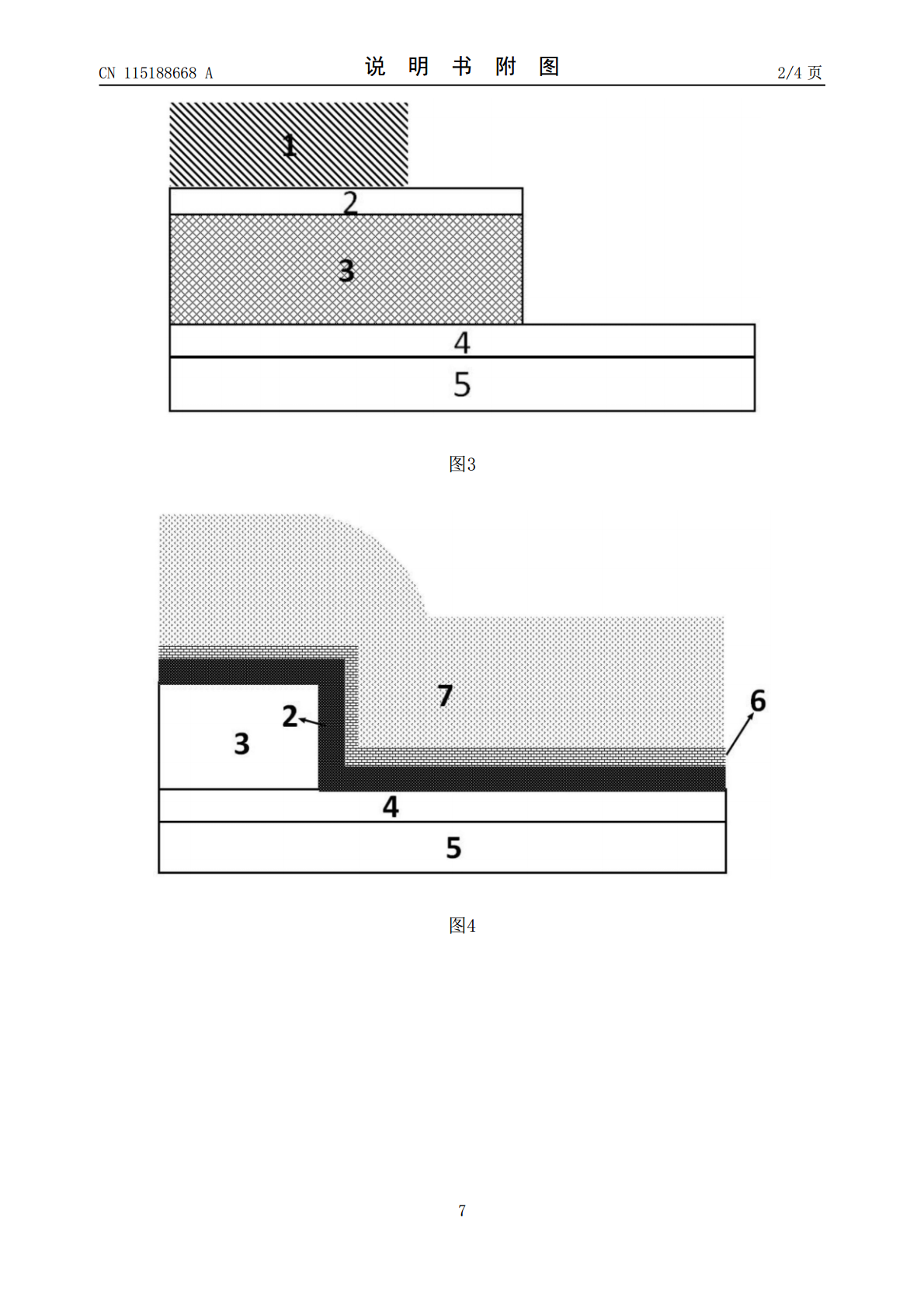

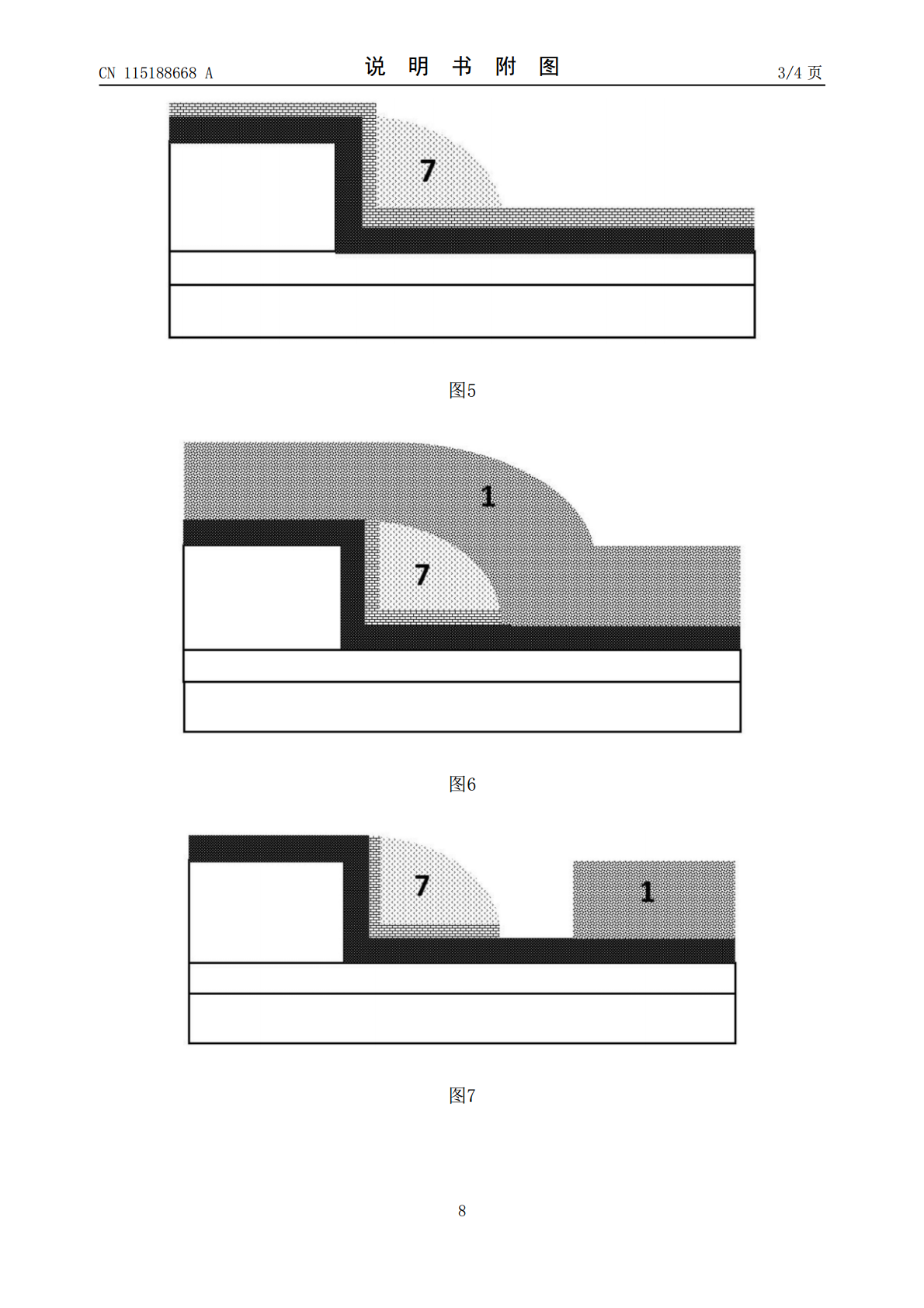

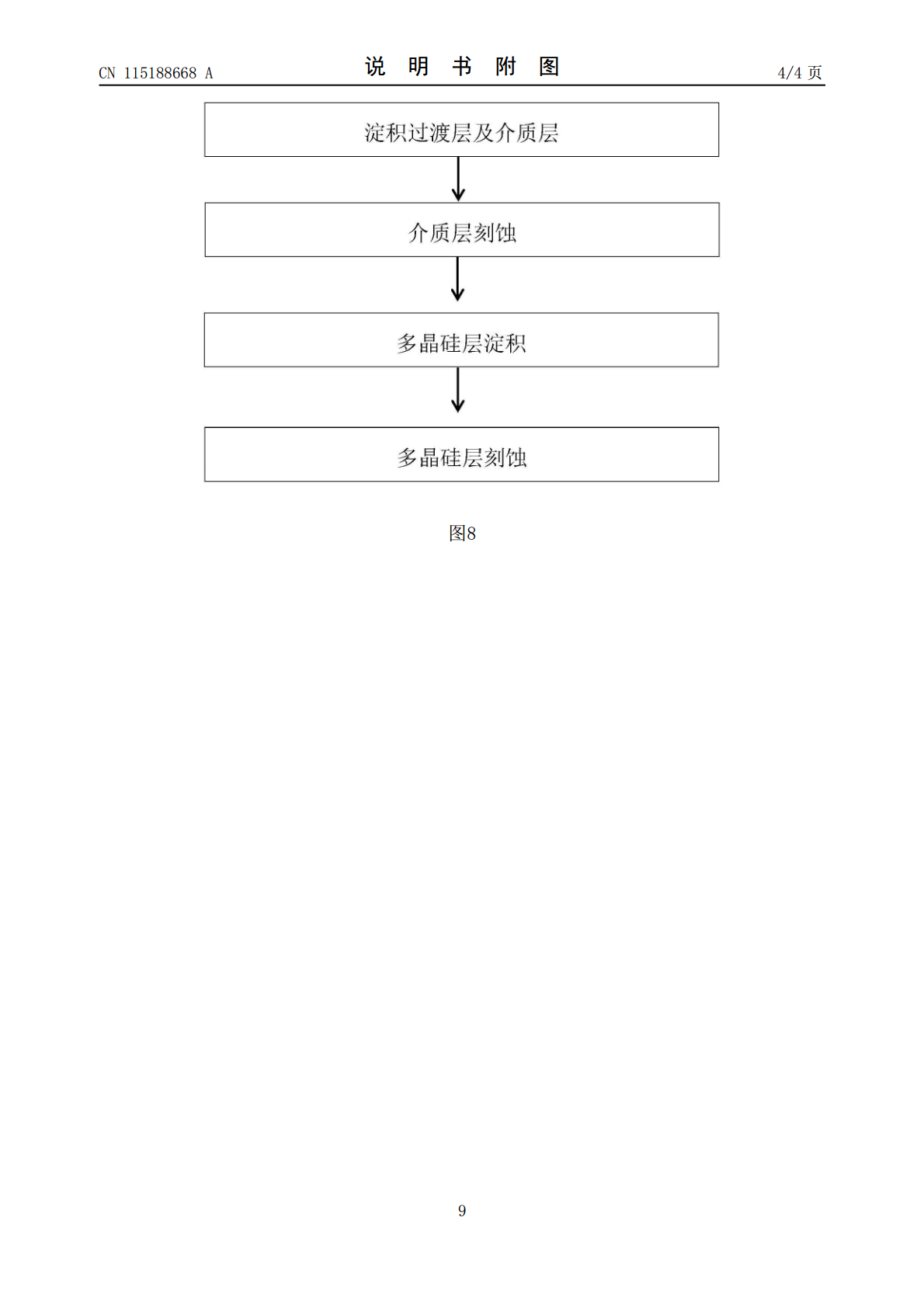

本发明公开了一种半导体器件的工艺方法,基于存在台阶的多晶硅刻蚀,在沉积多晶硅之前,先在具有台阶的薄膜表面沉积一层介质层,然后在介质层刻蚀之后再沉积多晶硅层。本发明所述的半导体器件的工艺方法,针对台阶状表面刻蚀工艺时在台阶角落存在刻蚀残留的问题,先形成一次其他介质层的斜坡将台阶角落充填,然后再沉积相应的薄膜,对薄膜刻蚀的时候由于台阶已被斜坡填充,薄膜的刻蚀更加彻底,解决了刻蚀残留的问题。

半导体器件和使用多个CMP工艺制造半导体器件的方法.pdf

本公开涉及半导体器件和使用多个CMP工艺制造半导体器件的方法。一种制造半导体器件的方法,所述方法包括在器件晶片的背侧表面上执行一个或多个研磨工艺,以将所述器件晶片从第一厚度减薄到第二厚度。在所述器件晶片的所述背侧表面上执行第一化学机械抛光(CMP)工艺,以将所述器件晶片从所述第二厚度减薄到第三厚度。在所述器件晶片的所述背侧表面上执行第二CMP工艺,以选择性地去除设置在所述半导体器件的有源器件区域上方的器件晶片材料,其中所述器件晶片材料的去除速率是深度的函数。

光波导半导体器件的工艺方法.pdf

本发明公开了一种光波导半导体器件的工艺方法,包含步骤:第1步,在硅衬底上淀积第一介质膜层;第2步,在第一介质膜层之上利用光刻胶定义出图形;第3步,对第一介质膜层进行刻蚀之后,去除光刻胶;第4步,淀积热氧化层,然后进行化学机械研磨;第5步,淀积第二介质膜层;第6步,在第二介质膜层之上利用光刻胶定义出光刻对准标记区域;第7步,在光刻对准标记区域完成光刻对准标记的制作;第8步,对第二介质膜层进行刻蚀;第9步,重复上述步骤进行介质膜层的反复淀积,最终完成光波导半导体器件的制作。本发明工艺避免因介质膜层沉积造成的光

半导体器件半导体工艺掺杂.pptx

掺杂工艺目的扩散扩散形成的掺杂区和结扩散工艺步骤扩散方式淀积工艺受控制或约束的因素淀积工艺受控制或约束的因素扩散源扩散源扩散源2、推进氧化drive-in-oxidation氧化的影响离子注入离子注入概念离子注入系统离子注入系统离子注入系统束流聚焦:离开加速管后,束流由于相同电荷的排斥作用而发散。发散导致离子密度不均匀和晶体掺杂不均一。成功的离子注入,束流必须聚焦。静电或磁透镜用于将离子束聚焦为小尺寸束流或平行束流。束流中和:尽管真空去除了系统中大部分空气,但是束流附近还是有些残存的气体分子。离子和这些气

半导体器件原理与工艺(器件)1.ppt

半导体器件微电子学研究领域半导体中的缺陷电子:带负电的导电载流子是价电子脱离原子束缚后形成的自由电子对应于导带中占据的电子空穴:带正电的导电载流子是价电子脱离原子束缚后形成的电子空位对应于价带中的电子空位半导体、绝缘体和导体半导体器件突变结耗尽区的电场与电势分布电场分布电势分布耗尽层宽度耗尽层宽度VA0条件下的突变结反偏PN结线性缓变结定量方程耗尽层边界(续)准中性区载流子浓度理想二极管方程理想二极管方程(1)电子电流PN结电流空间电荷区的产生与复合空间电荷区的产生与复合-1VA