一种沟槽型SiC MOSFET器件结构及其制造方法.pdf

Do****76

亲,该文档总共18页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种沟槽型SiC MOSFET器件结构及其制造方法.pdf

本申请公开了一种沟槽型SiCMOSFET器件结构及其制造方法,该方法包括:在SiC衬底上生长SiC外延层;在SiC外延层形成体区;对体区进行源注入,形成源极;在体区内通过刻蚀形成栅沟槽;沉积形成第一介电层和第二介电层,第一介电层覆盖于栅沟槽的第一侧壁、第二侧壁以及底部,第二介电层填充于栅沟槽的第一侧壁和第二侧壁之间的中空区域;去除部分覆盖于第一侧壁的第一介电层,并至少保留覆盖于栅沟槽底部的第一介电层,形成空置区域;在露出于空置区域的第一侧壁表面生长栅氧化层;于栅氧化层和第二介电层之间填充填充物,形成栅极

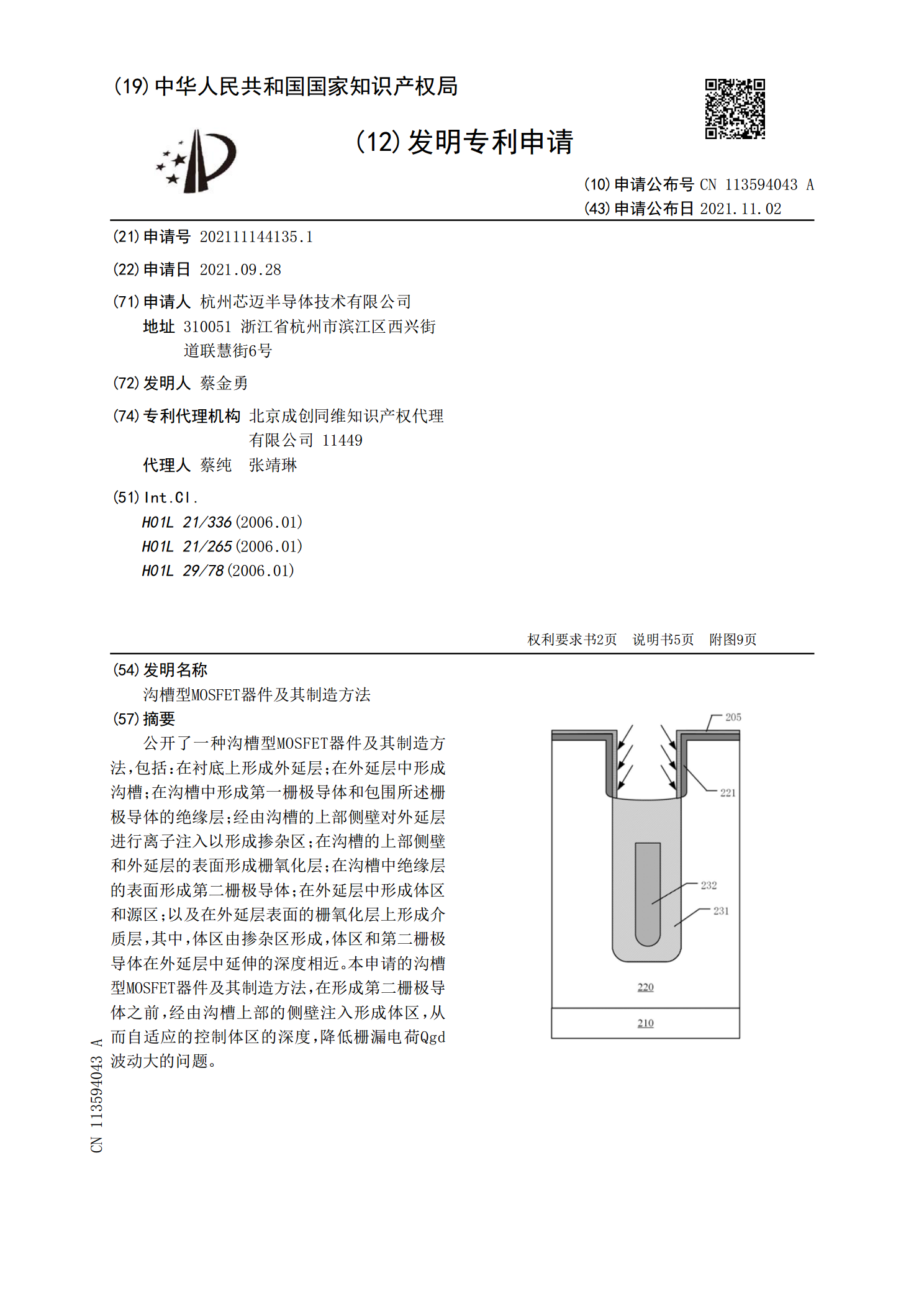

沟槽型MOSFET器件及其制造方法.pdf

公开了一种沟槽型MOSFET器件及其制造方法,包括:在衬底上形成外延层;在外延层中形成沟槽;在沟槽中形成第一栅极导体和包围所述栅极导体的绝缘层;经由沟槽的上部侧壁对外延层进行离子注入以形成掺杂区;在沟槽的上部侧壁和外延层的表面形成栅氧化层;在沟槽中绝缘层的表面形成第二栅极导体;在外延层中形成体区和源区;以及在外延层表面的栅氧化层上形成介质层,其中,体区由掺杂区形成,体区和第二栅极导体在外延层中延伸的深度相近。本申请的沟槽型MOSFET器件及其制造方法,在形成第二栅极导体之前,经由沟槽上部的侧壁注入形成体区

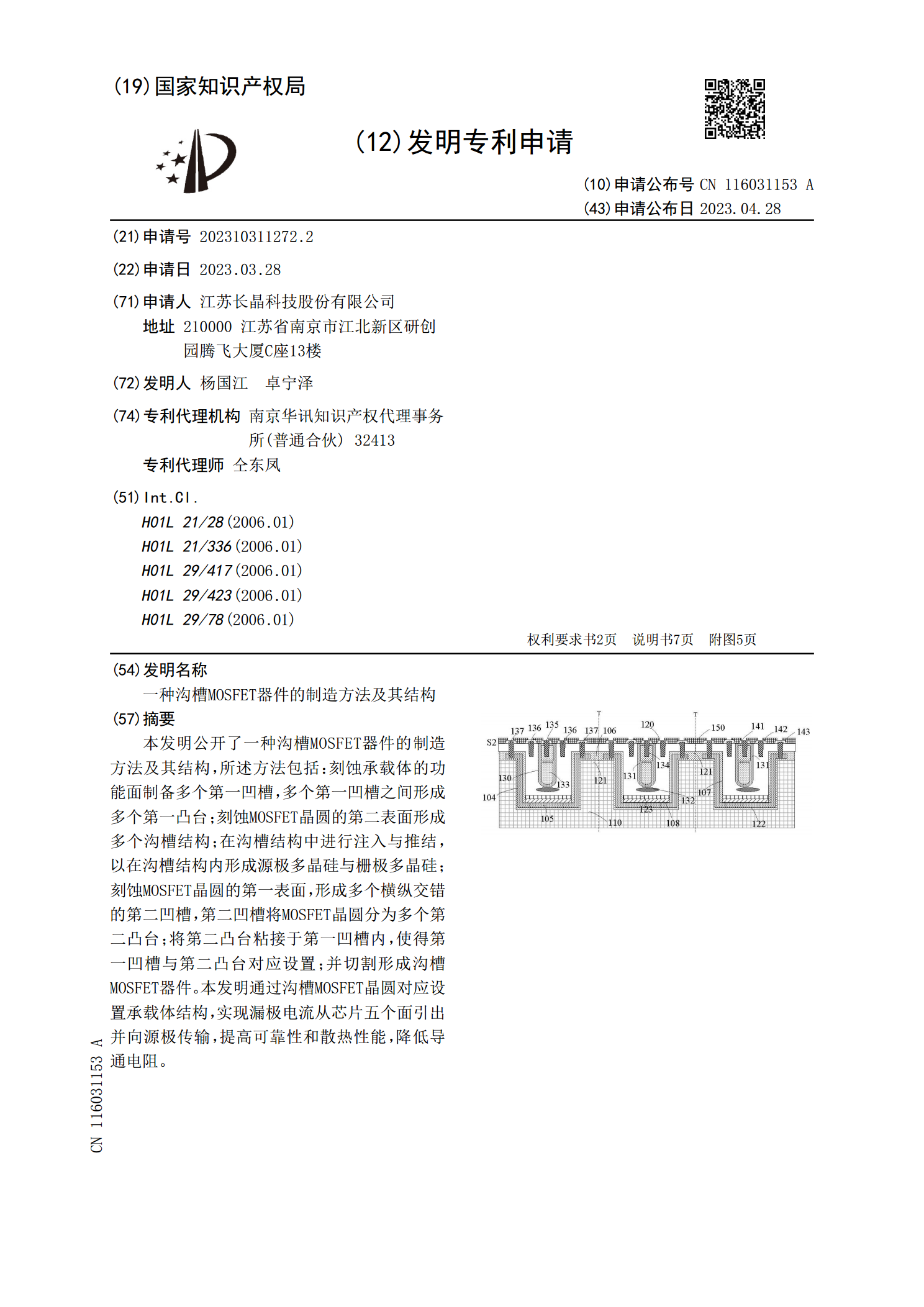

一种沟槽MOSFET器件的制造方法及其结构.pdf

(19)国家知识产权局(12)发明专利申请(10)申请公布号CN116031153A(43)申请公布日2023.04.28(21)申请号202310311272.2(22)申请日2023.03.28(71)申请人江苏长晶科技股份有限公司地址210000江苏省南京市江北新区研创园腾飞大厦C座13楼(72)发明人杨国江卓宁泽(74)专利代理机构南京华讯知识产权代理事务所(普通合伙)32413专利代理师仝东凤(51)Int.Cl.H01L21/28(2006.01)H01L21/336(2006.01)H01L

沟槽型MOSFET结构及其制造方法.pdf

公开了一种制造沟槽MOSFET的方法。包括:在半导体基底中形成从上表面延伸至其内部的沟槽;形成覆盖所述沟槽的侧壁、所述沟槽的底部以及所述半导体基底的上表面的第一绝缘层;在所述沟槽中形成覆盖所述沟槽的底部和下部侧壁的屏蔽导体,所述第一绝缘层将所述屏蔽导体与所述半导体基底隔开;形成覆盖所述屏蔽导体顶部的第二绝缘层,所述第一绝缘层和所述第二绝缘层共形形成介质层;去除位于所述半导体基底的上表面的介质层和位于所述沟槽上部侧壁的介质层,使得保留的所述介质层的上表面高于所述屏蔽导体的上表面。本发明简化现有技术中形成沟槽

沟槽型功率器件的沟槽栅结构及其制造方法.pdf

一种沟槽型功率器件的沟槽栅结构及其制造方法,在半导体基底的沟槽内底部的设有厚氧化层,沟槽侧壁形成沟槽型功率器件的栅氧化层,及在沟槽内沉积形成一个塞状多晶硅栅极,且在厚氧化层上方及多晶硅栅极下方设有第一限制部,及包覆第一限制部的第二限制部。透过第一限制部及第二限制部的存在,在后续工序中将保留第二限制部下方的厚氧化层,从而能降低工艺成本;能在更小深宽比的沟槽中形成良好的TBO(ThickBottomOxide),从而能适用于各种深宽比的沟槽的TBO形成,从而具有较大的使用范围。