半导体芯片的制造方法及半导体芯片.pdf

努力****妙风

亲,该文档总共19页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体芯片的制造方法及半导体芯片.pdf

本发明公开了半导体芯片的制造方法,包括如下步骤:在半导体基片上生长硬掩模介质层,所述半导体基片包括浓掺杂的衬底和轻掺杂的外延层,衬底和外延层的掺杂类型为N型;以硬掩模介质层为阻挡层,采用光刻、刻蚀工艺,在半导体基片上形成沟槽;去除所述硬掩模介质层,生长第一氧化硅、氮化硅以及第二氧化硅;采用化学机械研磨工艺,去除高出所述氮化硅上表面的第二氧化硅,保留所述沟槽中的第二氧化硅;采用离子注入、退火工艺,在所述外延层之中形成第一P型掺杂区和第二P型掺杂区;本发明提供半导体芯片,本发明公开的半导体芯片的制造方法及半导

一种半导体芯片的制造方法及半导体芯片.pdf

本发明公开了一种半导体芯片的制造方法,包括如下步骤:在半导体基片上生长硬掩模介质层,所述半导体基片包括浓掺杂的衬底和轻掺杂的外延层,衬底和外延层的掺杂类型为N型;以硬掩模介质层为阻挡层,采用光刻、刻蚀工艺,在半导体基片上形成沟槽;去除所述硬掩模介质层,生长第一氧化硅、氮化硅以及第二氧化硅;采用化学机械研磨工艺,去除高出所述氮化硅上表面的第二氧化硅,保留所述沟槽中的第二氧化硅;采用离子注入、退火工艺,在所述外延层之中形成第一P型掺杂区;采用腐蚀工艺,去除所述沟槽中的部分第二氧化硅;本发明提供一种半导体芯片,

半导体芯片及其制造方法.pdf

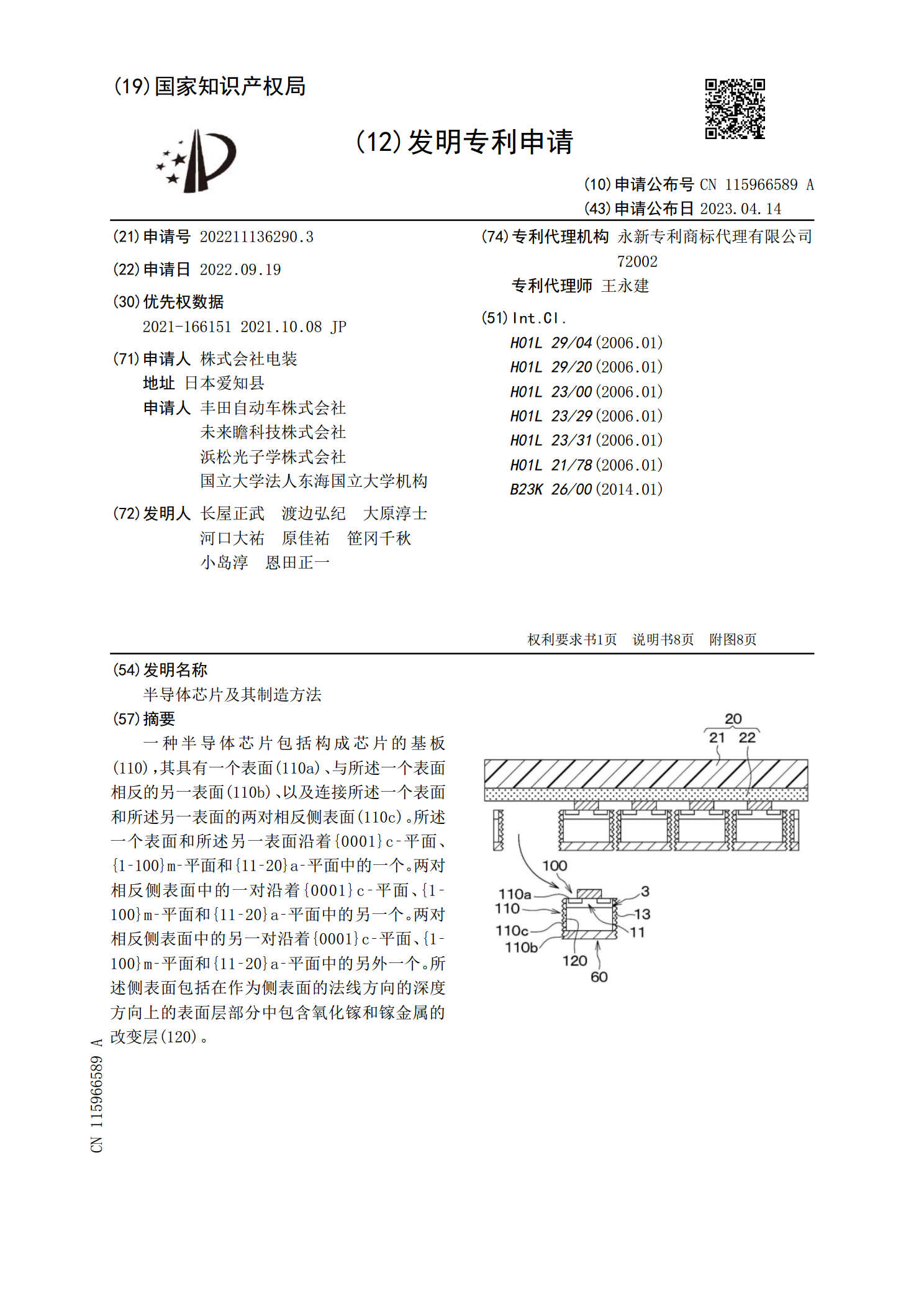

一种半导体芯片包括构成芯片的基板(110),其具有一个表面(110a)、与所述一个表面相反的另一表面(110b)、以及连接所述一个表面和所述另一表面的两对相反侧表面(110c)。所述一个表面和所述另一表面沿着{0001}c‑平面、{1‑100}m‑平面和{11‑20}a‑平面中的一个。两对相反侧表面中的一对沿着{0001}c‑平面、{1‑100}m‑平面和{11‑20}a‑平面中的另一个。两对相反侧表面中的另一对沿着{0001}c‑平面、{1‑100}m‑平面和{11‑20}a‑平面中的另外一个。所述侧表

半导体芯片的制造方法.pdf

本发明提供一种半导体芯片的制造方法,其用于处理包含晶圆测试垫的晶圆,晶圆测试垫位于切割道,该半导体芯片的制造方法以切割刀具沿着切割道切割该晶圆,于切割刀具切割该晶圆的过程中,添加一测试垫去除材料于该切割刀具与该晶圆之间,使该测试垫去除材料去除该晶圆测试垫,避免该晶圆测试垫于切割后残留形成毛边。

制造半导体芯片的方法.pdf

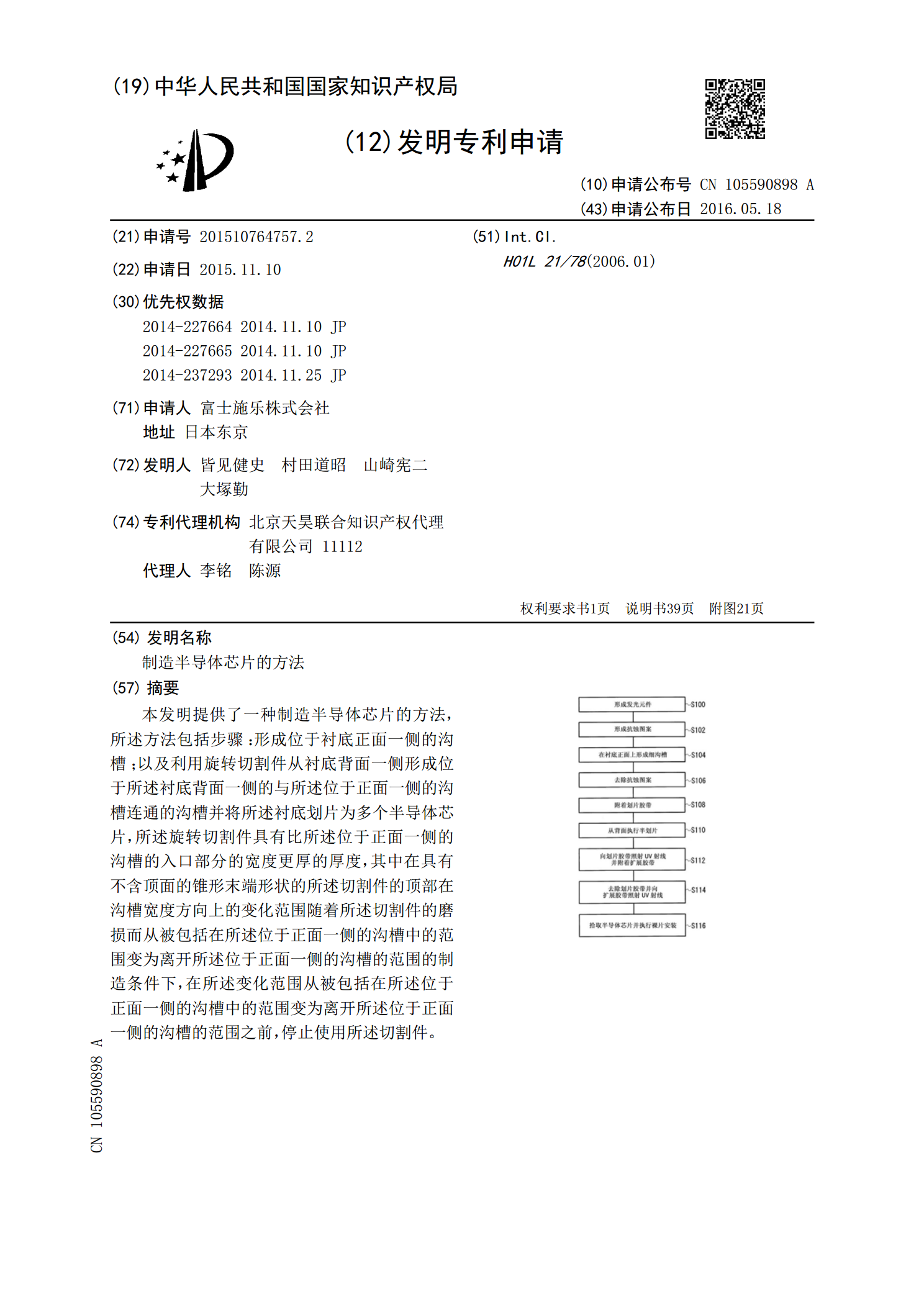

本发明提供了一种制造半导体芯片的方法,所述方法包括步骤:形成位于衬底正面一侧的沟槽;以及利用旋转切割件从衬底背面一侧形成位于所述衬底背面一侧的与所述位于正面一侧的沟槽连通的沟槽并将所述衬底划片为多个半导体芯片,所述旋转切割件具有比所述位于正面一侧的沟槽的入口部分的宽度更厚的厚度,其中在具有不含顶面的锥形末端形状的所述切割件的顶部在沟槽宽度方向上的变化范围随着所述切割件的磨损而从被包括在所述位于正面一侧的沟槽中的范围变为离开所述位于正面一侧的沟槽的范围的制造条件下,在所述变化范围从被包括在所述位于正面一侧的