一种新型屏蔽栅功率MOS的器件.pdf

一只****爱敏

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种新型屏蔽栅功率MOS的器件.pdf

本发明提出的一种新型屏蔽栅功率MOS器件,采用不掺杂多晶硅屏蔽栅,该屏蔽栅电位浮空不与源极相连,且栅极与屏蔽栅间无层间氧化层。本发明提出的浮空不掺杂多晶硅屏蔽栅结构,在保持与传统屏蔽栅结构相似的低的密勒电容的同时,显著提高器件的击穿电压,降低正向导通电阻,显著降低了栅源电容,即减小了器件的输入电容。此外由于重掺杂多晶硅栅极和不掺杂多晶硅屏蔽栅之间无层间氧化层,提高了栅氧可靠性,同时使得本发明的屏蔽栅功率MOS器件制造完沟槽后可直接热生长栅氧化层,省去了原有传统屏蔽栅功率MOS制造屏蔽栅和形成栅极结构的工艺

屏蔽栅功率器件的制作方法以及屏蔽栅功率器件.pdf

本申请的实施例提出了一种屏蔽栅功率器件的制作方法和屏蔽栅功率器件。制作方法的步骤包括:提供衬底,衬底的一侧形成有外延片,在外延片上形成深沟槽,其中,深沟槽包括有源区和位于有源区两端的端部;在外延片的一侧表面和深沟槽的内壁生长场氧化层,并在深沟槽内填充第一多晶硅;在场氧化层的表面和第一多晶硅上形成氮化硅,并刻蚀位于有源区的氮化硅和一部分位于深沟槽的顶部的场氧化层,以形成栅沟槽,保留位于深沟槽端部的氮化硅和场氧化层;刻蚀位于深沟槽端部的氮化硅,保留位于深沟槽端部的场氧化层。本实施例在刻蚀栅沟槽和场氧化层时,能

一种分裂栅功率MOS器件的制备方法.pdf

本发明涉及一种分裂栅功率MOS器件的制备方法,涉及半导体技术领域,包括:步骤S1,湿法刻蚀第一沟槽内的多晶硅层,形成屏蔽栅;步骤S2,沉积氮化硅层;步骤S3,干法刻蚀,保留第一沟槽内的氮化硅层;步骤S4,以氮化硅层作为自对准硬掩膜,湿法刻蚀第一沟槽内的场氧化层;步骤S5,湿法去除所有氮化硅层;步骤S6,于第一沟槽的侧壁形成栅氧化层,于屏蔽栅的上方以及两壁栅氧化层之间形成栅间氧化层;步骤S7,淀积栅多晶硅层,栅多晶硅层覆盖栅间氧化层,且与器件表面齐平,形成控制栅。本发明利用氮化硅层作为自对准硬掩膜,能够减少

一种屏蔽栅功率器件及其制备方法.pdf

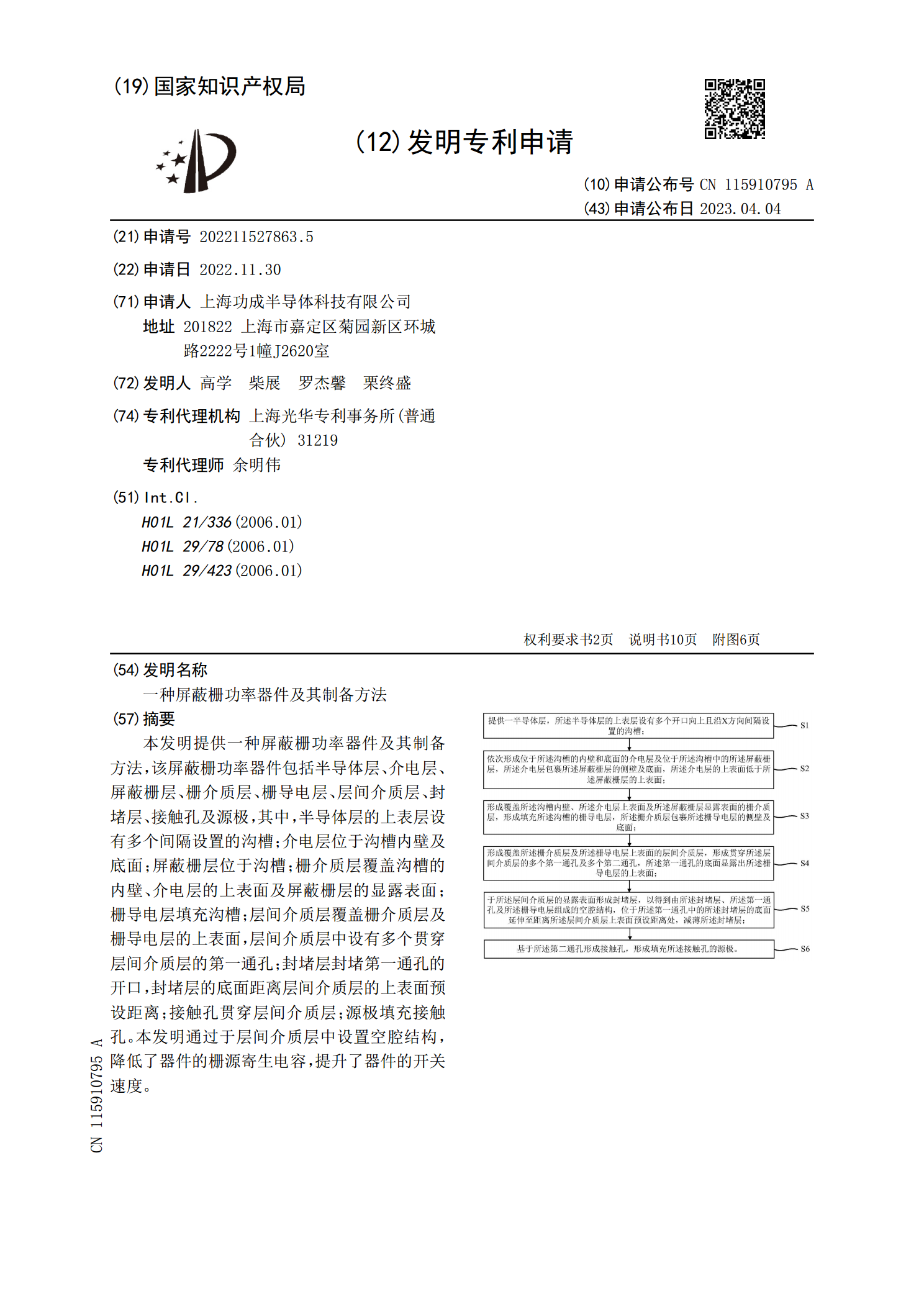

本发明提供一种屏蔽栅功率器件及其制备方法,该屏蔽栅功率器件包括半导体层、介电层、屏蔽栅层、栅介质层、栅导电层、层间介质层、封堵层、接触孔及源极,其中,半导体层的上表层设有多个间隔设置的沟槽;介电层位于沟槽内壁及底面;屏蔽栅层位于沟槽;栅介质层覆盖沟槽的内壁、介电层的上表面及屏蔽栅层的显露表面;栅导电层填充沟槽;层间介质层覆盖栅介质层及栅导电层的上表面,层间介质层中设有多个贯穿层间介质层的第一通孔;封堵层封堵第一通孔的开口,封堵层的底面距离层间介质层的上表面预设距离;接触孔贯穿层间介质层;源极填充接触孔。本

一种屏蔽栅功率器件及其制备方法.pdf

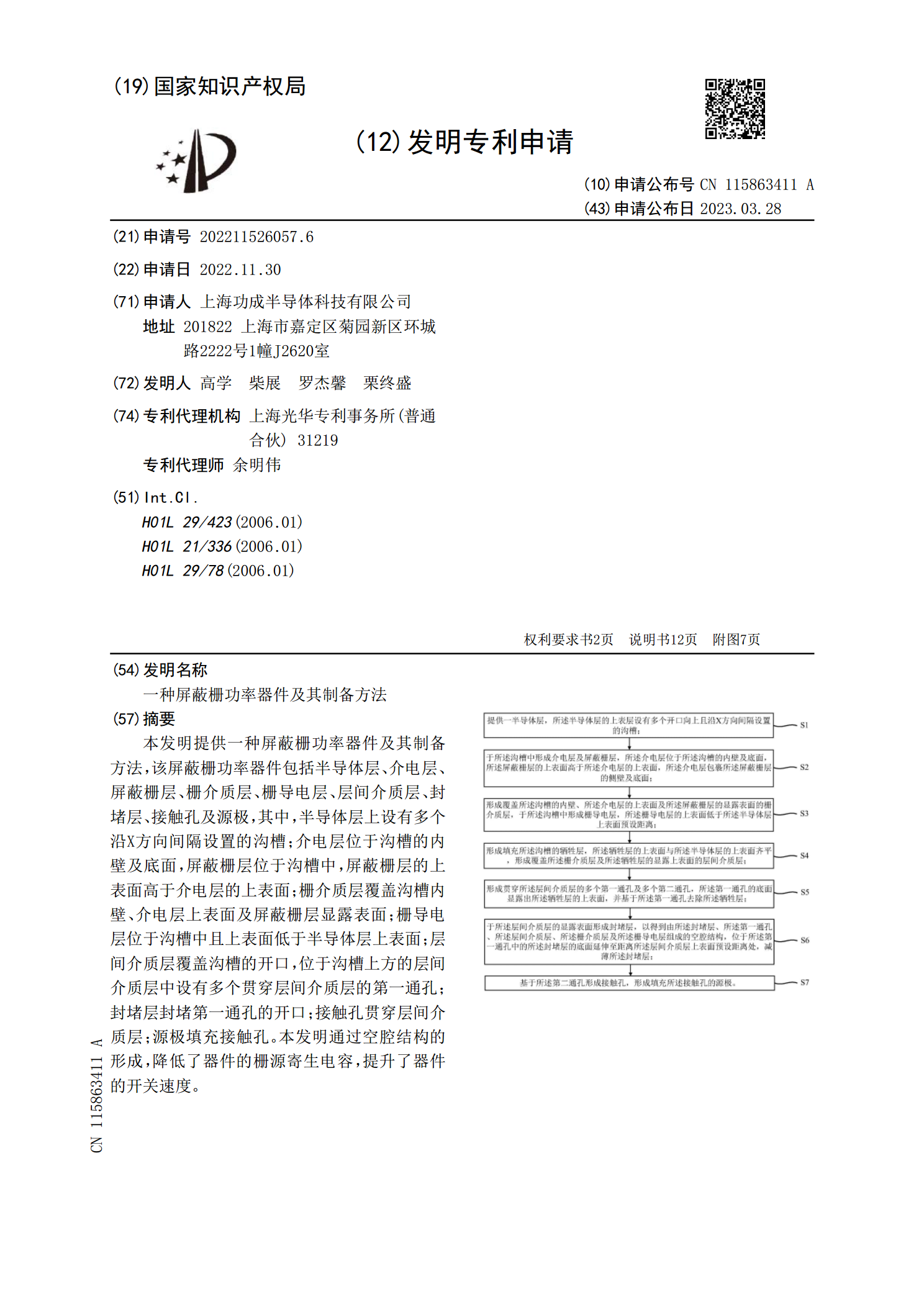

本发明提供一种屏蔽栅功率器件及其制备方法,该屏蔽栅功率器件包括半导体层、介电层、屏蔽栅层、栅介质层、栅导电层、层间介质层、封堵层、接触孔及源极,其中,半导体层上设有多个沿X方向间隔设置的沟槽;介电层位于沟槽的内壁及底面,屏蔽栅层位于沟槽中,屏蔽栅层的上表面高于介电层的上表面;栅介质层覆盖沟槽内壁、介电层上表面及屏蔽栅层显露表面;栅导电层位于沟槽中且上表面低于半导体层上表面;层间介质层覆盖沟槽的开口,位于沟槽上方的层间介质层中设有多个贯穿层间介质层的第一通孔;封堵层封堵第一通孔的开口;接触孔贯穿层间介质层;