一种分裂栅SiC垂直功率MOS器件及其制备方法.pdf

一吃****仕龙

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种分裂栅SiC垂直功率MOS器件及其制备方法.pdf

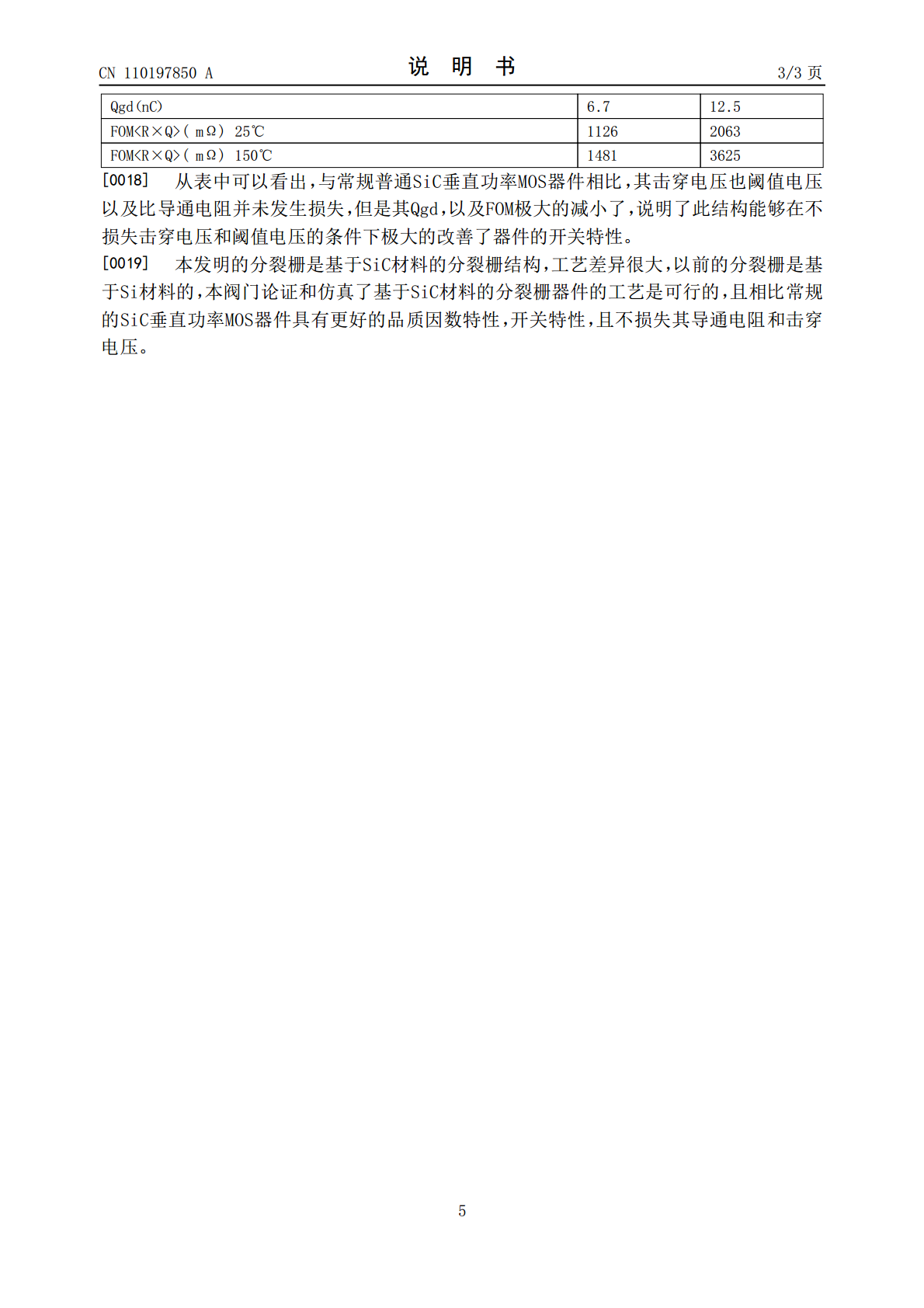

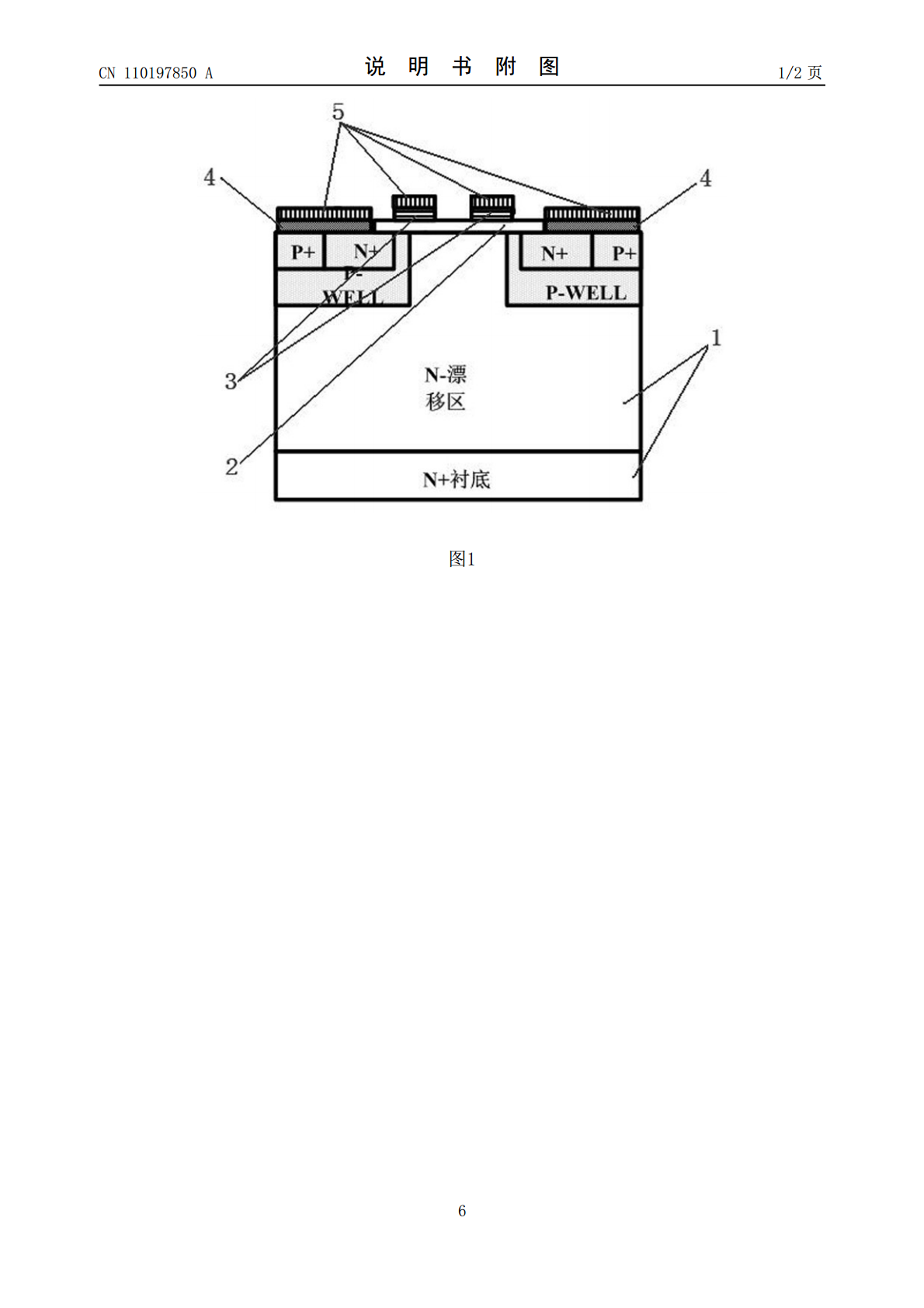

本发明公开了一种分裂栅SiC垂直功率MOS器件及其制备方法,采用新型分裂栅结构,常规沟槽VDMOS器件具有非常大的栅‑漏重叠电容。由于栅漏电荷密勒效应,当元件处于高频状态中,器件的频率响应大大降低,导致器件性能损失。要优化VDMOS在高频条件下的工作性能,分裂栅结构(Splitgate)便在此时应运而生,该结构降低了栅漏电容,改善了槽栅VDMOS的器件性能。它的导通电阻不但低于不同MOS,而且开关特性更加优秀。

一种分裂栅功率MOS器件的制备方法.pdf

本发明涉及一种分裂栅功率MOS器件的制备方法,涉及半导体技术领域,包括:步骤S1,湿法刻蚀第一沟槽内的多晶硅层,形成屏蔽栅;步骤S2,沉积氮化硅层;步骤S3,干法刻蚀,保留第一沟槽内的氮化硅层;步骤S4,以氮化硅层作为自对准硬掩膜,湿法刻蚀第一沟槽内的场氧化层;步骤S5,湿法去除所有氮化硅层;步骤S6,于第一沟槽的侧壁形成栅氧化层,于屏蔽栅的上方以及两壁栅氧化层之间形成栅间氧化层;步骤S7,淀积栅多晶硅层,栅多晶硅层覆盖栅间氧化层,且与器件表面齐平,形成控制栅。本发明利用氮化硅层作为自对准硬掩膜,能够减少

分离栅功率MOS器件及其制造方法.pdf

公开了一种分离栅功率MOS器件及其制造方法,方法包括:在衬底上形成外延层,在外延层中形成沟槽;在外延层表面和沟槽中形成第一绝缘层;在空腔中填充多晶硅并进行回蚀刻;在第一栅极导体的表面旋转涂布形成第二绝缘层;在第二绝缘层上形成掩膜,去除外延层表面和沟槽中所述掩膜侧壁的第一绝缘层,暴露沟槽的上部;在沟槽上部的侧壁和外延层的表面形成栅氧化层;在沟槽的上部中形成第二栅极导体。本申请的分离栅功率MOS器件的制造方法中,采用SOG工艺形成第二绝缘层,在回蚀刻第一绝缘层时采用掩膜保护第二绝缘层,降低了第二绝缘层厚度过厚

功率MOS器件及其制备方法.pdf

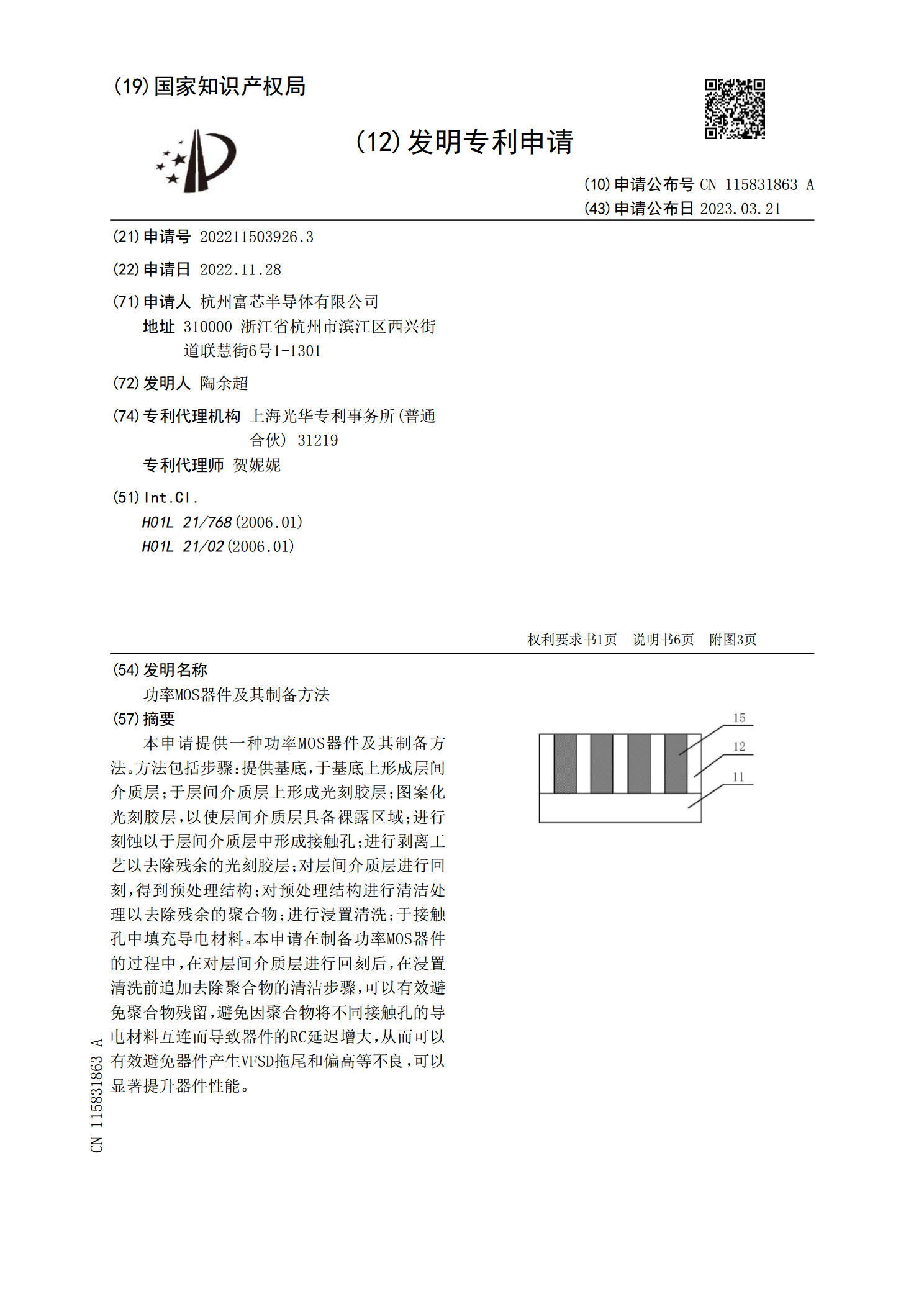

本申请提供一种功率MOS器件及其制备方法。方法包括步骤:提供基底,于基底上形成层间介质层;于层间介质层上形成光刻胶层;图案化光刻胶层,以使层间介质层具备裸露区域;进行刻蚀以于层间介质层中形成接触孔;进行剥离工艺以去除残余的光刻胶层;对层间介质层进行回刻,得到预处理结构;对预处理结构进行清洁处理以去除残余的聚合物;进行浸置清洗;于接触孔中填充导电材料。本申请在制备功率MOS器件的过程中,在对层间介质层进行回刻后,在浸置清洗前追加去除聚合物的清洁步骤,可以有效避免聚合物残留,避免因聚合物将不同接触孔的导电材料

Delta沟道掺杂SiC垂直功率MOS器件制作方法.pdf

一种Delta沟道掺杂SiC垂直功率MOS器件制作方法,其步骤依次为对N-/N+型SiC外延片表面清洗;在CVD炉中进行分层掺杂;刻出P-base区并高温Al离子注入;刻出N+掺杂源区并高温N离子注入;刻出P+接触区域并进行高温Al离子注入;在N-/N+型SiC外延片表面形成碳保护膜;高温离子注入退火;表面碳膜去除;酸清洗;SiO