具有用于线接合的局部化空腔的堆叠式半导体封装及其制造方法.pdf

mm****酱吖

亲,该文档总共19页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

具有用于线接合的局部化空腔的堆叠式半导体封装及其制造方法.pdf

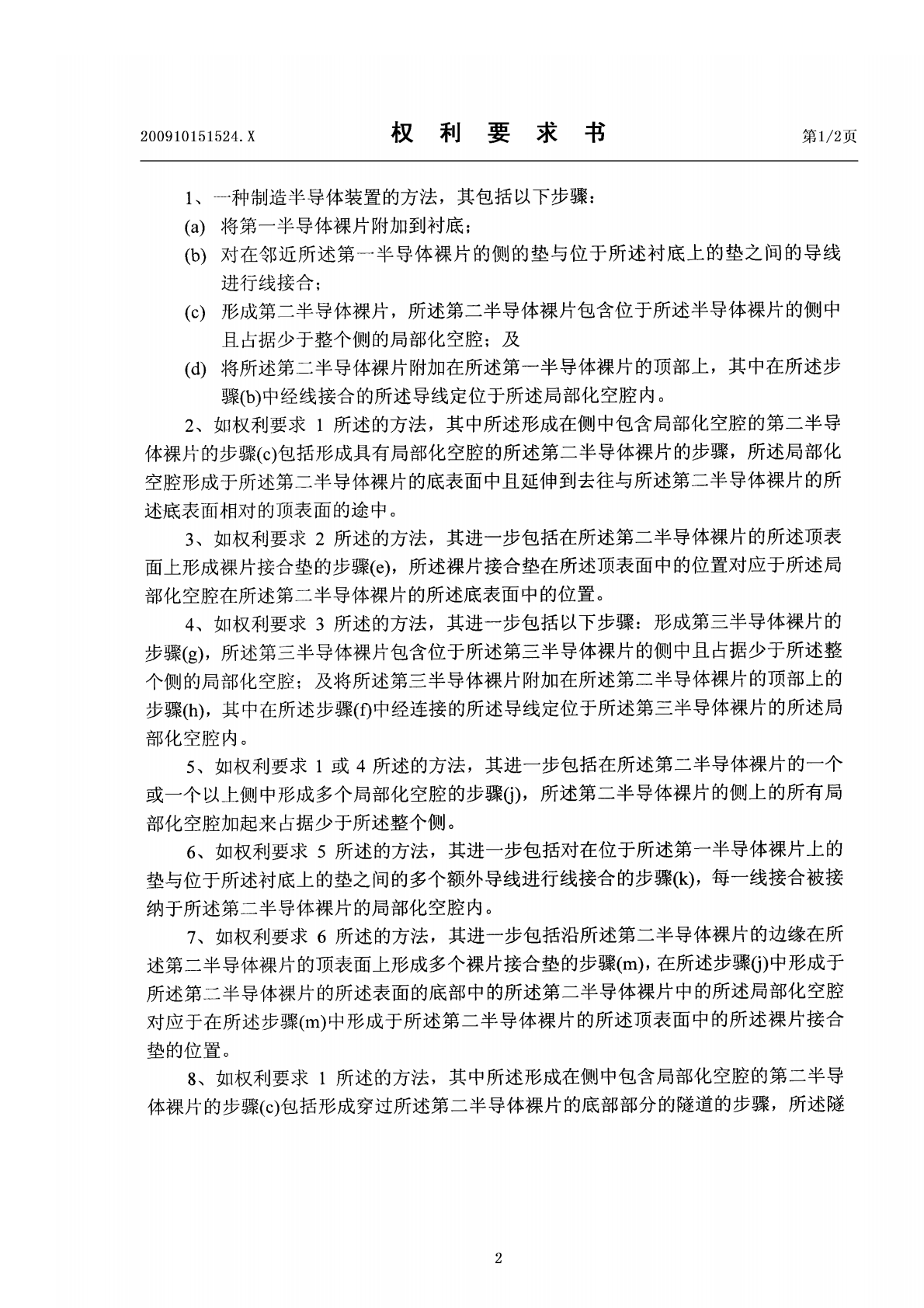

本发明揭示一种制造半导体裸片及低轮廓半导体封装的方法。所述半导体封装可包含安装到衬底的至少第一及第二堆叠式半导体裸片。可将所述第一及/或第二半导体裸片制造为具有沿所述半导体裸片的侧边缘穿过所述半导体裸片的底表面的若干局部化空腔。侧中的所述一个或一个以上局部化空腔占据少于整个侧。因此,所述局部化空腔允许半导体裸片的低高度堆叠同时为每一裸片提供高程度的结构完整性,以防止所述裸片边缘在制造期间破裂或断裂。

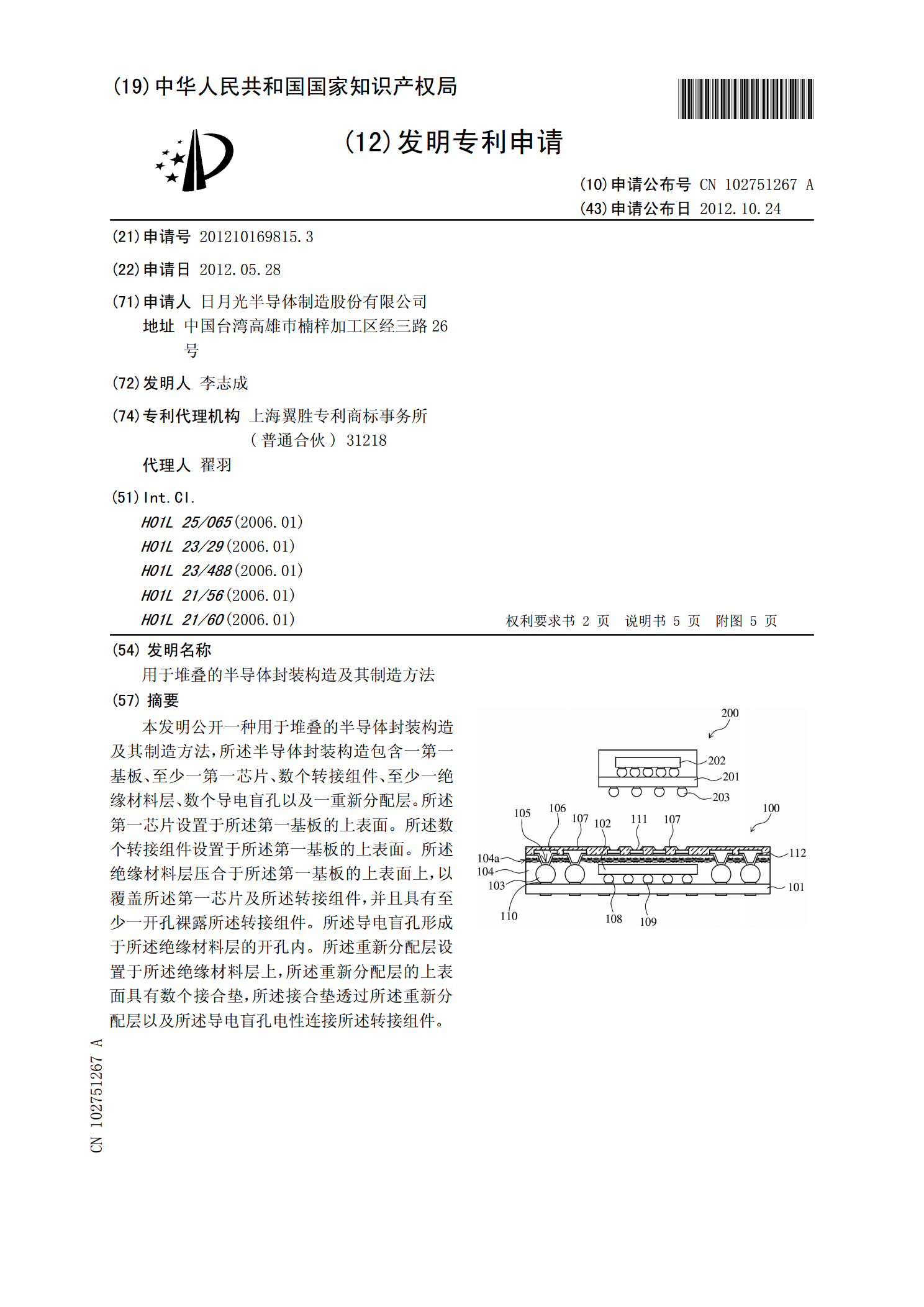

用于堆叠的半导体封装构造及其制造方法.pdf

本发明公开一种用于堆叠的半导体封装构造及其制造方法,所述半导体封装构造包含一第一基板、至少一第一芯片、数个转接组件、至少一绝缘材料层、数个导电盲孔以及一重新分配层。所述第一芯片设置于所述第一基板的上表面。所述数个转接组件设置于所述第一基板的上表面。所述绝缘材料层压合于所述第一基板的上表面上,以覆盖所述第一芯片及所述转接组件,并且具有至少一开孔裸露所述转接组件。所述导电盲孔形成于所述绝缘材料层的开孔内。所述重新分配层设置于所述绝缘材料层上,所述重新分配层的上表面具有数个接合垫,所述接合垫透过所述重新分配层以

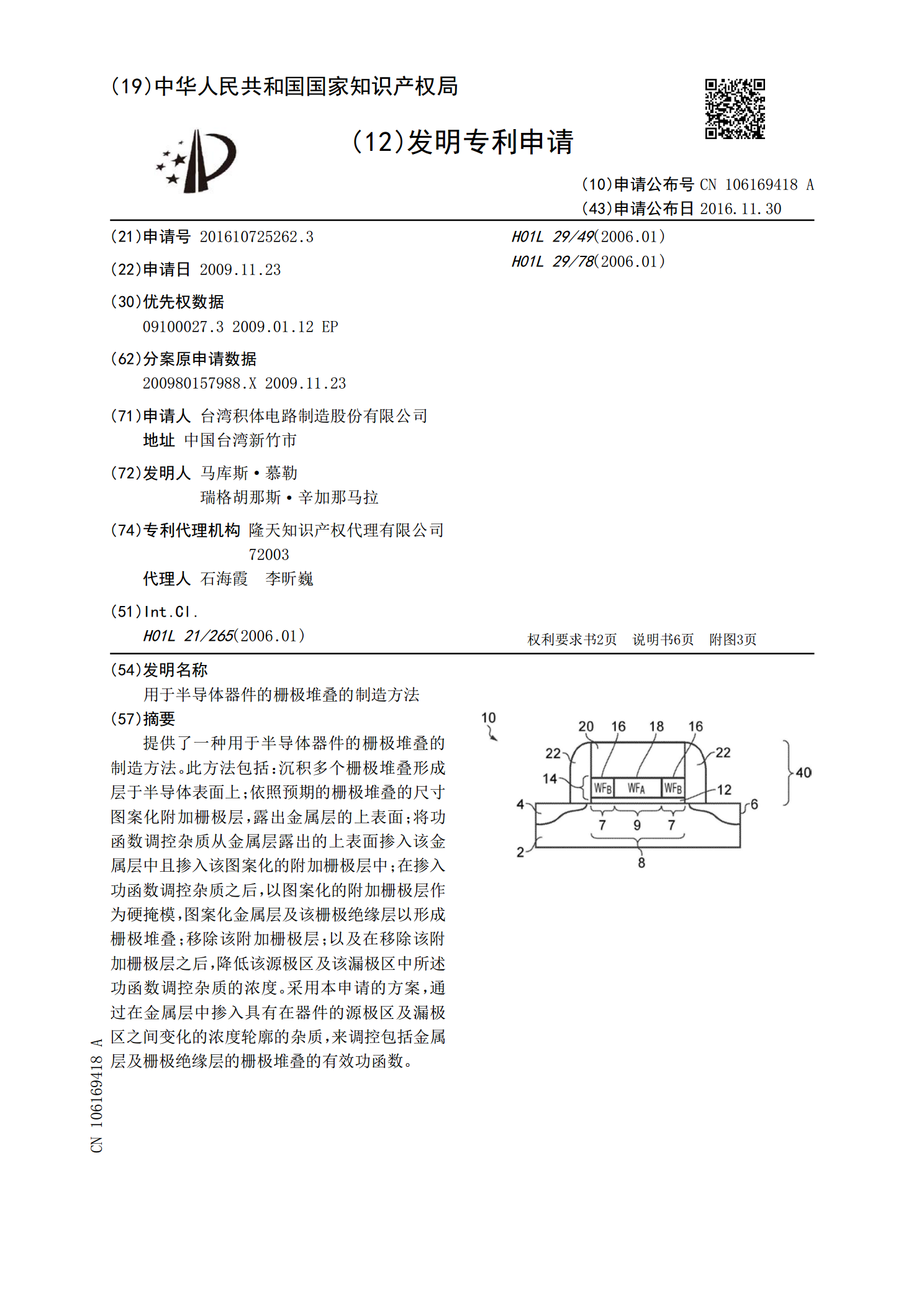

用于半导体器件的栅极堆叠的制造方法.pdf

提供了一种用于半导体器件的栅极堆叠的制造方法。此方法包括:沉积多个栅极堆叠形成层于半导体表面上;依照预期的栅极堆叠的尺寸图案化附加栅极层,露出金属层的上表面;将功函数调控杂质从金属层露出的上表面掺入该金属层中且掺入该图案化的附加栅极层中;在掺入功函数调控杂质之后,以图案化的附加栅极层作为硬掩模,图案化金属层及该栅极绝缘层以形成栅极堆叠;移除该附加栅极层;以及在移除该附加栅极层之后,降低该源极区及该漏极区中所述功函数调控杂质的浓度。采用本申请的方案,通过在金属层中掺入具有在器件的源极区及漏极区之间变化的浓度

用于制造半导体封装件的夹具和半导体封装件的制造方法.pdf

用于制造半导体封装件的夹具包括底部件和上部件。底部件包括基底、支撑板和至少一个弹性连接件。支撑板位于基底的中心区域中。至少一个弹性连接件介于支撑板和基底之间。上部件包括帽和外法兰。当上部件设置在底部件上时,帽位于支撑板上面。外法兰设置在帽的边缘处,与帽连接。当上部件设置在底部件上时,外法兰接触底部件的基底。帽包括开口,该开口是通孔。当上部件设置在底部件上时,开口的垂直投影完全落在支撑板上。本申请的实施例还涉及半导体封装件的制造方法。

一种用于半导体封装的粗铜线及其制造方法.pdf

一种用于半导体封装的粗铜线,其特征在于按重量计含有微量添加元素10‑500ppm,余量为铜;所述微量添加元素是Zn、Ca、P、Ag、Ni、Si及Sn中的一种或其中多种的组合。本发明还提供上述用于半导体封装的粗铜线的一种制造方法。本发明的粗铜线与现有的粗铝线、纯铜线相比,具有以下有益效果:(1)硬度低,焊线粘结性能优异;(2)电阻率低,导电性好;(3)强度高,延展性好,焊接稳定;(4)抗氧化性能高,具有更长的使用寿命;(5)具有稳定的可靠性能,能够增强键合工艺的可靠性,特别是对于高功率密度、高效散热的功率模