用于半导体器件的栅极堆叠的制造方法.pdf

文宣****66

亲,该文档总共12页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

用于半导体器件的栅极堆叠的制造方法.pdf

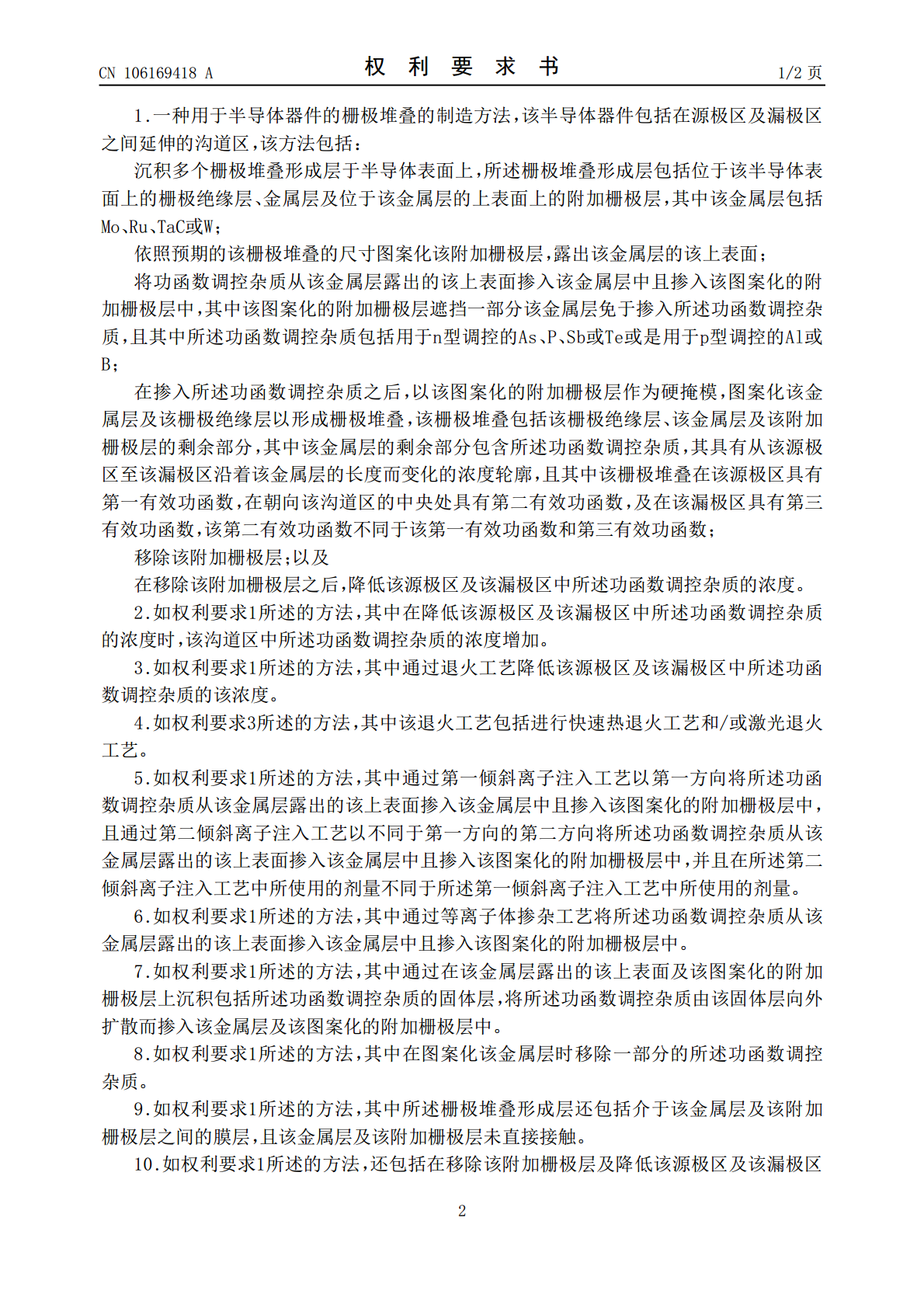

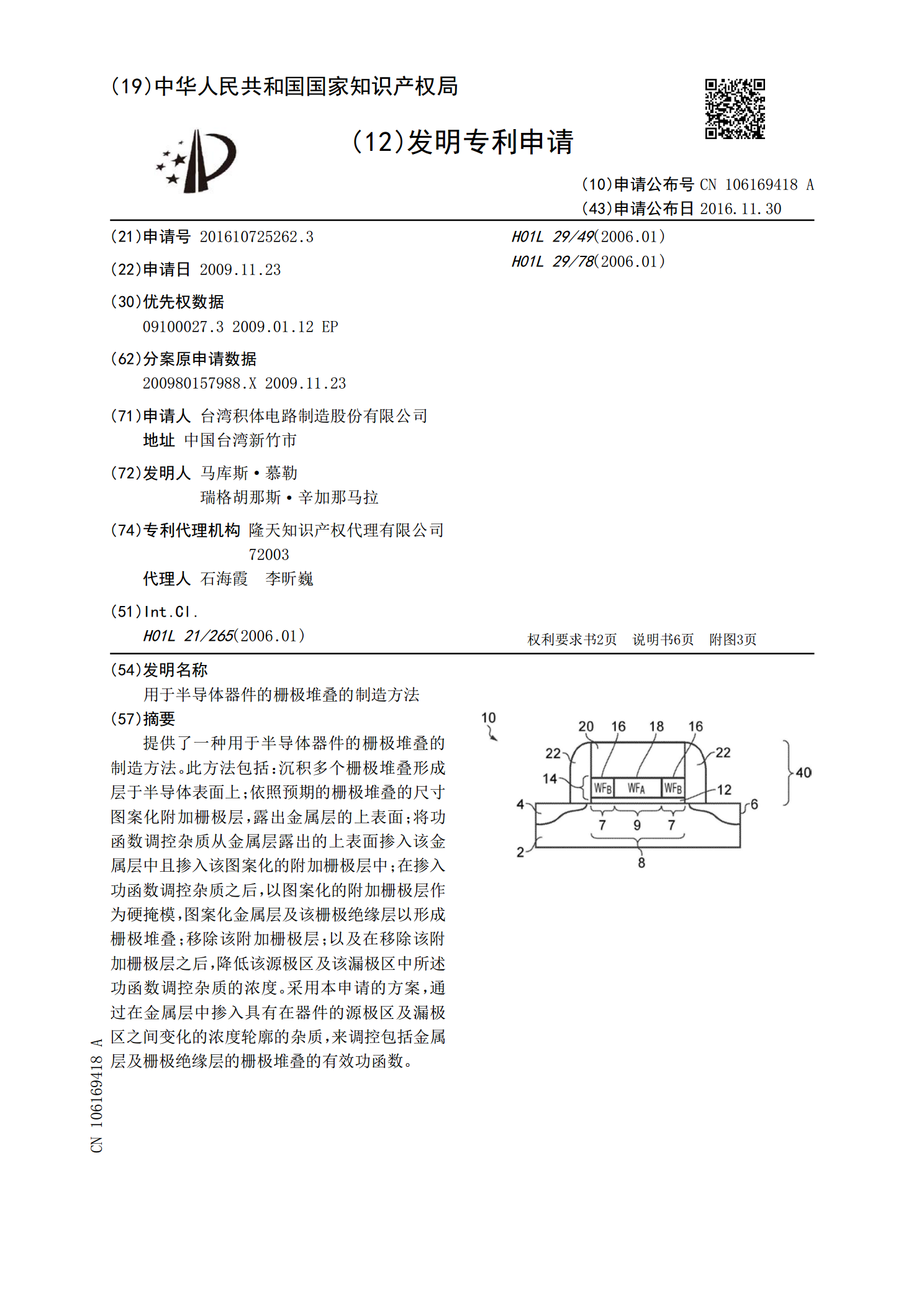

提供了一种用于半导体器件的栅极堆叠的制造方法。此方法包括:沉积多个栅极堆叠形成层于半导体表面上;依照预期的栅极堆叠的尺寸图案化附加栅极层,露出金属层的上表面;将功函数调控杂质从金属层露出的上表面掺入该金属层中且掺入该图案化的附加栅极层中;在掺入功函数调控杂质之后,以图案化的附加栅极层作为硬掩模,图案化金属层及该栅极绝缘层以形成栅极堆叠;移除该附加栅极层;以及在移除该附加栅极层之后,降低该源极区及该漏极区中所述功函数调控杂质的浓度。采用本申请的方案,通过在金属层中掺入具有在器件的源极区及漏极区之间变化的浓度

栅极堆叠的制造方法和半导体器件.pdf

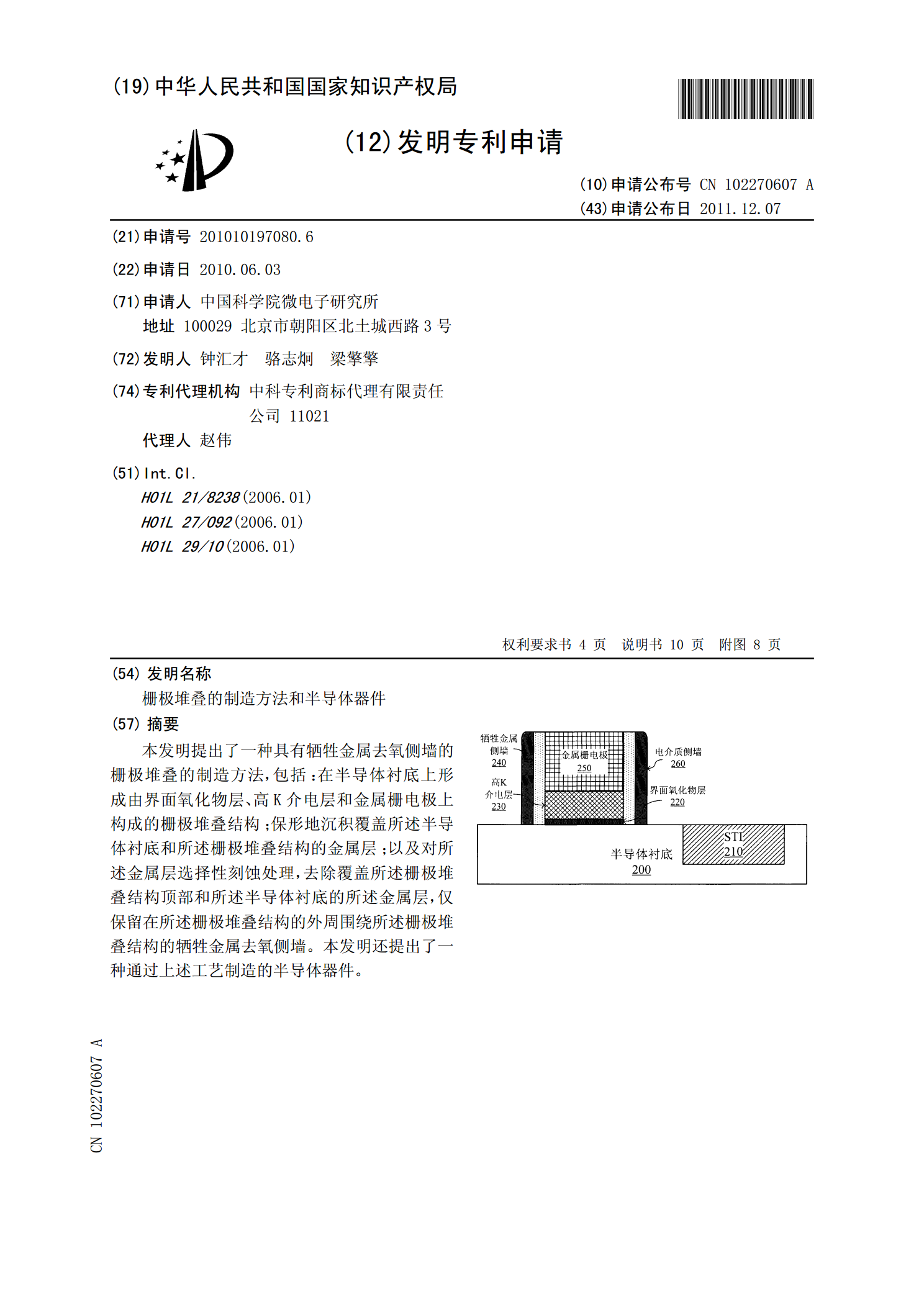

本发明提出了一种具有牺牲金属去氧侧墙的栅极堆叠的制造方法,包括:在半导体衬底上形成由界面氧化物层、高K介电层和金属栅电极上构成的栅极堆叠结构;保形地沉积覆盖所述半导体衬底和所述栅极堆叠结构的金属层;以及对所述金属层选择性刻蚀处理,去除覆盖所述栅极堆叠结构顶部和所述半导体衬底的所述金属层,仅保留在所述栅极堆叠结构的外周围绕所述栅极堆叠结构的牺牲金属去氧侧墙。本发明还提出了一种通过上述工艺制造的半导体器件。

用于形成栅极堆叠件的方法、半导体器件及其形成方法.pdf

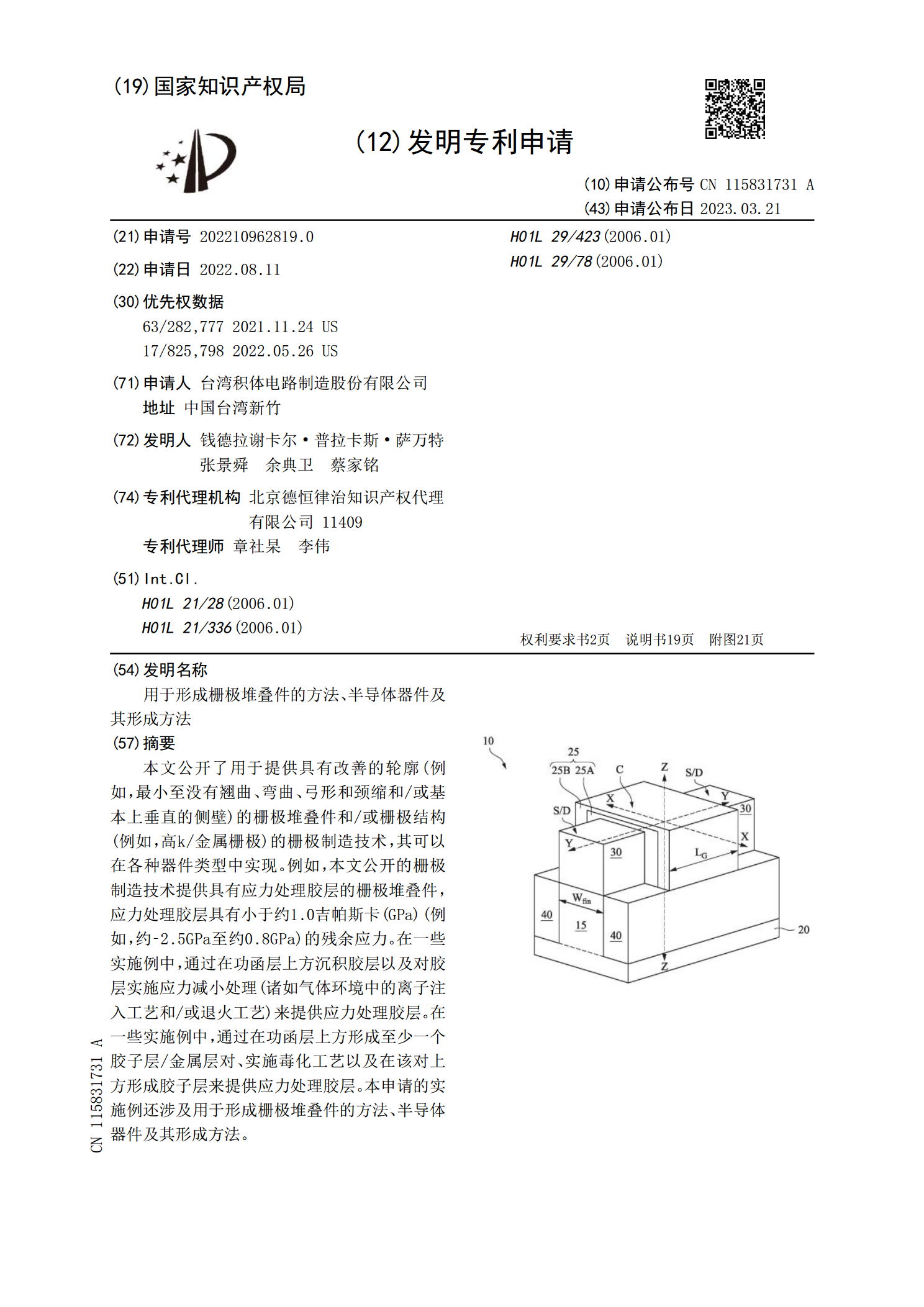

本文公开了用于提供具有改善的轮廓(例如,最小至没有翘曲、弯曲、弓形和颈缩和/或基本上垂直的侧壁)的栅极堆叠件和/或栅极结构(例如,高k/金属栅极)的栅极制造技术,其可以在各种器件类型中实现。例如,本文公开的栅极制造技术提供具有应力处理胶层的栅极堆叠件,应力处理胶层具有小于约1.0吉帕斯卡(GPa)(例如,约‑2.5GPa至约0.8GPa)的残余应力。在一些实施例中,通过在功函层上方沉积胶层以及对胶层实施应力减小处理(诸如气体环境中的离子注入工艺和/或退火工艺)来提供应力处理胶层。在一些实施例中,通过在功函

栅极沟槽以及半导体器件的制造方法.pdf

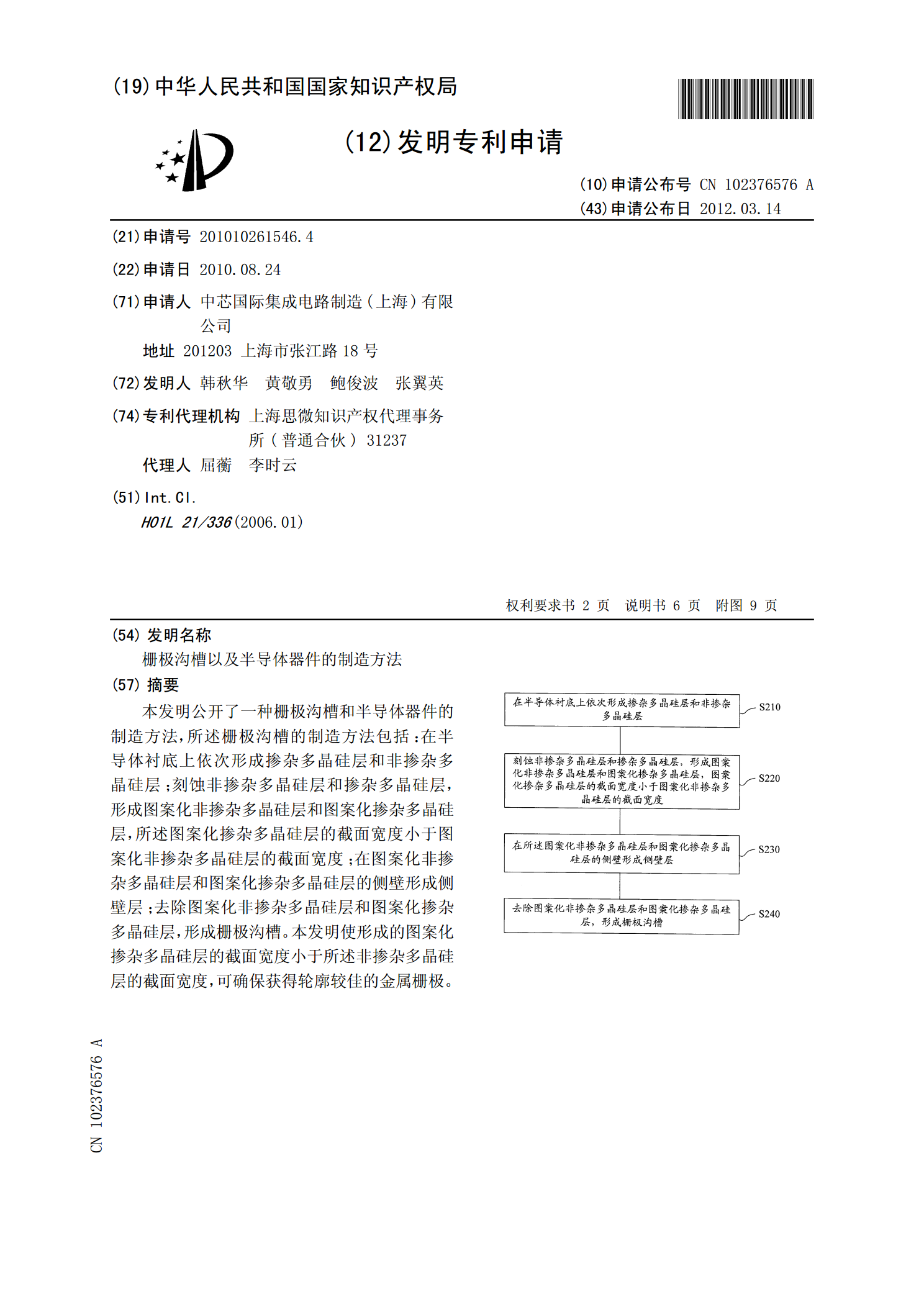

本发明公开了一种栅极沟槽和半导体器件的制造方法,所述栅极沟槽的制造方法包括:在半导体衬底上依次形成掺杂多晶硅层和非掺杂多晶硅层;刻蚀非掺杂多晶硅层和掺杂多晶硅层,形成图案化非掺杂多晶硅层和图案化掺杂多晶硅层,所述图案化掺杂多晶硅层的截面宽度小于图案化非掺杂多晶硅层的截面宽度;在图案化非掺杂多晶硅层和图案化掺杂多晶硅层的侧壁形成侧壁层;去除图案化非掺杂多晶硅层和图案化掺杂多晶硅层,形成栅极沟槽。本发明使形成的图案化掺杂多晶硅层的截面宽度小于所述非掺杂多晶硅层的截面宽度,可确保获得轮廓较佳的金属栅极。

金属栅极及半导体器件的制造方法.pdf

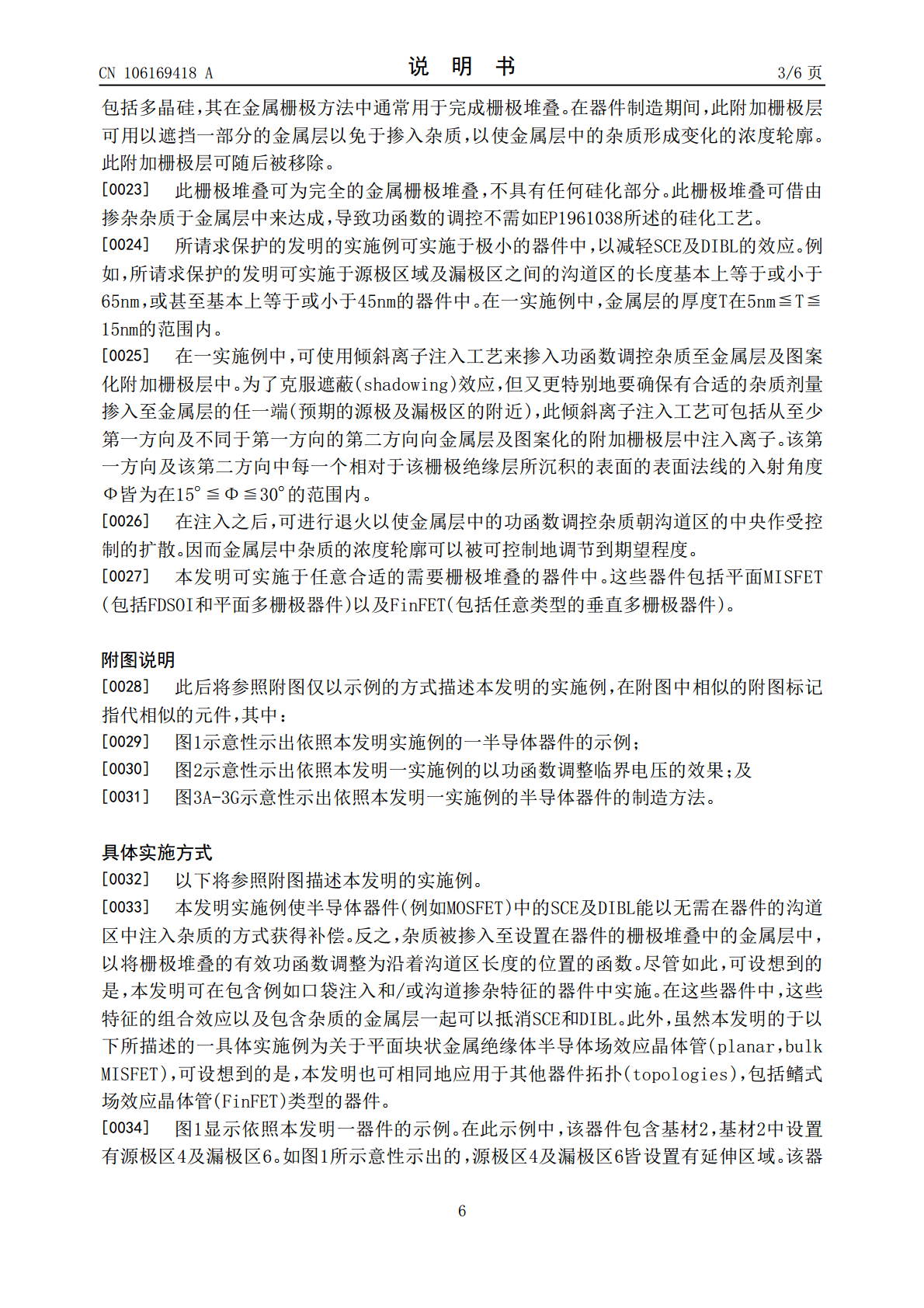

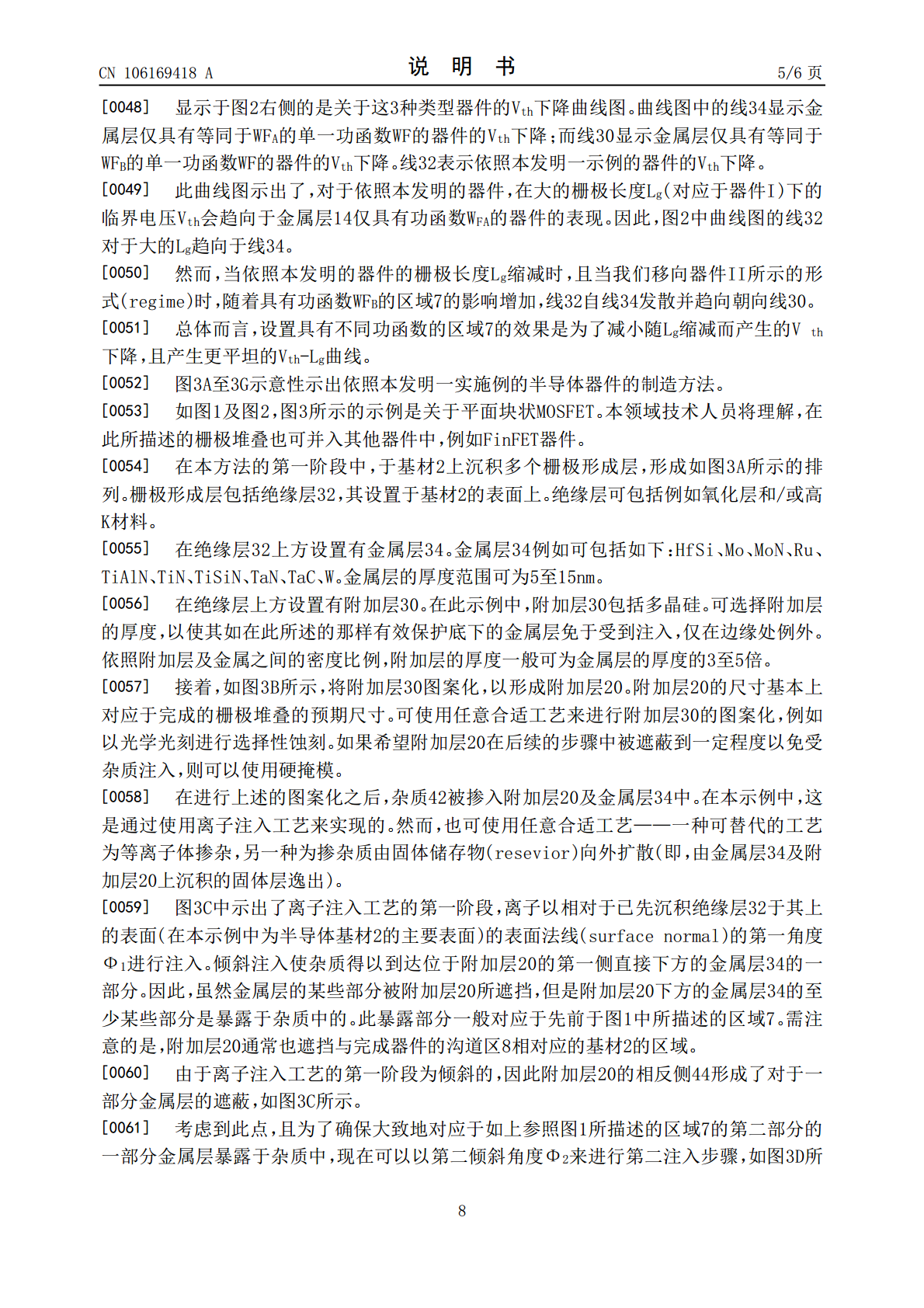

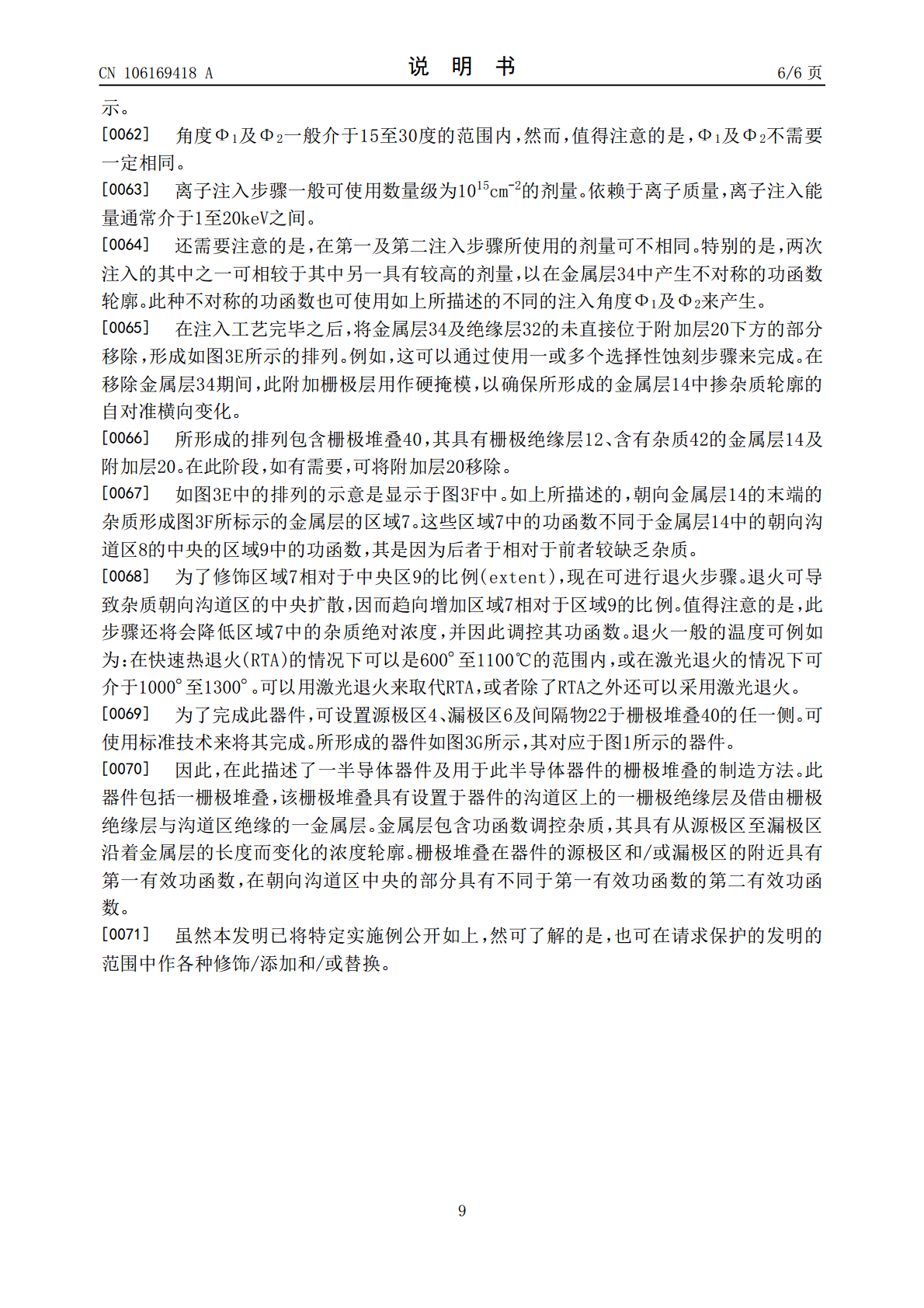

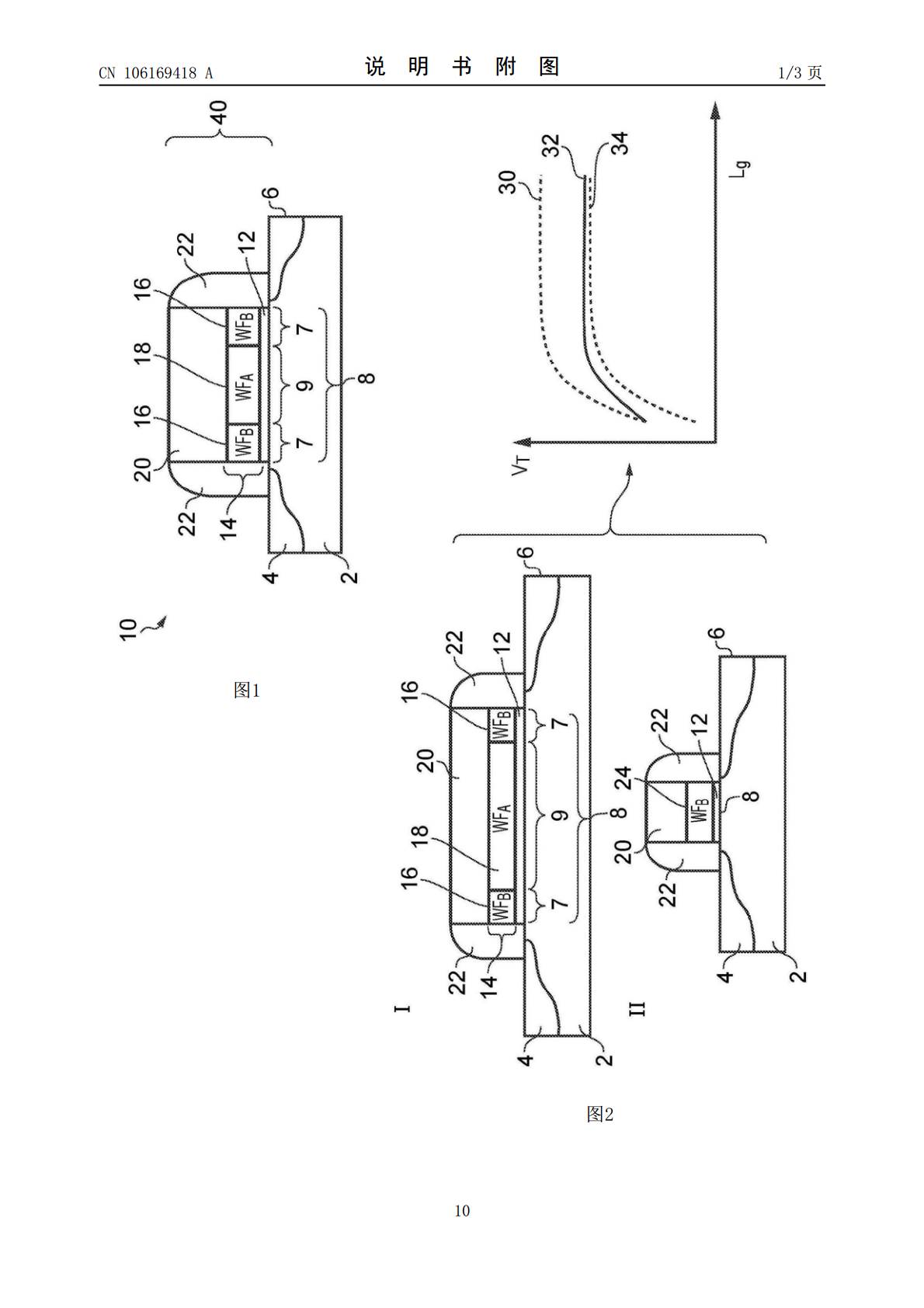

本发明提供一种金属栅极及半导体器件的制造方法,通过原子层沉积工艺在金属导电层和底部抗反射层之间上形成氧化物隔离层,可以在去除图形化的光刻胶层和底部抗反射层的过程中,通过较高的刻蚀选择比来保证所述图形化的光刻胶层和底部抗反射层的去除效果,不会产生严重的光刻胶等刻蚀残留,同时可以阻挡该过程中的氢离子向下方的金属导电层和高K介质层中扩散,大大减少了形成的金属栅极结构内部的损伤和缺陷,改善器件的偏压温度不稳定性,提高器件的可靠性。